调了很久发现uboot 2014.1从2410移植到2440总也开不起来,似乎总是程序跑偏,hang在了时钟设置的地方,所以有必要仔细读一读时钟和电源管理的部分章节。

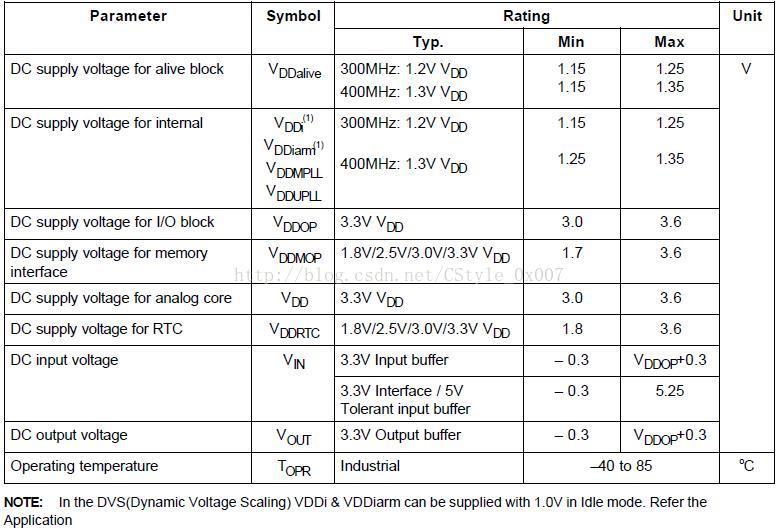

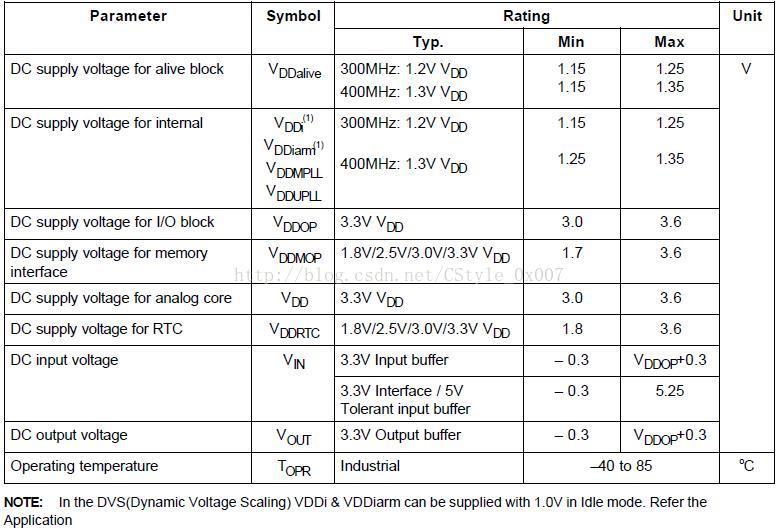

先说下硬件配置,12MHz晶振,前面提到我们的SDRAM(EM48AM1684VTE-6F)支持最大是166MHz @CL3,cpu最大支持工作频率400Mhz @ 1.3V/ 300MHz@1.20V ,但是我们的板子现在的电源设计由于无良厂商削减成本就设计了两种电压使用LDO来达到1.25V/3.3V所以参考下面的这幅图,可以看出我们的板子跑300Mhz应该是没什么问题,但是跑400Mhz估计够呛,别人参考的跑400Mhz的电压是1.3V,而我们的却是1.25V,勉强支持,但是稳定性难说,先让机器开起来,之后有时间在来逐个验证。

支持的PLL,两个:On-chip MPLL and UPLL,支持slow clocks without PLL and connect/disconnect the clock来降低功耗:

UPLL:

UPLL generates the clock to operate USB Host/Device. USB block (48Mhz).

MPLL :

MPLL generates the clock to operate MCU at maximum 400Mhz @ 1.3V.

Fclk Up to 400MHz /Hclk Up to 136MHz /Pclk Up to 68MHz

FCLK ->CPU core(ARM920T)

HCLK ->AHB bus peripherals.as memory controller, the interrupt controller, the LCD controller, the DMA and USB host block

PCLK -> APB bus peripherals.as WDT, IIS, I2C, PWM timer, MMC interface, ADC, UART, GPIO, RTC and SPI.

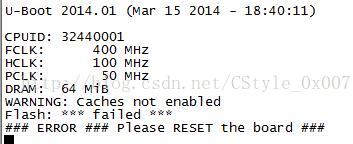

所以我们准备设置CPU工作在400Mhz,采取FCLK:HCLK:PCLK =1:4:8,刚好是:400Mhz:100Mhz:50Mhz,符合cpu的PLL的最高频率要求,所以我们的任务就是围绕这个展开。

电源管理Power management:

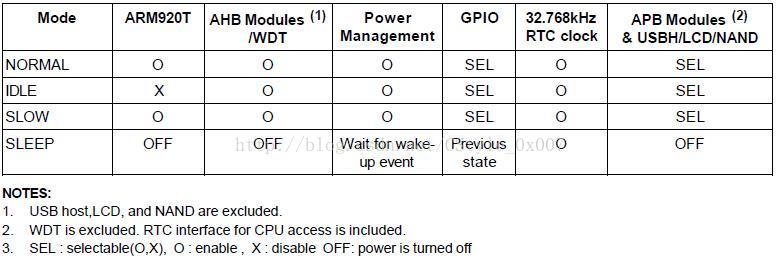

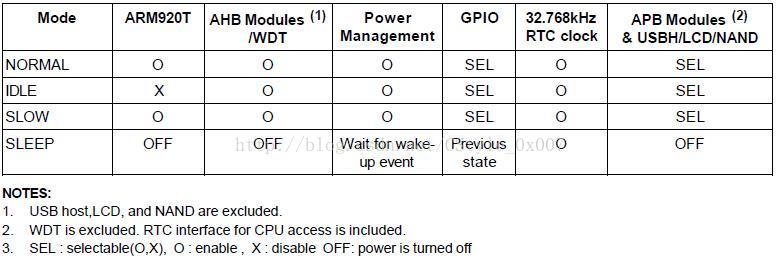

支持四种模式:NORMAL mode, SLOW mode, IDLE mode, and SLEEP mode

NORMAL mode:正常工作模式,默认外设都是打开的,功耗最高,可以使用CLKCON register来打开或者关闭某个外设的时钟

SLOW mode: Non-PLL mode,也就是关闭PLL,使用外部输入时钟,这里我们的是12Mhz

IDLE mode:关闭cpu的时钟,但是保持其他的外设的时钟正常(也可以关闭部分外设),cpu能被外设的中端唤醒。

SLEEP mode:internal power被关闭,保持唤醒的部分电源打开,可以通过EINT[15:0] or RTC alarm interrupt唤醒,需要设计两套电源供电PWREN引脚可以用来切换电源,但是我的板子上只使用了一路

MAX8860EUA18从3.3V转1.25V供电,应该是不支持S3的功能的,具体可能还要测试之后才知道。

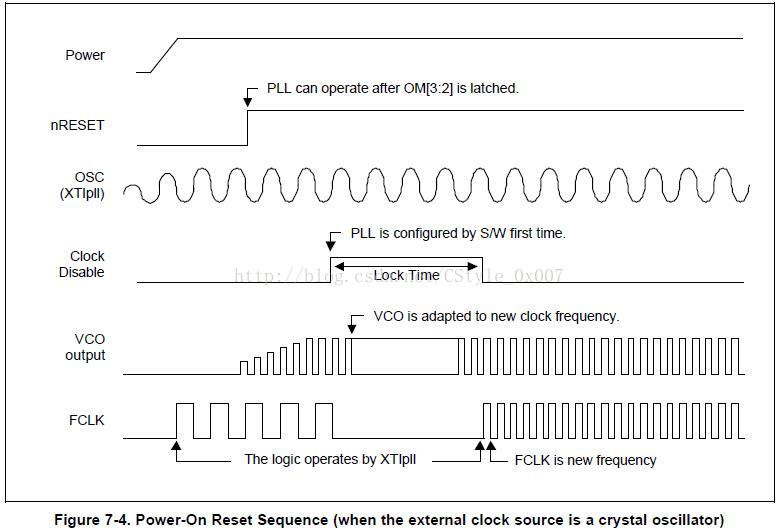

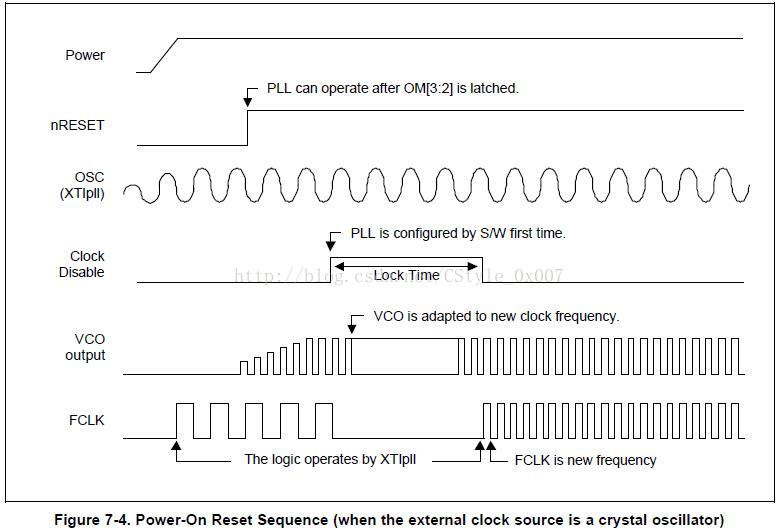

MPLL和UPLL可以选择使用外部晶振或者外部输入,使用 OM[3:2]来选择,我们的板子上选择是是使用12Mhz的晶振,同时需要注意的是,MPLL系统时钟是在reboot的时候生效,但是默认的情况下它的PLL产生的时钟是不会被用于MPLL的各种时钟输出,必须先写一次MPLLCON register才会生效。

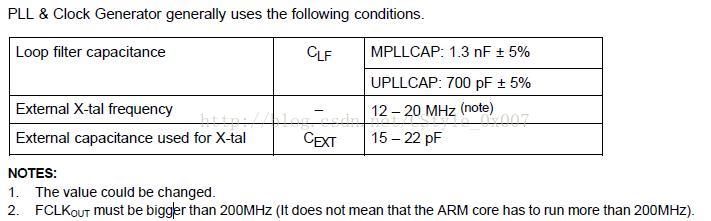

锁相环时钟计算,以及晶振频率选择:

MPLL Control Register

Mpll = (2 * m * Fin) / (p * 2S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

UPLL Control Register

Upll = (m * Fin) / (p * 2S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

PLL Value Selection Guide (MPLLCON)

1. FOUT = 2 * m * Fin / (p*2S), FVCO = 2 * m * Fin / p where: m=MDIV+8, p=PDIV+2, s=SDIV

2. 600MHz < FVCO < 1.2GHz

3. 200MHz < FCLKOUT< 600MHz

4. Don't set the P or M value as zero, that is, setting the P=000000, M=00000000 can cause malfunction of the PLL.

5. The proper range of P and 1 <P < 62, 1 < M < 248

6

.When you set MPLL&UPLL values, you have to set the UPLL value first and then the MPLL value. (Needs intervals approximately 7 NOP).(陷阱之一)

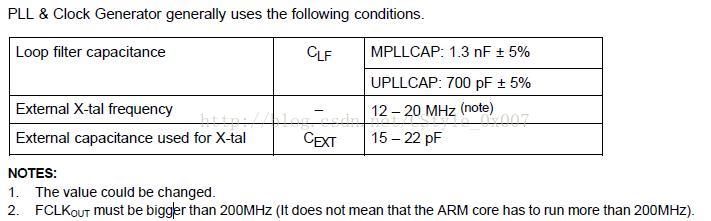

从下面两张图可以看出,我们对晶振的选用要求,以及loop filter cap大小精度要求,以及在系统reset的时候系统时钟自动设置的时序,我们还需要注意的是,FCLK在用户没有设置PLLCON寄存器之前是不会使用MPLL的输出的,而是直接使用Fin也就是12Mhz。同理PLL (UPLL)也需要事先设置,USB所需要的48Mhz时钟才会生效。

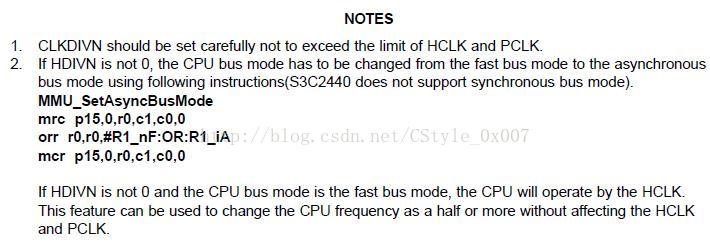

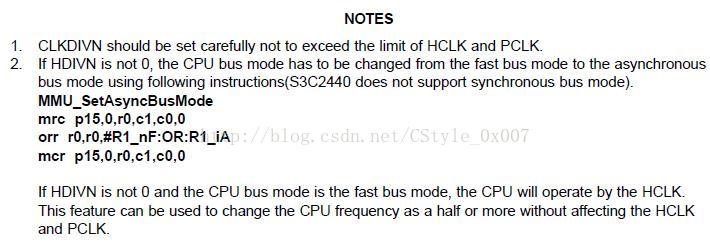

一个来自于vendor的重要注释,当我们选择我们的时钟配置的时候,需要谨慎的去注意这部分,这里说的是ARM core的时钟是选择使用FCLK还是HCLK的问题,涉及到cpu bus mode的切换:

除了上面提到的时钟的切换之外,我们还需要注意的一个东西就是关于各种cpu工作的ACPI状态,以及他们之前的切换方式,切换之前需要设置哪些寄存器,保存哪些信息,比如:

如何设置数据总线的状态,sdram如何进入自刷新模式,GPIO的状态,usb的状态,唤醒源的设置 ,adc的设置,支持ACPI的硬件电源设计等等,暂时先放一放,等玩到电源管理的部分的时候再去研究它,这部分就先到这里。

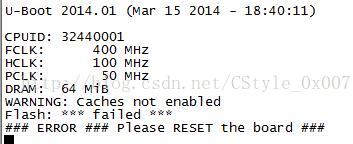

最后上一张图,这个可是我辛辛苦苦了很久才调试出来的,看起来时钟部分设置以及ok了,至少是系统能动起来了,对于高手来说这可能不算什么,但是对于菜鸟来说也算是一项莫大挑战,欣慰的是i made it,系统跑起来了,板子上用来调试的四个LED灯也正常的点亮,嘚瑟一下。

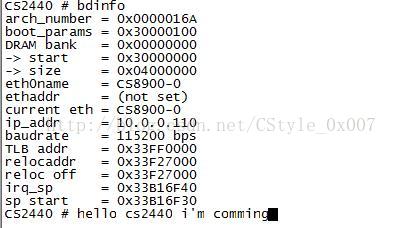

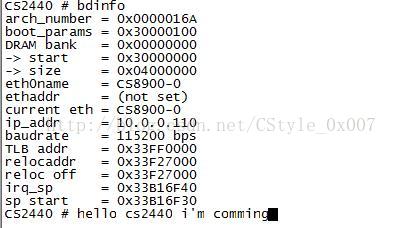

看下半成品,可以boot到uboot的shell环境下了,这里面的故事比较复杂一点,还有修改过amd_flash_info这个结构:

4764

4764

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?