翻译前:

这个是网上找ZIGBEE开源协议栈masstatePAN的文档。一看是英文的。就但算翻译一下,作为以后的参考。

看了下摘要好像和ZIGBEE没什么关系??难道是我看错了?

第一次接触协议栈,术语可能有些不太对,英语水平不算好,请见谅。

内容比较多,有时间更,顺便外包一段,格式就先不整了。

下面是翻译正文:

下次附上原文的链接:

Finite State Machine

Datapath Design, Optimization,

and Implementation

————————————————

摘要:

状态机数据通路设计,最优化选择,解决方案这书是为了探讨设置空间组合状态机/数据通路解决方案。本篇从检测像存在时钟信号不稳定所影响时序的建立和保持的影响因素的数字系统中的执行问题出发,使用流水线拉力增加系统时钟频率。随后是定义潜在因素和吞吐量,通过使用数据流程图和调度表来实现的数字信号处理的应用的例子来详细讨论相关资源的权衡问题。此外,设计还和设计功能,界面,性能在ASIC,FPGA像FIFO,单端接口,双端接口有共同点的不同类型的存储器有关。选择的设计实例在implementation-neutral Verilog代码和块图中执行,相关设计文件可以从Altera Quartus and Xilinx Virtex FPGA平台上下载。需要有Verilog,组合逻辑电路和基础数字信号设计技术相关知识作为支持。本篇适合作为名为介绍逻辑组合在Verilog HDL的应用的查询手册。

关键字:

Verilog, datapath, scheduling, latency, throughput, timing, pipelining, memories, FPGA, flowgraph

————————————————————————————————

目录

章节1——计算最大时钟频率

章节2——提升设计性能

章节3——带有数据通道的有限状态机(FSMD)的设计

章节4——嵌入式显存使用量在带有数据通道的有限状态机(FSMD)的设计

————————————————————————————————————

章节1

计算最大时钟频率

本章目的在于找到最大时钟频率并调整基于组合门电路的传输延时的时序的保持和建立。本章假设读者非常熟悉数字梦电路和像锁存器和触发器之类的存储单元。

1.1 学习目标

在阅读这一章节后,你将可以做以下测试:

- 找到通过电路的最长组合延时路径

- 在时序电路计算3种类型的延时

- 计算片级基于内部寄存器组的时序的建立和保持。

- 计算板级时钟频率

1.2 门电路传输延时

最简单的数字器件的性能的度量是计算时间。通常这种方法用于精确每一秒的计算结果,并且取决于不同类型的计算过程。对于通用处理器来说,这可能是需要精确到数百万分之一秒的指令周期(MIPS)。对于算术处理器,可能要精确到数百万分之一秒的浮点运算数(MFLOPS)。计算时间是部分取决于时钟的速度,部分取决于时钟每操作的数量。本章将关注计算最大时钟速度去启用最小计算时间。

数字逻辑门电路是建立在晶体管的特殊排列来表现出的一种数学上的操作。这些晶体管被操作表现为开/关的转换器。理想情况的晶体管能瞬时转换从开到关或者从关到开;然而实际的的晶体管存在着有限度的开关延时。一个在晶体管转换时间中的首要的因素是他们的物理尺寸。越小的晶体管通常转换的比大的晶体管要快。随着晶体管的尺寸通过新兴科技的的进一步微小化,这种延时在不断的被减小。现在的晶体管的转换特别的快,但是延时还是一定存在的。

具体类型的晶体管在逻辑门电路中没有它们达到的功能重要。这种开关的延时会产生在逻辑门上的延时。这种延时被精确地从时间输入的改变到时间输出的改变。这个延时被称为传输延时(tpd)。本书将考虑和这种延时相关的门,还要理解基本的晶体管的定义。

1.2.1 单输入/多输入延时

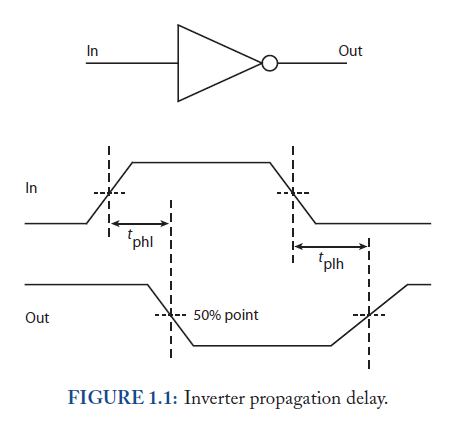

被讨论的最简单的门电路tpd是反相器。反相器具有一个输入和一个输出,当输入一个逻辑高,则输出一个逻辑低。当输入产生从逻辑高到逻辑低的改变时,输出将会在逻辑上有从低到高的改变或反之也一样。这些有限的上升时间和下降时间被展示在图1.1中。50%的上升和下降时间点是当电平在逻辑高和逻辑低的重点的点。tpd被用于测量输入50%的上升时间和输出50%的下落时间。

tpd能区别于输出上升时间和下落时间。如果上升沿时间比下降沿时间长,那么50%点就会偏移,导致结果产生一个比tpd更大的值。一旦传输延时改变,则意味着全部改变。当输出改变从高到低,延时就和它所指的tphl有关。当输出被改变从低到高,则延时和它所指的tplh有关。简单的说,最差的情况发生了两个传输延时,并且被认为成整个门电路的时间tpd。

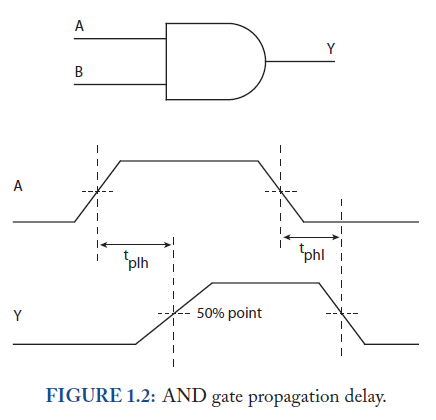

尽管每种逻辑门的类型的构造不同,但是延时始终贯穿着门电路计算测量。多路输入门有更多传输延时。比如,一个与门(AND)有至少2个输入,如图1.2所示。tpd需要衡量从低到高和从高到低的每个输入。

对于2个输入的门,存在是个延时A2Y tplh, A2Y tphl, B2Y tplh,A2Y tphl.

简单的说,最坏的情况是在四个传输延时发生并且被认为是整个门(Y tpd).的总共延时tpd。这使用于任意数量输入的组合门电路。典型的,逻辑器件的技术文档包括了最坏情况tpd和典型的tpd取值。

1.2.2 传输延时效应

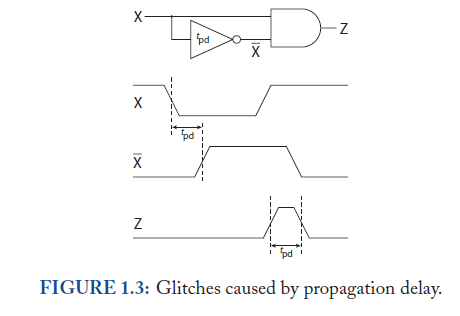

当多个门被连接到一起,在单独的门电路产生多余且不正确的输出结果的传输延时被称为故障(glitches)。故障会造成输出值在逻辑上不是理想的逻辑门电路。比如,一个与门当所有输入都为逻辑高时仅仅输出一个逻辑高。当与门的输入总是和图1.3相反,那么输出将永远不会置高。如果反相器有一个有限tpd,那么与门的输出在信号传输通过反相器是将变成逻辑高。当输入转换为高电平,所有的与门输入都是逻辑上高,因为改变结果不会通过反相器进行传播。

由于传输延时,无论何时多路门被组合使用,输出都会可能出现故障,直到所有的信号全部传输通过门电路,输出在这种经过这段延时前不能被认为有效。这就是为什么数字系统通常使用时钟。时钟信号的上升沿表示当所有输入信号已经被发送到电路中。如果时钟周期产生正确,直到下一个上升沿到来,故障结束并且输出则被认为是有效的。时钟周期的产生是分析电路中所有的传播延时得到的。

1.2.3 计算最长的延时路径

电路的tpd是用来描述通过追踪一个输入到输出。每个门的传播延时被叠加到通路的总延时上。这个步骤被重复用于单个输入到输出的每个路径。在确定一系列的延时综合后,电路Tpd被用来决定最大延时时间的建立。

1.2.4 例子1.1

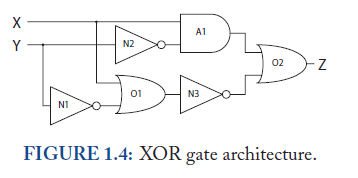

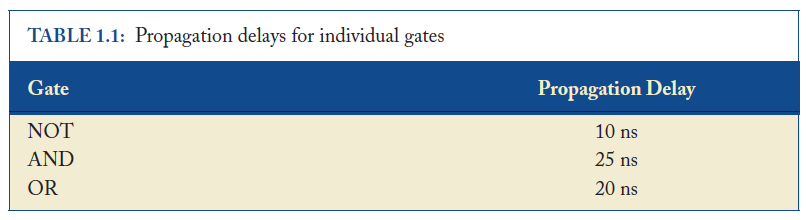

一个异或门电路是有与,或,非门构成,具体见图1.4。使用图1.4的电路,与或非们的延时被列在表1.1中,那么整个电路的最差值tpd是多少?

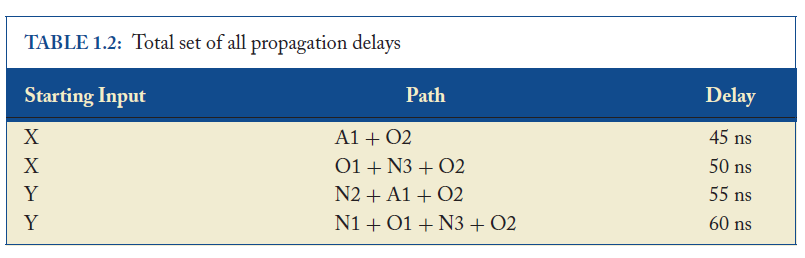

对于一个异或门来说,这里有4个从输入到输出的独立路径。第一条路径开始在X输入,并且经过A1与门的处理和O2或门,总共的延时时间是25+20=45ns。第二条路径从X开始输入,通过O1或门,N3非门和O2或门的处理,有20+10+20=50ns的延时。

Y的输入路径也有两条。第一条通过N2非门,A1与门和O2或门用时10+25+20=55ns的延时。最后一条的路径通过N1非门,O1或门和N3非门和O2或门,用时10+20+10+20=60ns延时。所有路径列在表1.2中。

最坏的延时路径是60ns。在技术文档中,最大Tpd将被列为60ns。如果这个异或电路用于实际电路,这个延时同样是最小时钟周期。

1.3 触发器延时

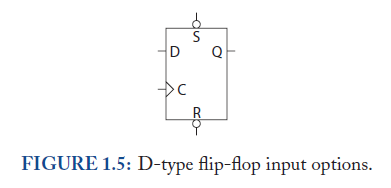

触发和锁存器被认为是存储单元,因为他们能在没有输入的情况下输出一个有效值。该值可以按需被改变。当器件被使用时,输入被转化为输出。在本书中,触发器将被定义为使能(通常是一个时钟)于一个边沿触发信号。对于锁存器,使能信号是一个灵敏级别的信号。本书在例子中使用触发器,因为这是最通用的设计类型。虽然存在很多类型的触发器想SR触发器,D触发器,T触发器,JK触发器,本书只讨论D触发器因为他们是最简单和直接的触发器。另一种类型的触发器被用作分析D触发器在同样的技术下的运用。在D触发器中,在时钟信号边沿时输入被复制到输出。D触发器能有多种输入选择如图1.5所示。

一种特殊类型的触发器被称为寄存器。寄存器有一个使能输入,能防止后者在每个时钟周期被转化到输出。当使能端设置为高时,输入将被复制。寄存器可以成组进入,每个都有相同的控制信号。但是有不同的数据输入和输出。有时寄存器这个词又被用作触发器的同义词。

存储单元的输出有一个像组合门电路的Tpd值。然而,它的计算方式不同。

因为寄存器的输出仅仅在一个时钟转换的时间里改变,Tpd的测量值来自于时钟在时间从输入到拷贝到输出端的改变。当数据输入的变化时,输出不变,tpd不是从输入到输出的测量结果。然而,时钟输出延时(tC2Q)不是关系到寄存器延时的唯一延时。

1.3.1 异步延时

在不同类的寄存器中其他输入为有效的。一些寄存器在独立输入的情况下可以置高和复位到逻辑零。这些置位/复位输入会在时钟边沿有效或完全独立于时钟。当一个输入取决于时钟边缘时,我们称它为同步输入。当一个信号依赖于时钟信号,我们称它为异步输入。寄存器的输入数据往往是同步输入。异步信号从产生到输出延时被标记为(tS2Q),异步型号从复位到输出延时被标记为(tR2Q)。如果置位/复位输入时同步的,那么当从事重到输出延时覆盖它们的延时是,就不会有和有关的独立延时。对于其他输入像使能输入是有效的,但是再次输入需要取决于时钟的信号将不会有一个单独的传播延时。

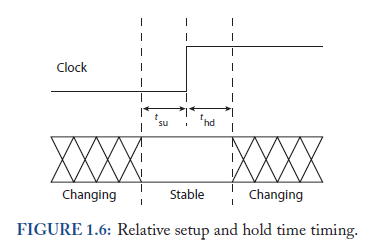

1.3.2 建立和保持时间

寄存器有一个额外的限制来保障输入可以有效地传递到输出。对于每个同步信号输入来说,信号必须在时钟边沿发生之前建立的一段时间保持一个稳定的逻辑电平。这称为寄存器的建立(tsu)时间。另外,输入信号必须在时钟边沿到来后的一段时间保持稳定。这被称为寄存器的保持(thd)时间。如果输入在建立和保持时间内改变,那么输出就不能被保证是正确的。这个规范在寄存器的技术文档中会表示,会根据内部晶体管的特性被设置。图1.6阐明了建立和保持时间的概念。

1739

1739

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?