概要

由于VHDL编程实现数字电路具有很高的灵活性,为多种不同的思路编写实现同一种功能提供了可能。这些不同的设计思路,在耗费资源,可靠性,速度上也有很大的差异,往往需要我们根据实际需求和资源条件选择适合的设计思路。

正文

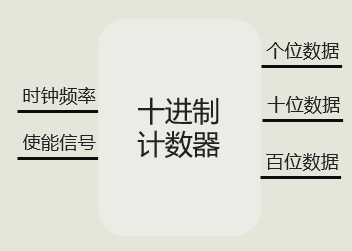

本文以十进制1k计数器作为例子,阐述不同的思路最终形成的数字电路的差异性。该十进制的需求输入输出信号如图

作为硬件设计的初学者,可能还会利用软件设计的思路来编写VHDL代码。假设我们在一个高级语言(相对应机器语言)的环境下,实现一个这样的计数器对于程序员来说,最简单不过了。维护一个自加变量,每当触发条件(这里是时钟上升沿信号)发生时,这个变量的值自加即可。至于输出该变量的每一位,则通过除余法来实现。

若是利用硬件思路来实现,则会想到利用十进制计数器了。通过多个十进制计数器进行级联,即可实现十进制1k计数器。每一个十进制计数器中的数据对应着每一位的数,可以直接输出这些计数器的数据。

这两种设计思路的不同,完成的VHDL的代码,实现的数字电路的各种特性也有很大差异。

- 软件思路

这是软件设计思路写出的VHDL代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT1000 IS

PORT (

CLK : IN STD_LOGIC ;

EN : IN STD_LOGIC ;

COUT : OUT STD_LOGIC;

D0,D1,D2 :OUT INTEGER RANGE 0 TO 9

);

END ENTITY CN

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1913

1913

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?