在Verilog中使用二进制补码数据,对负数求绝对值,也就是负数取反,正数不变。

已知负数A,则|A|=~A+1,或者|A|=-A,两种是等效的,但是FPGA编译出来资源一样?等待试试。

但是,但是,有符号数的负最大值,取反后,还是原数,如x[3:0] 是1000=-8,取反加1后后,还是1000,

则需要进行符号位扩展,在高位扩展一位符号位,然后取反加1,才是绝对值。

求绝对值,必须得符号位扩展,

下面是Modelsim仿真程序:

module tb_signed_x;

reg signed [3:0] signed_x;

reg [3:0] unsigned_x;

reg signed [3:0] abs_x;

reg signed [4:0] abs_x_ext;

reg signed [4:0] abs_x_minus;

reg clk;

always #5 clk = ~clk;

integer ii;

initial begin

ii = 0;

clk = 0;

for(ii = 0;ii<16;ii=ii+1) begin

signed_x = ii;

unsigned_x = ii;

abs_x = signed_x[3]?(~signed_x + 1'b1):signed_x; //不进行符号位扩展,<span style="font-family: Arial;">|A|=~A+1</span>

abs_x_ext = signed_x[3]?(~{1'b1,signed_x}+1'b1):{1'b0,signed_x}; //符号位扩展,<span style="font-family: Arial;">|A|=~A+1</span>

abs_x_minus = signed_x[3]?(-{1'b1,signed_x}):{1'b0,signed_x}; //符号位扩展,<span style="color: rgb(51, 51, 51); font-family: Arial; font-size: 14px; line-height: 26px;">|A|=-A</span>

@(posedge clk);

end

$stop;

end

endmodule

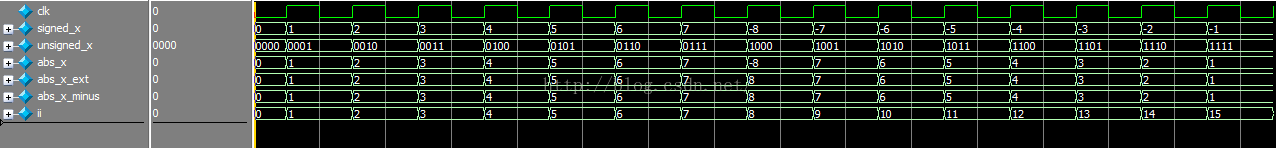

符号位扩展,才不会出现错误,在负极大值,仿真图形,-8处,不进行符号位扩展,则绝对值计算错误,取反后还是原数;符号位扩展后,结果正确;

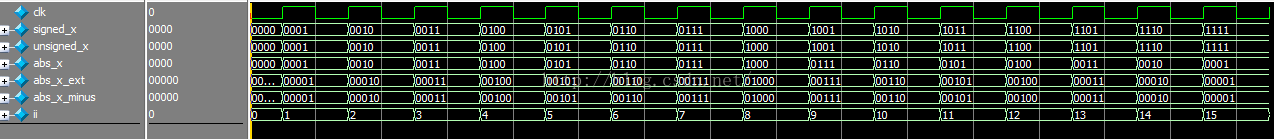

数据显示为二进制格式:

可以清晰看见转换后的二进制格式;

-----

图片看不清楚,可以右键,在新标签页打开图片,可以看大图,很清晰

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?