硬件高速缓存和TLB原理

基本概念

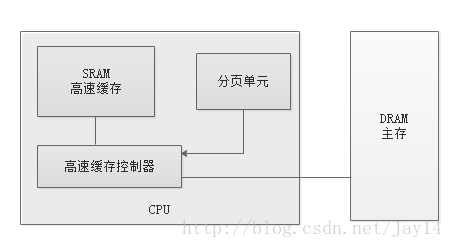

硬件高速缓存的引入是为了缩小CPU和RAM之间的速度不匹配,高速缓存单元插在分页单元和主内存之间,它包含一个硬件高速缓存内存和一个高速缓存控制器。高速缓存内存存放内存中真正的行。高速缓存控制器存放一个表项数组,每个表项对应高速缓存内存中的一个行,如下图:

除了通用硬件高速缓存,80x86处理器还包含了另一个称为转换后援缓冲器或TLB(Translation Lookaside Buffer)的高速缓存用于加快线性地址的转换。TLB是一个小的、虚拟寻址的缓存,其中的每一行都保存着一个由单个页表条目组成的块。

原理

下面通过一个具体的地址翻译示例来说明缓存和TLB的原理(注意:这是简化版的示例,实际过程可能复杂些,不过原理相同),地址翻译基于以下设定:

- 存储器是按字节寻址的

- 存储器访问是针对1字节的字的

- 虚拟地址(线性地址)是14位长的

- 物理地址是12位长的

- 页面大小是64字节

- TLB是四路组相连的,总共有16个条目

- L1 Cache是物理寻址、直接映射的,行大小为4字节,总共有16个组

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5668

5668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?