注:本博文所需工程下载链接:http://download.csdn.net/detail/lzy272942518/8850539

一、目的

学会diagram中MicroBlaze最小系统的组成

学会导出、建立以及运行基于SDK的工程

二、简介

实验目的:

1.通过tcl脚本新建工程

2.通过block diagram框图学会microblaze基本结构

3.实现microblaze调用uart模块,完成串口打印功能。

实验原理:本系统中,Basys3的Microblaze模块调用基于AXI协议的uart IP核,通过AXI总线实现microblaze-uart之间的通信,完成串口打印功能。

三、步骤:

1、运行tcl,创建新工程

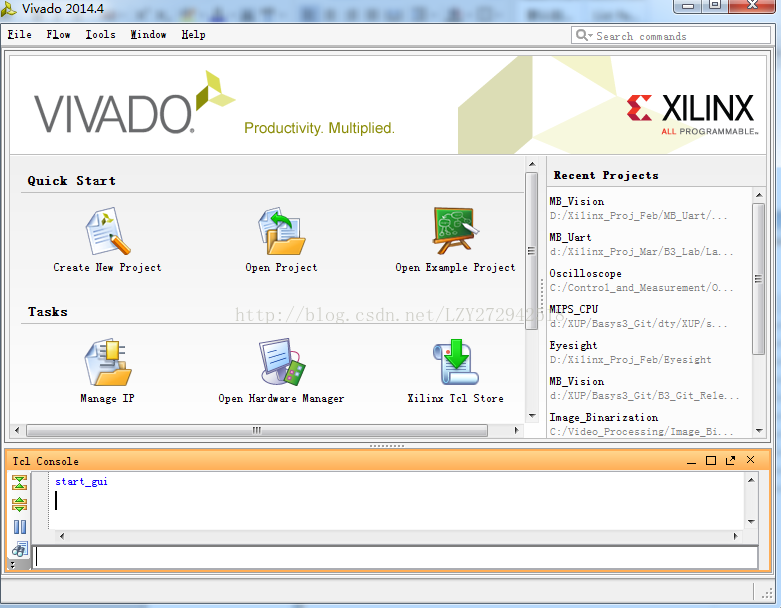

1) 打开Vivado2014.4设计开发软件

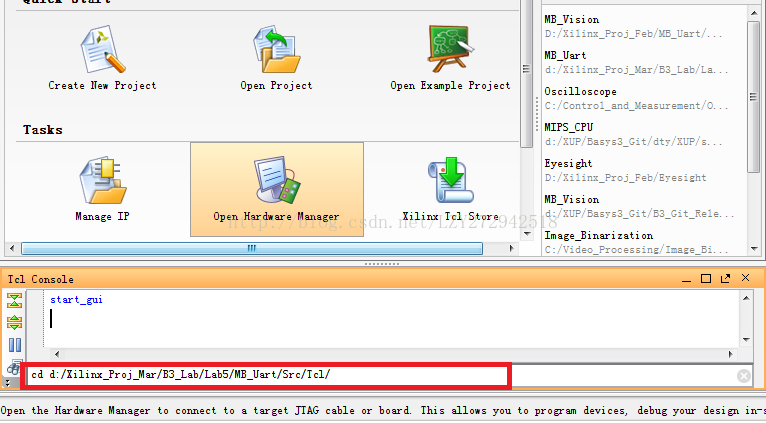

2) 在tcl console一栏,用cd指令,进入MB_Uart.tcl文件所在的路径。例如路径为d:/Xilinx_Proj_Mar/B3_Lab/Lab5/MB_Uart/Src/Tcl/,

那么就要输入:cd d:/Xilinx_Proj_Mar/B3_Lab/Lab5/MB_Uart/Src/Tcl/,如下图:

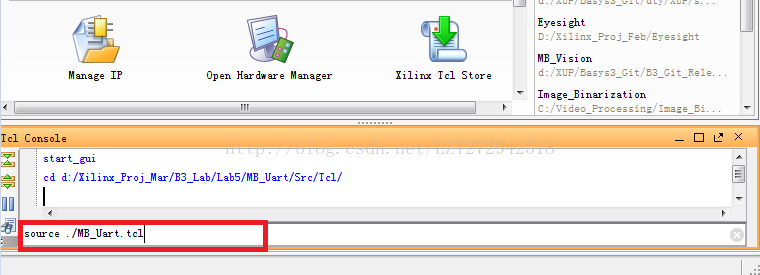

3)在tcl console一栏,输入以下指令:source ./MB_Uart.tcl。输入完毕按回车,运行tcl。如下图:

4)等待tcl综合、实现、生成bitstream;

2、建立SDK应用工程

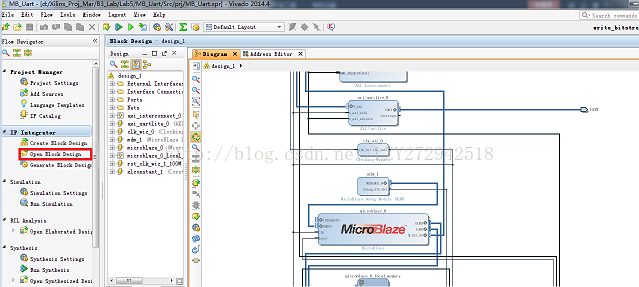

1)tcl运行结束后,点击工程界面左侧的openblock design,可以看到系统硬件框图:

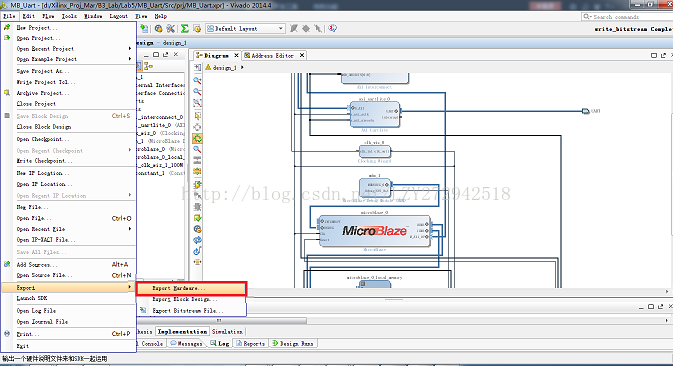

2)点击工程任务栏File->Export->Export hardware,导出硬件工程到sdk。

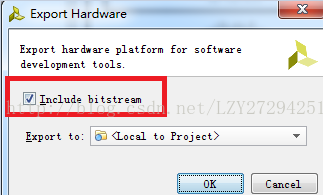

注意,在新弹出的小窗口中勾选“includebitstream”。如下:

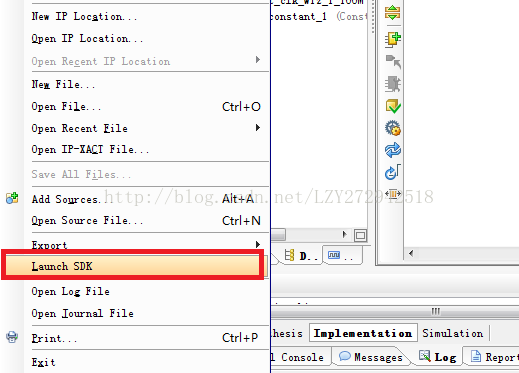

3)点击工程任务栏File->Launch SDK,启动sdk。

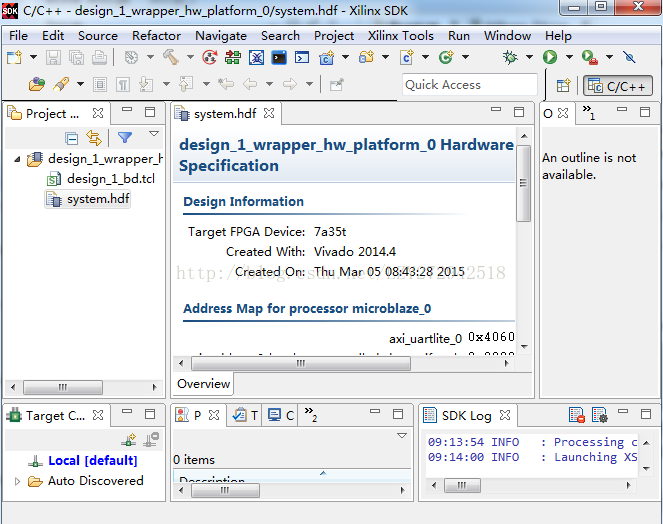

4)等待,然后SDK启动,如下界面所示:

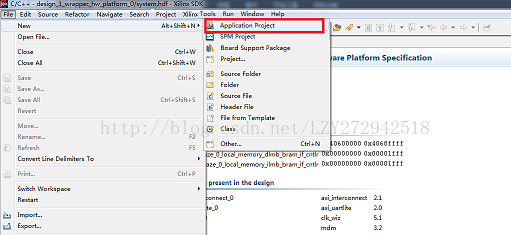

5)通过SDK任务栏New->Applicationproject,新建一个SDK应用工程:

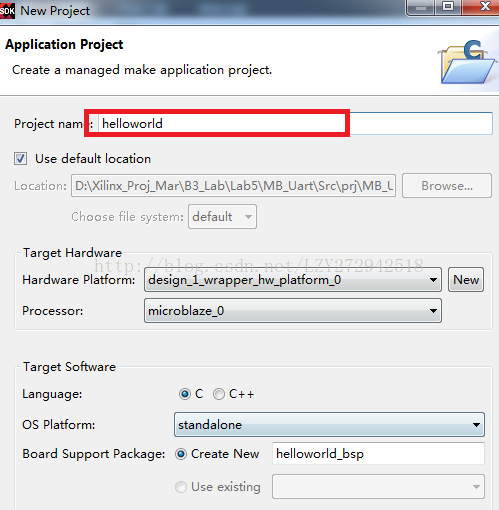

6)工程名字取为helloworld,直接点击finish完成建立:

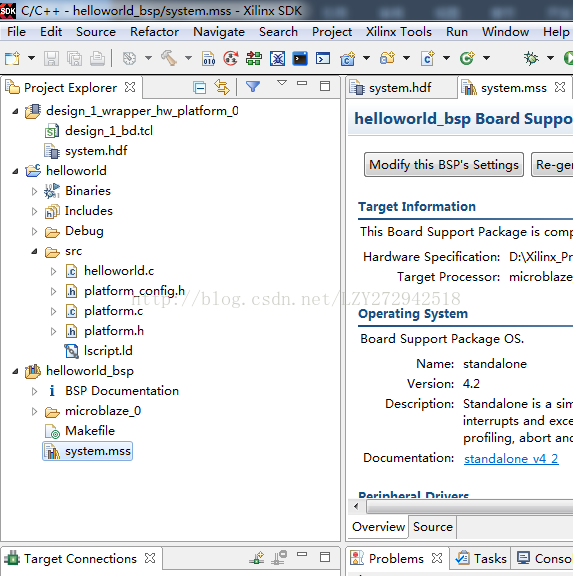

7)可以看到SDK界面左侧如下,新增加了helloworld和helloworld_bsp两项。其中helloworld_bsp为helloworld应用工程的板级支持包:

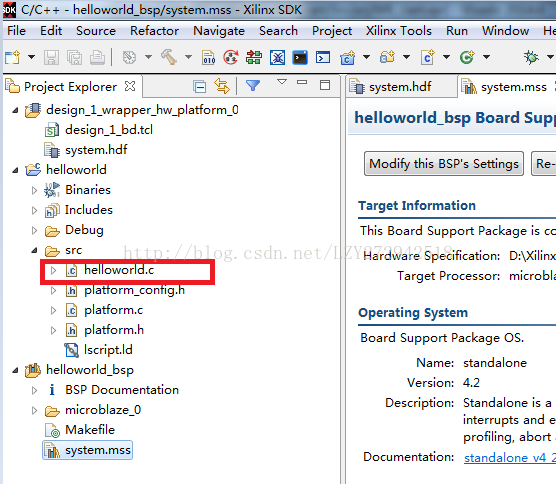

8)双击helloworld下的src下的helloworld.c。这个文件为包含主函数的c文件。然后可以通过CTRL+B完成工程的build:

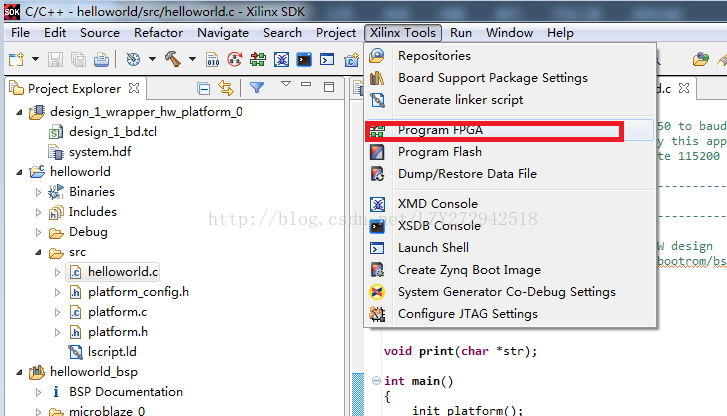

9)连接Basys3板卡,上电,点击SDK任务栏xilinx tools->Program FPGA,在新窗口中直接点击program完成bit的下载:

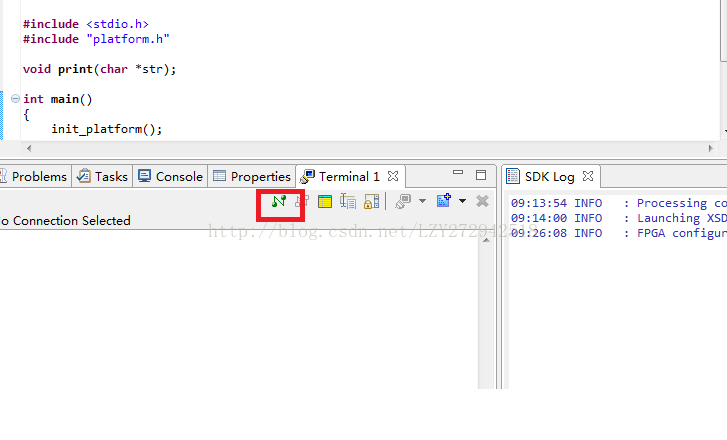

10)接下来是打开Basys3的串口。点击SDK界面下方的Terminal窗口,点击下图的连接按钮:

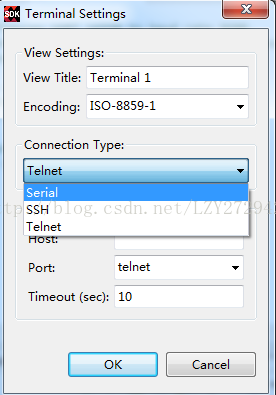

在新弹出的窗口中,将connection type改成serial:

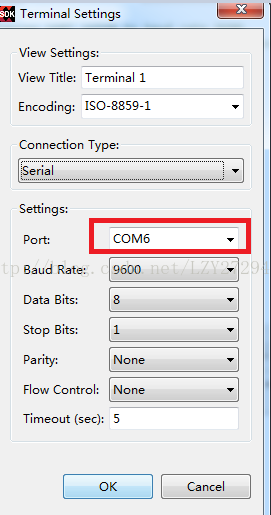

在port选择正确的串口号,然后点击OK,这样就打开了串口:

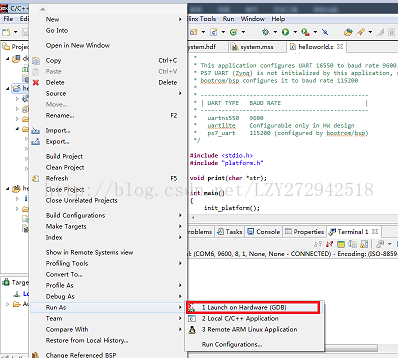

11)右击界面左侧project explorer的helloworld,选择Run as->launch on hardware(GDB),运行SDK软件工程:

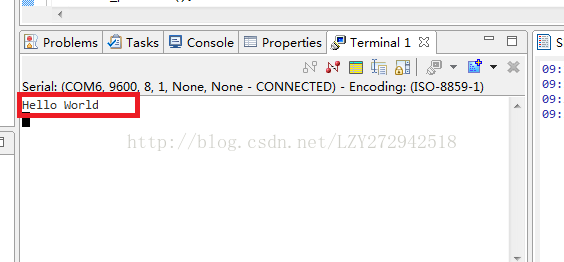

稍等几秒,可以看到terminal界面出现了打印的hello world字样:

842

842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?