本系列前面两篇文章《[攻克存储] SRAM地址线的连接》和 《[攻克存储] 存储芯片的写屏蔽及扩展》已经介绍了SRAM芯片的地址线连接方法以及存储芯片的写屏蔽扩展,这两篇文章基本上是从SRAM的角度在进行讲解和描述,其中许多原理在SDRAM/DDR芯片中也同样适用,不过,SDRAM/DDR 存储芯片的结构和寻址方式相对于ROM、SRAM、DRAM而言,还是有很大的变化和不同的,本文就着重介绍SDRAM/DDR的相关知识点和应用注意事项。

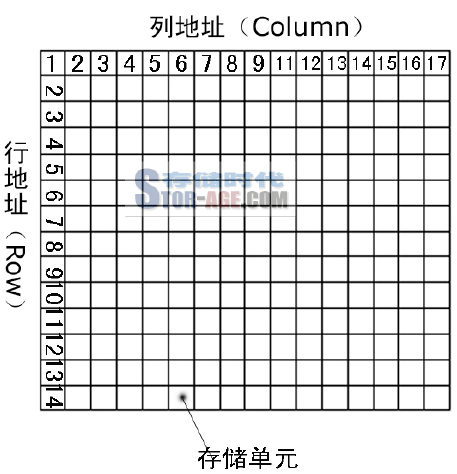

在存储结构上,SDRAM/DDR采取了多Bank方式,每一个逻辑Bank即为一个存储阵列,一般一个SDRAM芯片有2~8个Bank。我们可以把Bank想象为一个表格,如下:

图中的Bank是一个14行17列的逻辑存储结构,假设该SDRAM芯片有4个Bank,则其存储空间为:4 x 2^14 x 2^17 bit = 2^33 bit = 1GB

在寻址方式上,首先,多了几个Bank选择引脚,例如对于4个Bank的SDRAM,则有2个引脚(BA0~BA1)进行Bank选择。当具体Bank选定后,再给出行列地址从而定位到具体的存储位置。而行列地址值由相应的地址线引脚分时复用得到。

下面研究一个具体的SDRAM电路图,如下图所示,该图为ARM芯片s3c2440与SDRAM芯片HY57V561620的连接示意图。

该SDRAM芯片为 HY57V561620 ,有4个Bank,16位宽数据线,32M的存储空间。该芯片的引脚功能描述如下:

重点关注地址线 A0~A12的说明,我们可以到,该芯片每一个Bank有13行(RA0~RA12),9列(CA0~CA8),行寻址时使用A0~A12,列寻址分时复用,只使用了CA0~CA8。并且,相比于SRAM芯片,多了nRAS、nCAS引脚,用于标识当前是行寻址还是列寻址,从而实现地址线的分时复用。

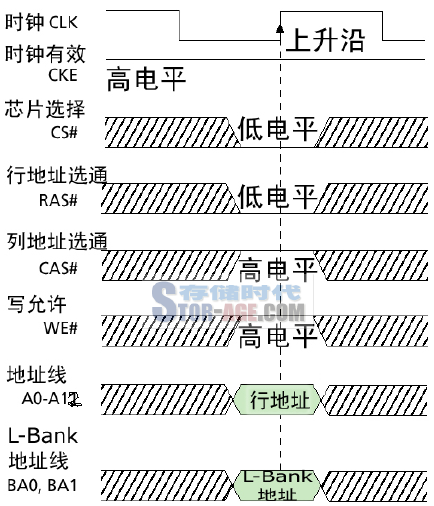

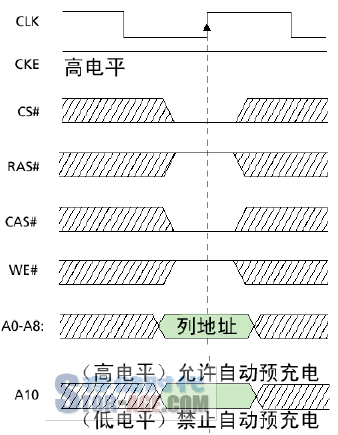

我们可以通过下面的时序图,来更加直观地了解一下SDRAM是如何寻址的:

[第一步] 选择Bank,同时给出行地址

[第二步] 给出列地址,得到数据

到此,基本上算是把 SDRAM/DDR 的结构和寻址讲完了,当然,关于SDRAM/DDR还有很多其他的相关知识点,比如 CAS 延时,比如 时钟频率,比如 DRAM/SDRAM/DDR2 的详细区别等等,将在后面的文章中陆续讲述。

最后,再补充点内容,关于上面ARM芯片s3c2440与SDRAM芯片HY57V561620的连接图,有一个细节,即为什么SDRAM芯片的BA0~BA1连接的是ARM芯片的LADDR24~LADDR25引脚?

因为,HY57V561620为32MB的SDRAM芯片,我们知道,32MB的存储空间是需要 25 根地址线寻址的,由于BA0~BA1引脚决定了访问第几个Bank,即决定了存储空间的最高两位,因此,需要使用ARM的25根地址线中的最高两位来连接 BA0~BA1,这样就可以满足寻址的映射要求了。

SDRAM/DDR的结构与寻址就介绍到这里,欢迎对文中错误以及不够清楚的地方提出意见和建议,

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?