1.协处理器(CP15)的作用

arm926ej-S的内核基于的是arm v5tej的架构,其cp15处理器单元主要有以下几个作用:

- 1.控制arm926ej-S处理器

- 2.开关Cache(I-Cache|D-Cache)

- 3.控制mmu(内存管理单元)

- 4.控制紧耦合存储器(TCM)

- 5.以及其他大部分系统配置选项

*注意:对于协处理器的访问只能在特权模式下通过MRC/MCR指令来访问,其他条件下均会造成指令访问异常的错误。

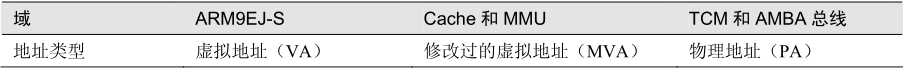

下面贴出一张cp15的寄存器组表:

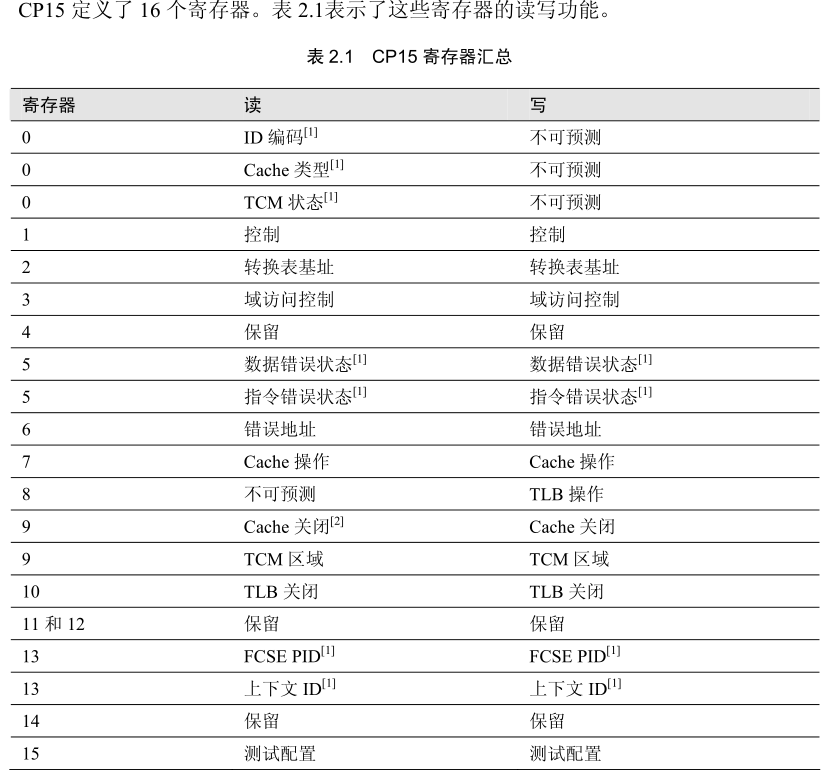

2.arm926ej-S系统的地址

在arm926ej-S系统中存在三种不同的地址

以arm926ej-s内核获取一条指令为例子,分析下实现的过程:

- 首先,arm926ej-s发出要取指令的虚拟地址

- 然后,FCSE PID将要访问的虚拟地址进行转换为修改过的虚拟地址MVA,

- 接着,如果MMU对MVA执行的保护检查没有中止,并且MVA标签在ICache中,则指令数据被送回arm926ej-s的内核

- 如果,MMU对MVA执行的保护检查没有中止,但ICache中并没有MVA的标签,那么会造成Cache没有命中,此时,MMU将MVA转化成实地址PA,该地址将被AMBA总线传送以执行一个外部访问。

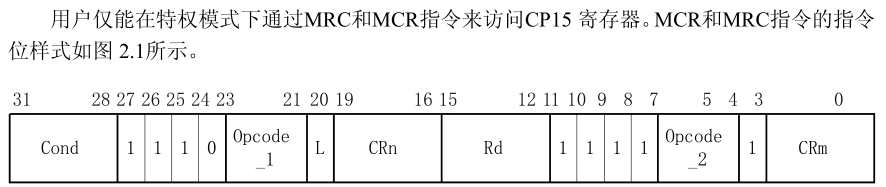

4.如何访问cp15的协处理器

1.MCR/MRC的位样:

2.简单的记忆这些访问指令就是:

mcr p15, <opcode_1>, <Rd>, <CRn>, <CRm>, <opcode_2>

mrc p15, <opcode_1>, <Rd>, <CRn>, <CRm>, <opcode_2>*注意,所有的改变寄存器值都是通过 读-改-写的方式

3.初始化的流程

- 1.测试并清理D-Cache中的脏的行,在清理的过程中,如果发现了脏的行,那么位30将会被清理成0,如果没有发现脏的行,那么为30将会被置一,使用下面的循环来清理整个D-Cache

代码一-测试和清理,但不清除D-Cache

tc_loop: mrc p15, 0, r15, c7, c10, 3 ;测试和清理,但不清除D-Cache

bne tc_loop代码二-测试和清理,并且清除D-Cache

tci_loop: mrc p15, 0, r15, c7, c14, 3 ;测试和清理,并且清除D-Cache

bne tci_loop代码三-清除TLB(传输)

mcr p15, 0, r0, c8, c7, 0 ;清除tlb代码四-打开/关闭 I-Cache/D-Cache

Icache_enable:

mrc p15, 0, r0, c1, c0, 0 ;读取cp15的从控制寄存器

orr r0, r0, #0x00001000 ;将bit12置为1

mcr p15, 0, r0, c1, c0, 0

Icache_disable:

mrc p15, 0, r0, c1, c0, 0 ;读取cp15的从控制寄存器

bic r0, r0, #0x00001000 ;将bit12置为0

mcr p15, 0, r0, c1, c0, 0

Dcache_enable:

mrc p15, 0, r0, c1, c0, 0 ;读取cp15的从控制寄存器

orr r0, r0, #0x00000004 ;将bit2置为1

mcr p15, 0, r0, c1, c0, 0

Dcache_disable:

mrc p15, 0, r0, c1, c0, 0 ;读取cp15的从控制寄存器

bic r0, r0, #0x00000004 ;将bit2置为0

mcr p15, 0, r0, c1, c0, 0

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?