最近在移植linux,用到kernel版本为3.14.28,在高版本的内核源码中用到了设备树(device-tree),设备树中用到pinctrl的配置,记录一下。

1、普通设置

在配置串口时,pinctrl的配置信息如下所示:

- &uart2 {

- pinctrl-names = "default";

- pinctrl-0 = <&pinctrl_uart2>;

- status = "okay";

- };

- //。。。。。。。。

- pinctrl_uart2: uart2grp {

- fsl,pins = <

- MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA 0x1b0b1

- MX6QDL_PAD_SD4_DAT4__UART2_RX_DATA 0x1b0b1

- >;

- };

这里的MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA在imx6dl-pinfunc.h文件中有如下定义:

- MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA 0x35c 0x744 0x000 0x2 0x0

将管脚的配置展开即: 0x35c 0x744 0x000 0x2 0x00x1b0b1

想知道这六个值都是什么意思,可以从两个路出发:①查找解读dts的文件,即看内核源码;②在网上查找相关知识。

1.1 查看源码对设备树文件的解读

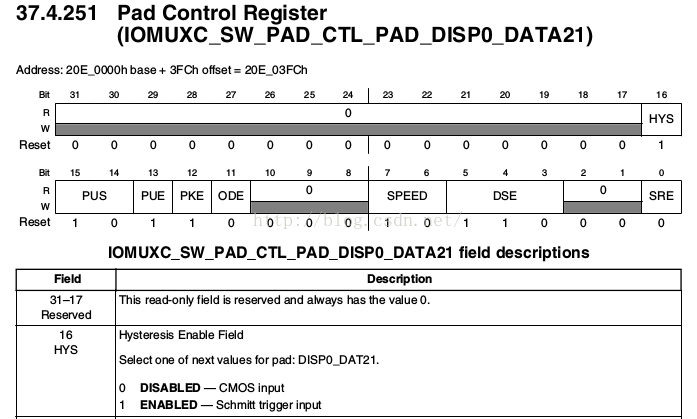

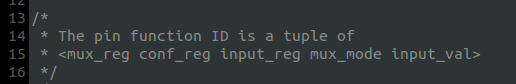

首先在imx6dl-pinfunc.h文件中有对前5个变量的解释,如下图:

为了验证这5个变量,并查找第6个变量的含义,我们打开读取设备树文件的代码。

读取dts文件的文件为:drivers/pinctrl/freescale/pinctrl-imx.c,实现函数名为:static int imx_pinctrl_parse_groups(。。。),如下:

- static int imx_pinctrl_parse_groups(struct device_node *np,

- struct imx_pin_group *grp,

- struct imx_pinctrl_soc_info *info,

- u32 index)

- {

- int size, pin_size;

- const __be32 *list;

- int i;

- u32 config;

- dev_dbg(info->dev, "group(%d): %s\n", index, np->name);

- if (info->flags & SHARE_MUX_CONF_REG)

- pin_size = SHARE_FSL_PIN_SIZE;

- else

- pin_size = FSL_PIN_SIZE;

- /* Initialise group */

- grp->name = np->name;

- /*

- * the binding format is fsl,pins = <PIN_FUNC_ID CONFIG ...>,

- * do sanity check and calculate pins number

- */

- list = of_get_property(np, "fsl,pins", &size);

- if (!list) {

- dev_err(info->dev, "no fsl,pins property in node %s\n", np->full_name);

- return -EINVAL;

- }

- /* we do not check return since it's safe node passed down */

- if (!size || size % pin_size) {

- dev_err(info->dev, "Invalid fsl,pins property in node %s\n", np->full_name);

- return -EINVAL;

- }

- grp->npins = size / pin_size;

- grp->pins = devm_kzalloc(info->dev, grp->npins * sizeof(struct imx_pin),

- GFP_KERNEL);

- grp->pin_ids = devm_kzalloc(info->dev, grp->npins * sizeof(unsigned int),

- GFP_KERNEL);

- if (!grp->pins || ! grp->pin_ids)

- return -ENOMEM;

- for (i = 0; i < grp->npins; i++) {

- u32 mux_reg = be32_to_cpu(*list++);

- u32 conf_reg;

- unsigned int pin_id;

- struct imx_pin_reg *pin_reg;

- struct imx_pin *pin = &grp->pins[i];

- if (info->flags & SHARE_MUX_CONF_REG)

- conf_reg = mux_reg;

- else

- conf_reg = be32_to_cpu(*list++);

- pin_id = mux_reg ? mux_reg / 4 : conf_reg / 4;

- pin_reg = &info->pin_regs[pin_id];

- pin->pin = pin_id;

- grp->pin_ids[i] = pin_id;

- pin_reg->mux_reg = mux_reg;

- pin_reg->conf_reg = conf_reg;

- pin->input_reg = be32_to_cpu(*list++);

- pin->mux_mode = be32_to_cpu(*list++);

- pin->input_val = be32_to_cpu(*list++);

- /* SION bit is in mux register */

- config = be32_to_cpu(*list++);

- if (config & IMX_PAD_SION)

- pin->mux_mode |= IOMUXC_CONFIG_SION;

- pin->config = config & ~IMX_PAD_SION;

- dev_dbg(info->dev, "%s: 0x%x 0x%08lx", info->pins[pin_id].name,

- pin->mux_mode, pin->config);

- }

- return 0;

- }

这段代码中list = of_get_property(np, "fsl,pins", &size);实现了读取dts文件中的fsl,pin属性值,并保存在了list指针变量中。紧接着,分别将list中的值mux_reg、conf_reg、input_reg、mux_mode、input_val、config六个变量中,由名字可以猜测个大概,前5个得以验证,第六个表示config,config的值说白了就是对寄存器配置(上拉电阻、频率等等)的值,就是pad_ctrl的值。

因此对应关系如下:

0x35c | 0x744 | 0x000 | 0x2 | 0x0 | 0x1b0b1

---------------------------------------------------------------------------------------------------------

mux_ctrl_ofs | pad_ctrl_ofs | sel_input_ofs | mux_mode | sel_input | pad_ctrl

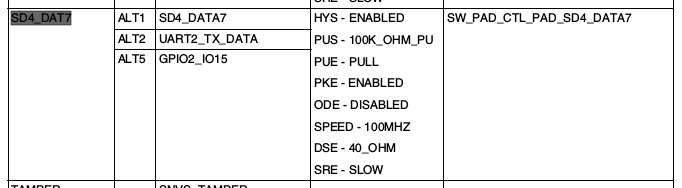

以上参数在参考手册怎么确定的呢?由于是对复用管脚的配置,于是在管脚复用的章节(IOMUXC)中查找。但是现确定pad name才方便,于是定义在External Signals and Pin Multiplexing章节,搜索MX6QDL_PAD_SD4_DAT7__UART2_TX_DATA的中间部分:SD4_DAT7,如下图

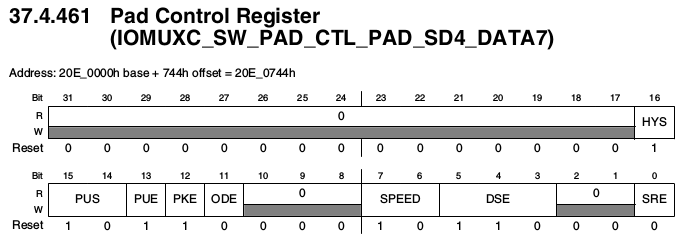

可知UART2_TX_DATA是属于SD4_DAT7的ALT2,于是mux_mode=0x2即可。上图表格中最后一列SW_PAD_CTL_PAD_SD4_DATA7是config配置需要查找的名称,跳到管脚复用的章节(IOMUXC)中,找到SW_PAD_CTL_PAD_SD4_DATA7,如下所示:

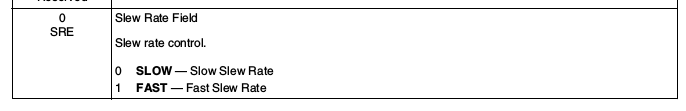

如果直接取默认值的话结果是config=0x1b0b0,这里可以根据自己的需要(硬件)更改为与自己的板子匹配的值,我把最后SRE的值设置为1,即Fast Slew Rate,如下图说明:

OK,接下来是mux_ctrl_ofs、pad_ctrl_ofs、sel_input_ofs三个偏移值,这些值都是在复用管脚的章节确定的。因为pad name为SD4_DATA7,所以在找的时候可以拿它当关键字。

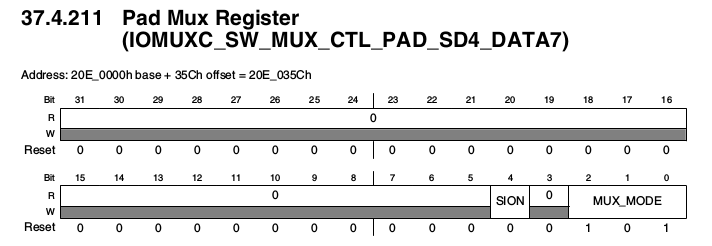

首先是mux_ctrl_ofs,找到IOMUXC_SW_MUX_CTL_PAD*开头的部分,结尾选择SD4_DATA7即可,如下图,

由”Address: 20E_0000h base + 35Ch offset = 20E_035Ch“中可知offset=35C,即mux_ctrl_oft=0x35c

其他的查找方法类似。pad_ctrl_ofs,查找IOMUXC_SW_PAD_CTL_PAD_SD4_DATA7一节,可知偏移值pad_ctrl_ofs=0x744

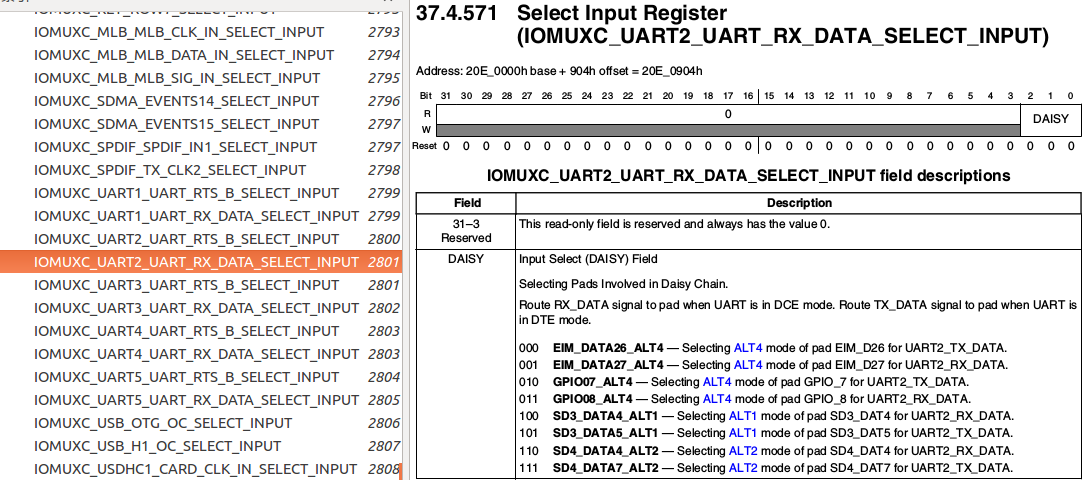

sel_input_ofs查找IOMUXC章节以SELECT_INPUT结尾的部分,中间选择UART2_TX,如果没有这里sel_input_ofs=0x000即可,对应的sel_input为0即可。如果有例如IOMUXC_UART2_UART_RX_DATA_SELECT_INPUT,即uart的rx管脚配置,如下图,所以RX的sel_input_ofs=0x904,这里选择对应的值“110 SD4_DATA4_ALT2 — Selecting ALT2 mode of pad SD4_DAT4 for UART2_RX_DATA..“所以RX(MX6QDL_PAD_SD4_DAT4__UART2_RX_DATA)的sel_input=0x6。

首先还是先看代码,看看到底特殊到哪里。

- pinctrl_gpio_leds: gpioledsgrp {

- fsl,pins = <

- MX6QDL_PAD_DISP0_DAT21__GPIO5_IO15 0x80000000

- >;

- };

- pinctrl_i2c2: i2c2grp {

- fsl,pins = <

- MX6QDL_PAD_EIM_EB2__I2C2_SCL 0x4001b8b1

- MX6QDL_PAD_KEY_ROW3__I2C2_SDA 0x4001b8b1

- >;

- };

可以看出来特殊的配置就是后面的值也就是上一篇讲的config(pad_ctrl)的值改变了,变为0x80000000和0x4001b8b1了,当我们查找相应的pad值时是这样的:

这明显不和常理,在上图中显示高15位全部置0,取值也没啥用,那么为什么设置为0x80000000和0x4001b8b1呢?在网上搜罗一番没有任何有帮助的文档,只能靠自己了。还是老思路,查找设备树文件的读取源码,drivers/pinctrl/freescale/pinctrl-imx.c中,找到了惊喜!!!代码如下

- /* The bits in CONFIG cell defined in binding doc*/

- #define IMX_NO_PAD_CTL 0x80000000 /* no pin config need */

- #define IMX_PAD_SION 0x40000000 /* set SION */</span>

- for (i = j = 0; i < grp->npins; i++) {

- if (!(grp->pins[i].config & IMX_NO_PAD_CTL)) {

- new_map[j].type = PIN_MAP_TYPE_CONFIGS_PIN;

- new_map[j].data.configs.group_or_pin =

- pin_get_name(pctldev, grp->pins[i].pin);

- new_map[j].data.configs.configs = &grp->pins[i].config;

- new_map[j].data.configs.num_configs = 1;

- j++;

- }

- }

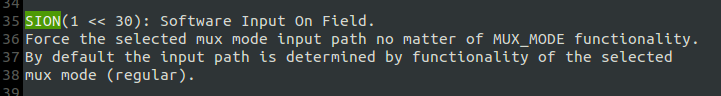

同理0x40000000表示设置了SION。但是0x4001b8b1表示什么意思呢,从上一个注释(/* The bits in CONFIG cell defined in binding doc*/)可以找到方向,即取binding doc中找,所以打开Documentation/devicetree/bindings/pinctrl目录下的fsl,imx6dl-pinctrl.txt文件,里面有关于SION的介绍,如下:

再从芯片的参考手册中查阅可知,SION就相当于一个标志为(第30位),去掉这一位后config=0x1b8b1,这个值就是从pad_ctrl一节找到的,具体可以参见第6个参数的确定方法。

1070

1070

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?