目的

1. 进一步掌握VHDL语言的基本结构及设计的输入方法。

2. 掌握8选1数据选择器的设计思路;

内容

1. 用拨码开关SW7~SW0作为数据输入端D7~D0的输入,SW10~SW8作为数据选择端C、B、A的输入,SW11作为选通端STROBE的输入, LEDR0作为数据输出端Y的输出, LEDR1作为反码数据输出端W的输出。

2. 观察Y与数据输入端D7~D0的关系,验证八选一数据选择器设计的正确性。

原理

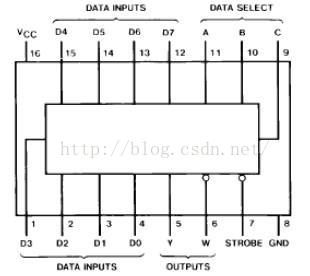

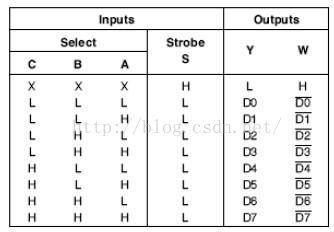

CT74151为互补输出的8选1数据选择器,其引脚排列图如图2-28所示。数据选择端(ABC)按二进制译码,从8 个数据(D0---D7)中选取1 个所需的数据。只有在选通端STROBE 为低电平时才可选择数据。151 有互补输出端(Y、W),Y 输出原码,W 输出反码。

图2-28 CT74151管教图

表2-3 CT74151功能表

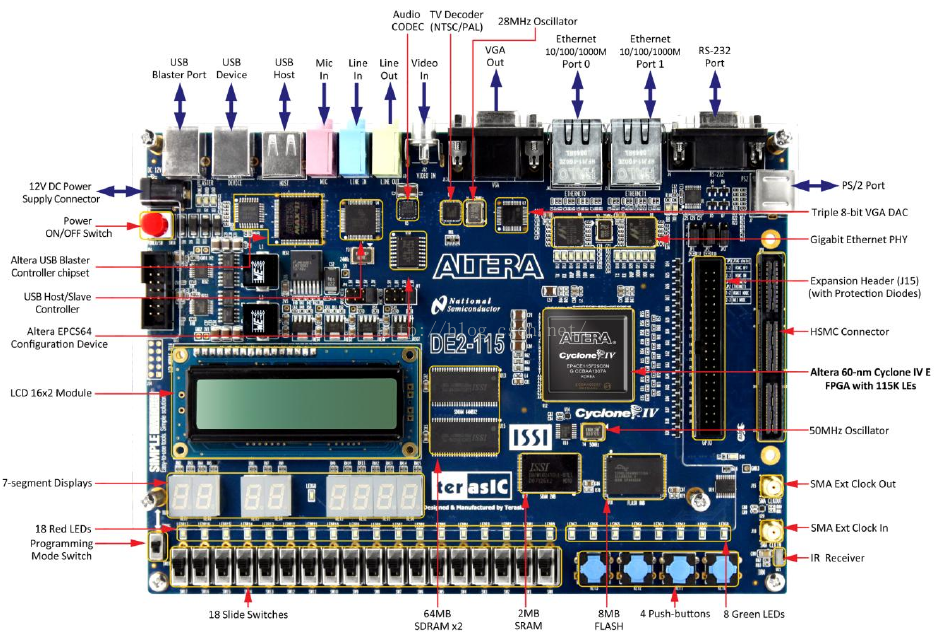

1.创建一个Quartus II 工程,用来在DE2-115上实现预期电路。

2.写出预期电路的VHDL代码。

3.将VHDL文件包含进工程并编译。

4.仿真电路来检测其功能。

5.分配引脚。

6.重新编译并将其下载进FPGA芯片中。

通过DE2-115开发板来证实电路是否准确。

程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CT74151 IS

PORT(A,B,C,D0,D1,D2,D3,D4,D5,D6,D7,STROBE: IN STD_LOGIC;

Y,WN: OUT STD_LOGIC);

END CT74151;

ARCHITECTURE behave OF CT74151 IS

SIGNAL sel: STD_LOGIC_VECTOR (2 DOWNTO 0);

BEGIN

sel<=C&B&A;

PROCESS (sel,STROBE)

VARIABLE Y_TEMP:STD_LOGIC;

BEGIN

IF STROBE=’0’ THEN

CASE sel IS

WHEN "000" => Y_TEMP :=D0;

WHEN "001" => Y_TEMP :=D1;

WHEN "010" => Y_TEMP :=D2;

WHEN "011" => Y_TEMP :=D3;

WHEN "100" => Y_TEMP :=D4;

WHEN "101" => Y_TEMP :=D5;

WHEN "110" => Y_TEMP :=D6;

WHEN "111" => Y_TEMP :=D7;

WHEN OTHERS=> Y_TEMP :='X';

END CASE;

END IF;

Y<=Y_TEMP;

WN<=NOT Y_TEMP;

END PROCESS;

END behave;

问题及解决

文件名必须与VHDL文件中的设计实体名保持一致。

总结:这次课程设计虽然在功能上完全实现了课题的要求,即实现了八选一数据选择器的全部要求,但是相应的不足之处还应该考虑到。怎样更好地布局以及连线,使整个电路图不至于杂乱无章等等问题,虽然是细节问题,但往往可以决定成败,这些问题都应该引以为戒并作为以后设计相关电路时的参考。

322

322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?