I2S音频总线学习(四)I2S接口设计

一、数据发送端的设计

图1 发送端

随着WS信号的改变,导出一个WSP脉冲信号,进入并行移位寄存器装入DATA LEFT或DATA RIGHT,从而输出数据被激活。串行数据在时钟下降沿移出。串行数据的默认输入是0,因此所有位于最低位(LSB)后的数据将被设置为0。

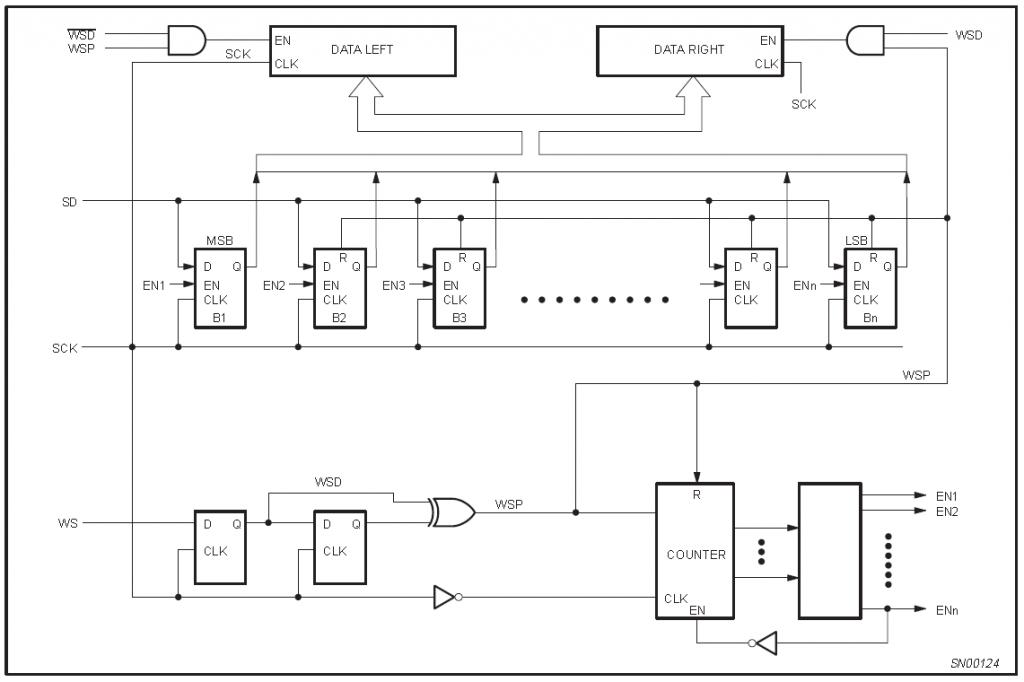

二、数据接收端的设计

图2 接收端

随着第一个WS信号的改变,WSP在SCK信号的下降沿重设计数器。在“1 out of n”译码器对计数器数值进行译码后,第一个串行的数据(MSB)在SCK时钟信号的上升沿被存放进入B1,随着计数器的增长,接下来的数据被依次存放进入B2到Bn中。在下一个WS信号改变的时候,数据根据WSP脉冲的变化被存放进入左(声道

订阅专栏 解锁全文

订阅专栏 解锁全文

2212

2212

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?