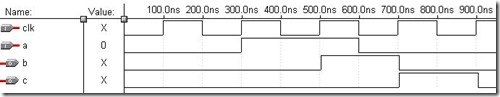

非阻塞赋值的例子:新赋值不会影响当前always中执行的语句,因为其综合成寄存器,有效输入是时钟上升沿到达前的数据。

reg c,b;

always@(posedge clk)

begin

b <= a;

c <= b;

end

非阻塞赋值语句简述为:在一个always 块中,语句是并行执行的

module nonblockingassignment (clk ,q1,q2);

input clk;

output [2:0] q1,q2;

reg[2:0] q1,q2;

always @ (posedge clk)

begin

q1<=q1+3'b1;

q2<=q1;

end

endmodule

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6586

6586

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?