一、hyperlink的使用

1.overview

1.DSP之间用于高速,低延迟,少管脚的通信接口,可以模拟多种当前使用的外设接口。

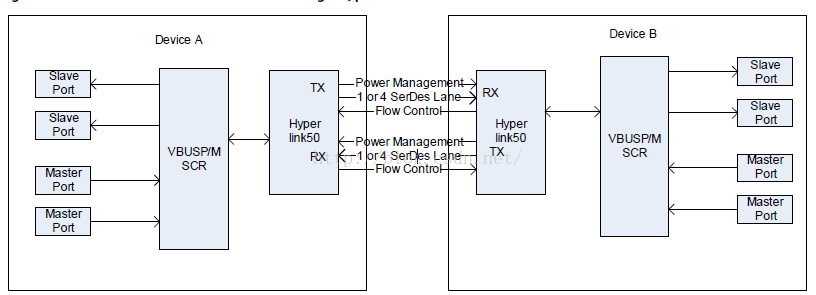

2.hyperlink包括数字信号和边频带控制信号。数字信号是基于serdes的,边频带信号是基于LVCMOS的。当前的hyperlink提供点对点的连接方式。

2.feeatures

1.少量的pin只有26个,数据传输才用serdes,控制信号才用LVCMOS

2.所有的信号都由一个设备驱动和提供,所有的LVCMOS边频带信号都使用源同步时钟

3.每个通道12.5G,1or4通道用于发送和接收,可以支持serdes全速,半速,四分之一和八分之一的更低的速度。serdes自动侦测和校正polarity,自动识别通道和校正。

4.基于简单的包的映射内存间的传输协议,写请求,写数据,读请求,读反馈数据,中断请求,支持多种优秀的传输。

5.点对点的连接,请求和反馈数据通过一个物理管脚被复用?支持主机/外围设备以及点对点的通信模式

6.提供的LVCMOS管脚可以用于留空和电源管理,支持单个方向单个通道的流控,支持单个lane单个方向的电源管理

7.省电模式自动调整Lane位宽。

8.用于诊断和调试模式的serdes内部回环

9.无需外部上拉或者下拉电阻

10.64个硬件和软件中断。

11.8个中断指针地址

12.不支持写反馈的包e

13.TX和RX必须运行在同一个速度下。

14.该版本中没有外部的控制字命令。

15.最大支持64bytes的远程寄存器,超过寄回引起总线冲突。

16.不支持独占传输操作。

17.CBA constant mode is not supported for bursts larger than 256-byte aligned burst

3.功能框图

1.从FIFO来的数据流通过MAC和PLS到达wire

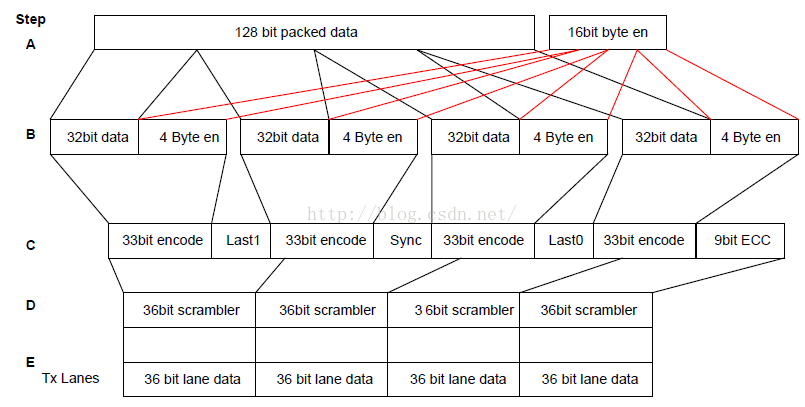

2.每一个lane可以工作在12.5G,hyperlink有自己有效的编码方式来支持物理层。和传统的8b10b编码方式相比,hyperlink去掉了编码的overhead。

3.边带信号提供流控和电源管理控制信息。硬件自己控制,软件无法配置干预。如下:

4.架构

1.hyperlink需要一个参考时钟为SerDes模块服务,可以选择156.25Mhz,250Mhz,312Mhz。

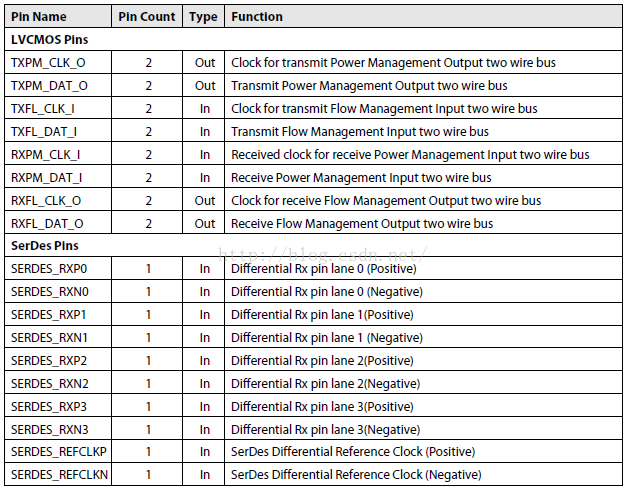

2.管脚描述,serdes是数据传输,LVCMOS是边带信号用于控制,数了一下一共26根线,8*2的LVCMOS线,10根serdes线。具体功能如下图:

3.TXPM和TXFL控制serdes的TXDATA;RXPM和RXFL控制serdes的RXDATA。

4.电源管理和流控管理的四个位D3D2D1D0只有前两位D0D1是有效的,D0=1表示支持高于12.5G的Baud,D0=0表示支持12.5G和低于。D1=1表示支持4个通道,D0=0表示不支持4个通道。

5.激活通道:

激活通道,传输方通过TXPM发送一个power-up事件告知接收者。接收方通过RXPM接收该power-up事件,然后使能接收。档接收方已经完全和传送方的训练序列同步之后,接收方发送个事件回去告诉发送者现在可以使用通道来进行数据传输了。然后接收方侦测到该传输并从训练队列切换到数据接收模式。

在serdes内支持符号对齐,PLS需要使能去通知serdes符号对齐会发生。同步字包含一个comma"逗号?"以方便serdes可以轻易的完成。每一个通道都需要符号对齐,取决于其他通道的状态,相位矫正也许会在所有活动的lane中发生。这使得开发一个通道到四个通道的时候,在对齐过程中不会taken down。

流控对用户是透明的,hyperlink的接收端自动管理可用资源的传输流量,并且限制TX端的流量通过边带信号。

6.电源管理:

hyperlink根据lane power management register决定通道的电源状态,并且通过sideband signals统治相关的接收者进入相同的电源状态。

在重启阶段,serdes和所有通道一样处于掉电模式。当退出掉电模式之后,HYPERLINK模块通过sideband总线发送一条消息给远程的相关设备请求其能力。当收到应答之后,HYPERLINK自动的进入一种可操作的状态。serdes只有在PWRMGT寄存器被清零或者传送挂起的时候才会被带出复位。hyperlink模块会基于PWRMGT寄存器和outbound load来自动的改变电源模式。默认情况下,HYperlink 让传输连接空闲知道节后到从VBUS的从端口来的传输。然后hyperlink进入单一通道模式为该传输服务并且一个通道的上电处理也已经完成。hyperlink根据traffic load动态的管理他的电源模块。当一个通道跟不上数据传输的时候,hyperlink就会自动进入四个通道的模式,如果流量低于一个通道的,那就自动转到单通道模式。如果流量进一步减少,Hyperlink会自动的进入0通道模式,关闭serdes的传输,直到通道内有传输来。发送和接收都是独立控制的一遍一些应用只有一个方向的传输。

不同模式的传输是被lane power management寄存器控制的。

7.serdes配置和时钟

该模块控制hyperlink的开发速率,提供hyperlink的发送和接收以及外部设备的管脚之间的接口。文档末尾体供了配置serdes的相关例子。serdes寄存器是芯片级的,并不在hyperlin的配置寄存器空间。在操作这些寄存器之前,必须对Kick寄存器操作以允许有对寄存器操作的权限。

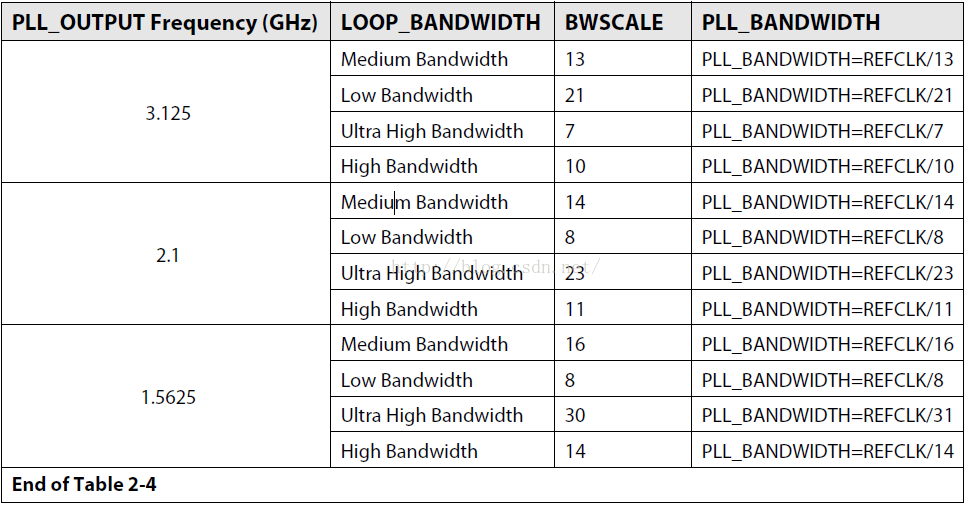

serdes的时候取决于hyperlink serdes PLL和发送接收的RATESCALE,速率比例因子。环路带宽?loop bandwidth。

hyperlink serdes的主要目的是由一个低频率的参考时钟(REFCLK)生成一个高频率的输出时钟。PLL输出频率由MPY决定,MPY在HYPERLINK_SERDES_CFGPLL中,计算公式如下:

PLL_OUTPUT=REFCLK*MPY

输出范围必须在1.5625GHz到3.125GHz的范围内。

为了消除抖动带来的干扰,引入了LOOP_BANDWIDTH来设置,公式如下:

PLL_BANDWIDTH = REFCLK/BWSCALE

BWSCALE和PLL_OUT以及LOOP_BANDWIDTH的关系如下表,8~30MHZ是一个特殊范围,可以根据下面的表来进行配置:

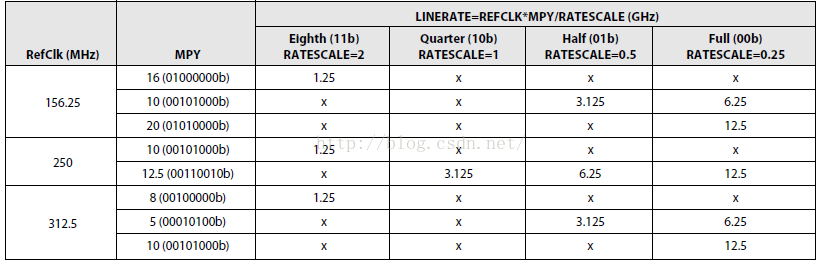

RateBITS可以设置一个频率系数,例如0.25.0.5等,LINRATE的计算公式如下:

LINERATE=REFCLK*MPY/RATESCALE,最大为12.5GHZ

有一个参考的配置表如下:

8.SerDes的接收接口

有四个数据通道,可以在HYPERLINK_SERDES_CFGRX[3-0]的系统级寄存器中,ENRX域会给出接收模块的状态。hyperlink自动使能接收模块。接收模块的主要作用是在接收信号来的时候处理数据和时钟。CDR寄存器配置该功能。时钟数据recover算法的目的是简化RXp和RXn以至于数据样本在数据传输中途可以被提取,这是为了决定样本式中是被空闲了还是需要传输的早一些或者晚一些。

可以检测到信号丢失的情况,配置LOS域的寄存器。

9.SerDes的发送接口

对应接收接口的ENTX域寄存器可以给出发送接口的状态,该模块自动使能。

发送接口使能发送通道,提供信号传输中的信号调制选项,关注SWING,TWPRE,TWPST1寄存器。

10.SesDes的训练过程

一旦PLL设定好了,稳定输出了,lock了,就开始边带信号和训练步骤。

当一个非0的MPY值写到HYPERLINK_SERDES_CFGPLL寄存器中的时候,会锁定锁相环并且传输步骤被触发,为了保证hyperlink配合寄存器被合适的设置在初始化训练步骤的时候,并且确保自动协商,以下步骤需要被遵守:

1.复位要做好

2.出reset状态,在运行应用程序

3.配置hyperlink寄存器和SerDes的发送和接收配置寄存器

4.配置MPY和PLL寄存器,如果配置有效,PLL会锁定并且给出期望的频率输出。

5.HYperlink会等待SerDes的PLL锁定,并且开始Hyperlink的边带信号和传输步骤。

SDCS1(sleep_cnt)控制标识的通道进入睡眠或者使能的状态。这样可以允许在链接建立之前电源供电稳定。该寄存器是控制链接和恢复状态前的一个稳定状态。

Sleep masked symbol count = sleep_cnt x 16 x Unit Interval

Disable masked symbol count = disable_cnt x 16 x Unit Interval

sleep_cnt和disable_cnt的建议值为最大值0xff

11.Hyperlink的协议

h提供三种类型的传输,读,写和中断事件。

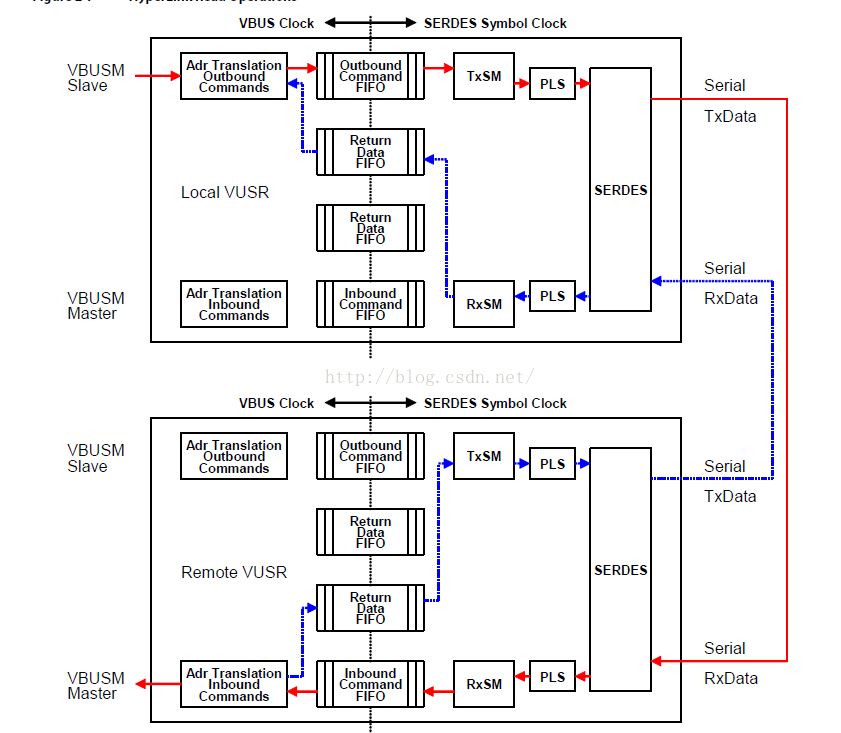

1.hyperlink写操作

从slave VBUSM端口接收写传输,写命令被写在outbound Command FIFO里面,数据被立即从FIFO中读取,被封装成一个写请求的包。输出地址传输逻辑overly将控制信息输出到地址域,包被编码并且串行化在被传输到远程设备之前。远程设备收到包,解串,解码收到的数据。远程的h模块存储收到的写数据包到inbound commandFIFO里面。入口地址传输逻辑激活新的映射笛之爱并且为写传输其他的控制信息激活例如安全和PRIVID。远程设备内部的h模块初始化一个VBUSM maste的写操作,基于新的地址和其他控制信息。写的数据Land到远程设备,每次写是256B,如果数据大于这个,那就拆包,并且每一个256B的包都会重复上述步骤。见下图红色箭头走向。

2.hyperlink读操作

hyperlink接收一个VBUSM从端口的读请求,读的请求被存放在outbound command FIFO里面,读的命令被存放在outbound command的FIFO里面,输出地址转换逻辑识别要读的地址,并且加上控制信息,然后再打包成一个读的请求包。这个包被编码,串行化发送到远程设备去了,远程设备通过自己的h接口接收读请求包。该包被解串,解码并且写到inbound command FIFO里面。远程设备从inbound command FIFO里面读出读请求包并且初始化一个读请求,该请求基于地址和控制信息。(之前发送读请求那一端打包进来的)。读请求从h的masterVBUSM端口到从端口之间一个的终点。当远程设备的h模块接收到了读的返回数据,数据被写到return datd FIFIO里面,然后进行串行化。远程设备将读返回的数据发送出去通过h模块的接口,本地的h模块接口接收到数据。传输大小256B,一次传输大于这个会被拆包。具体路径见下图红色和蓝色。

3.hyperlink的格式化

hyperlink传输到远程设备是通过控制字和数据字,每一个Hyperlink包都包括一到两个控制字和多个数据字。控制字和控制字扩展被定义在section 0和0相关的地方。extend control位为1的时候,扩展控制域才会被包含进去。具体的协议信息,不需要太关注。

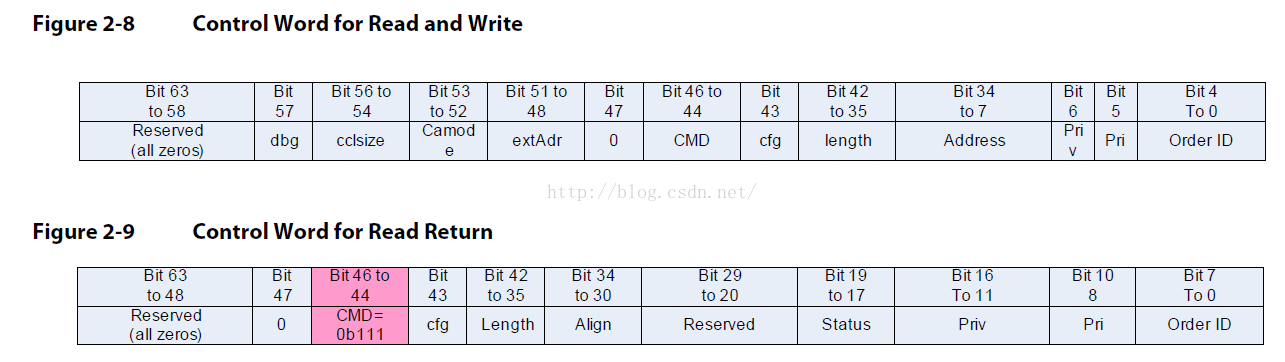

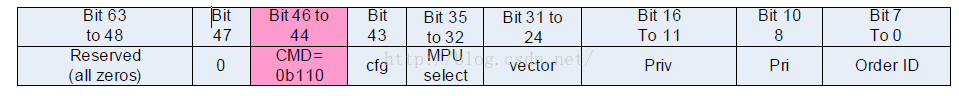

一个数据包总是以一个控制字开始,一共有四中类型的控制字:write post ,read,interrupt和read data return。如下:

具体的每一位的表在datasheet的协议节,需要去对应。

4.地址转换

hyperlink有独立的内部地址外部地址的转换模块。ingress的作用是将控制信息覆盖到相关的地址上,egress的作用是将进来的地址重映射到相关的内存区域中。hyperlink支持高大64个不同的内存映射。每一个内存区域的其实地址可以被放在任何64KB地址的边界上,就是说要64KB对齐了?每个映射内存的大小可以sized of power of two,以256B为开始。

最大映射的区域大小为256M。有些传输特性已经嵌入到控制字里面,比如优先级,监督者(supervisor),使用模式等。

转换格式为,先将从机的目标地址和和安全位私有ID打包在一起,形成一个覆盖域,目标地址的低端部分拎出来组成一个lower portion of slave address,该部分和覆盖阈组和起来变成一个输出的yperlink地址。在接收端。有一个控制器,输入端为rxsecsel,这个用来选择security bit,rxsegsel用来输出seg value,段的值,这个段的值在比较重要,和进来的低端部分的地址组和生成一个头,打包成新的输出地址。第三个是privIDsel,这个ID一共有16个,分别为0到15,作用暂时不明。

输出通道决定地址如何修剪禀赋高控制信息,例如到远程设备的security 和 privID。

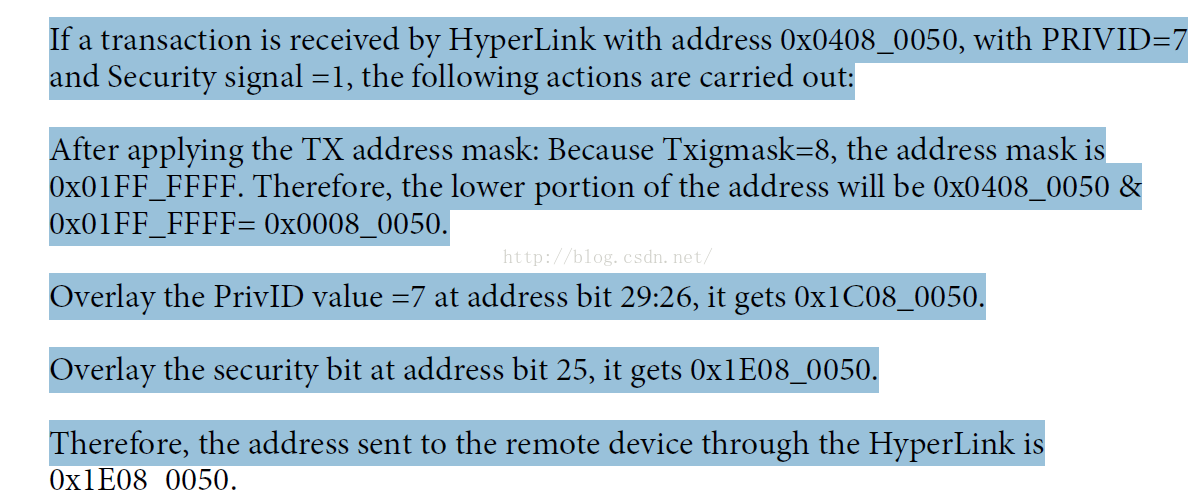

Tx地址的产生发分为三个阶段,取地址,加入privid,加入security bit,这两个都有16个不同的值。

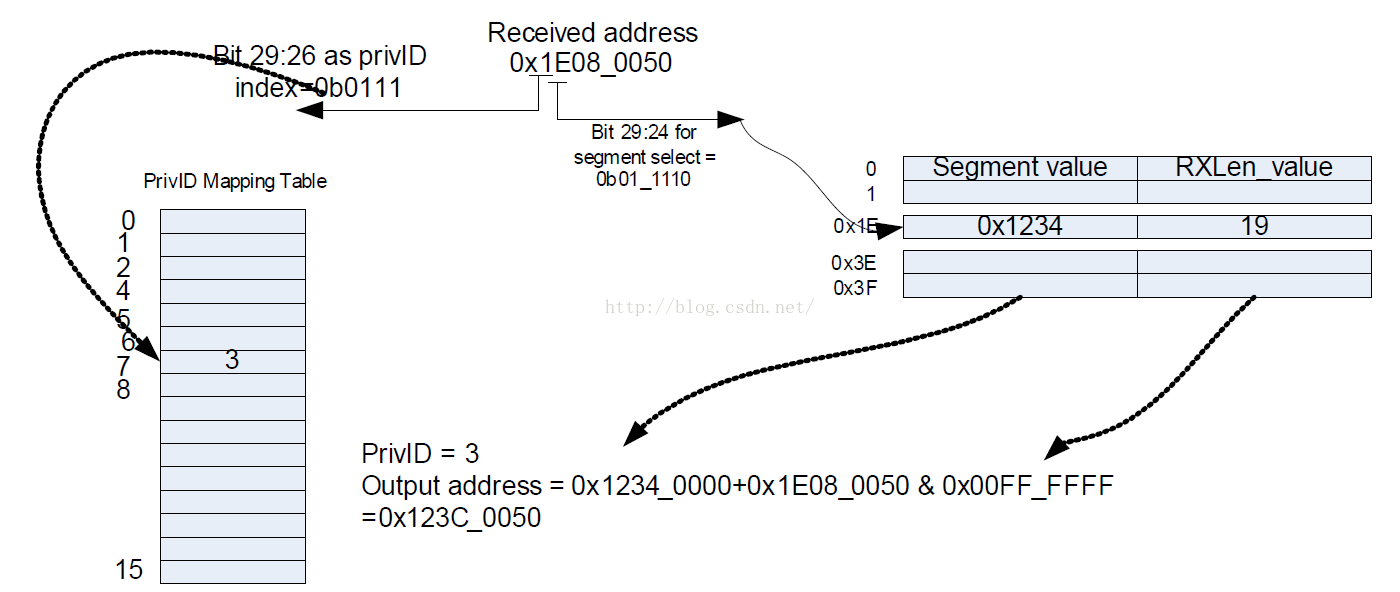

Rx地址部分就比较复杂,h模块有一个PrivID的表,表中有16个值,每一个入口值都可以配置4位的privID,根据包的这个值,来决定进来的数据包的映射关系。

privID的两个寄存器,一个是序列寄存器一个是数据寄存器,都是32位的,但是只有4位有用,其于都是写0.检查的时候,要先写index寄存器,再读value寄存器。

接收端的地址重映射,主要是依赖一个段和长度的表从而决定映射的地址。OFFSET_MASK使一个便宜掩码,用来地址重映射,一共有16个,而表有64个入口,每一个入口都可以被独立编程,映射一片地址。

RX端的地址等效于:Segment Address + (Rx Address& OFFSET_MASK),其中segment address的31:16来自RXSEG_VAL的segment/length表。,0:15位均为0.每一个segment的大小可以从512B到256M,且必须是64KB边界对齐的。

一个发送地址的打包过程,手册自带的例子,地址转换。

这是接收的过程,手册自带的例子,可以参考。

一个包最大可以是256BYTES,但是读写都是被拆分成64B的。

5.中断

64个中断事件。HW_EVENT必须被单独配置,步骤如下:

写中断控制索引寄存器baseaddress+0x64,用十进制数写

INTEN,使能位

SIEN,软件是否可以出发中断

INTTYPE: 电平触发还是脉冲触发,只能设置为0,根时钟有关系

INTPOL:极性选择,是高电平触发还是低电平触发。

ISEC:如果置1,只有安全主机才能触发软件中断事件。

DNID:未使用,写0.

MPS:用来发送中断数据包给远程设备,只有3LSB有效,高MSB全部为0.

VECTOR:当INT2CFG置1,那么HW_EVENT[x],就表示哪一位中断需要挂起。如果INT2CFG设为0,那么HW_EVENT[x],就表示指向的中断就开始发送包到远程设备withMPS和vector域。vector很重要,可以用来表明哪一位远程寄存器需要挂起,或者用作获取中断地址的索引,根据远端设备的int2cfg的设置。

获取中断控制寄存器的值得方法:向中断控制寄存器相关的寄存器写数值,然后从往后便宜0x04的地方读出来。中断一共有0~63个,期中0-31是来自芯片级的中断,32-64是来自QM模块等待队列的中断信号。当IINTPOL写0,队列不为空的状态就触发中断,当写1,空队列触发一个中断。软件中断写SW_INT寄存器。

756

756

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?