#define APLL_LOCK (*((volatile unsigned long *)0x7E00F000))

#define MPLL_LOCK (*((volatile unsigned long *)0x7E00F004))

#define EPLL_LOCK (*((volatile unsigned long *)0x7E00F008))

#define OTHERS (*((volatile unsigned long *)0x7e00f900))

#define CLK_DIV0 (*((volatile unsigned long *)0x7E00F020))

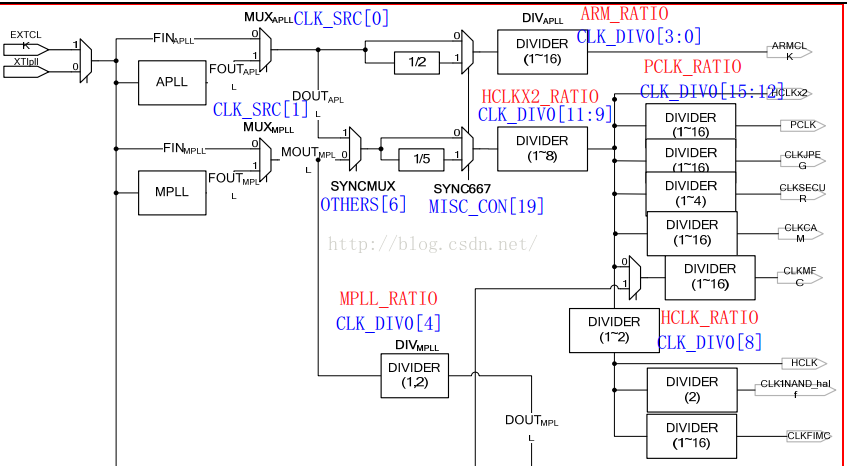

#define ARM_RATIO 0 /* ARMCLK = DOUTAPLL / (ARM_RATIO + 1) */

#define HCLKX2_RATIO 4 /* HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1) = 100MHz */

#define HCLK_RATIO 0 /* HCLK = HCLKX2 / (HCLK_RATIO + 1) = 100MHz */

#define PCLK_RATIO 1 /* PCLK = HCLKX2 / (PCLK_RATIO + 1) = 50MHz */

#define MPLL_RATIO 0 /* DOUTMPLL = MOUTMPLL / (MPLL_RATIO + 1) */

#define APLL_CON (*((volatile unsigned long *)0x7E00F00C))

#define APLL_CON_VAL ((1<<31) | (250 << 16) | (3 << 8) | (1)) /* FOUT_APLL=500MHz*/

#define MPLL_CON (*((volatile unsigned long *)0x7E00F010))

#define MPLL_CON_VAL ((1<<31) | (250 << 16) | (3 << 8) | (1)) /* FOUT_MPLL=500MHz*/

#define CLK_SRC (*((volatile unsigned long *)0x7E00F01C))

void clock_init(void)

{

APLL_LOCK = 0xffff;

MPLL_LOCK = 0xffff;

EPLL_LOCK = 0xffff;

/* set async mode 当CPU时钟 != HCLK时,要设为异步模式 */

OTHERS &= ~0xc0;

while ((OTHERS & 0xf00) != 0);

CLK_DIV0 = (ARM_RATIO) | (MPLL_RATIO << 4) | (HCLK_RATIO << 8) | (HCLKX2_RATIO << 9) | (PCLK_RATIO << 12);

APLL_CON = APLL_CON_VAL; /* 500MHz */

MPLL_CON = MPLL_CON_VAL; /* 500MHz */

CLK_SRC = 0x03;

}

配置过程参考下图,从右向左配置。

1. 配置同步模式,异步模式主要用于ARMCLK=667MHz时的配置。

当APLL_OUT=667MHZ时 ARMCLK:HCLKx2:HCLK=1:2.5:5

当APLL_OUT为533MHZ或以下时,只需保证ARMCLK=n*HCLK即可。

The clock ratio between ARMCLK and HCLK must be integer to use synchronous interface between ARM core

and AXI bus interface. S3C6410X does not have any limitation up to 533MHz synchronous interface, i.e.,

ARMCLK = 533MHz, HCLKX2= 266MHz, HCLK = 133MHz. However, there is some constraints over 533MHz,

typically 667MHz interface. The supported clock ratio is only 1:2.5:5 (ARMCLK = 667MHz, HCLKX2=266MHz,

HCLK = 133MHz).

2.配置CLK_DIV0寄存中的各种分频系数,注意HCLK与PCLK的频率必须是偶数分频。

3.配置APLL_CON&MPLL_CON,使能PLL并设置分频系数。

4. 配置CLK_SRC,选择PLL输出频率作为后续分频的输入。

关于OK6410的一些频率参数:

ARMCLK最大667MHz

HCLKx2最大266MHz,为DDR0&DDR1提供时钟

HCLK最大133MHz

PCLK最大66MHz

4.关于Lock time的说明

PLL输入时钟变化或者分频系数变化后,需要一段时间锁定频率,这段时间内,输出一直是0.锁定时间单位是输入时钟周期。

A PLL requires locking period when input frequency is changed or frequency division (multiplication) values are

changed. PLL_LOCK register specifies this locking period, which is based on PLL’s source clock. During this

period, output will be masked ‘0’ 。

8811

8811

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?