4、PCB 简要设计

关于对原理图或者说是对整个项目的编译,这一步是为生成网络表,做准备工作,在 project,project options 中打开下图

4.1 DRC 规则

对于电气规则方面,我在网上搜索了些注解,以供参考:

Violations Associated with Buses 有关总线电气错误的各类型(共 12 项)

bus indices out of range 总线分支索引超出范围

Bus range syntax errors 总线范围的语法错误

Illegal bus range values 非法的总线范围值

Illegal bus definitions 定义的总线非法

Mismatched bus label ordering 总线分支网络标号错误排序

Mismatched bus/wire object on wire/bus 总线 / 导线错误的连接导线 / 总线

Mismatched bus widths 总线宽度错误

Mismatched bus section index ordering 总线范围值表达错误

Mismatched electrical types on bus 总线上错误的电气类型

Mismatched generics on bus (first index) 总线范围值的首位错误

Mismatched generics on bus (second index) 总线范围值末位错误

D: violations associated with nets 有关网络电气错误(共 19 项)

adding hidden net to sheet 原理图中出现隐藏网络

adding items from hidden net to net 在隐藏网络中添加对象到已有网络中

auto-assigned ports to device pins 自动分配端口到设备引脚

duplicate nets 原理图中出现重名的网络

floating net labels 原理图中有悬空的网络标签

global power-objects scope changes 全局的电源符号错误

net parameters with no name 网络属性中缺少名称

net parameters with no value 网络属性中缺少赋值

nets containing floating input pins 网络包括悬空的输入引脚

nets with multiple names 同一个网络被附加多个网络名

nets with no driving source 网络中无驱动源

nets with only one pin 网络只连接一个引脚

nets with possible connection problems 网络可能有连接上的错误

signals with multiple drivers 重复的驱动信号

sheets containing duplicate ports 原理图中包含重复的端口

signals with load 信号无负载

signals with drivers 信号无驱动

unconnected objects in net 网络中的元件出现未连接对象

unconnected wires 原理图中有没连接的导线

E:Violations associated with others 有关原理图的各种类型的错误 (3 项 )

1、No Error 无错误

2、Object not completely within sheet boundaries 原理图中的对象超出了图纸边框

3、Off-grid object 原理图中的对象不在格点位置

F:Violations associated with parameters 有关参数错误的各种类型

1、same parameter containing different types 相同的参数出现在不同的模型中

2、same parameter containing different values 相同的参数出现了不同的取值

Ⅱ、Comparator 规则比较

A:Differences associated with components 原理图和 PCB 上有关的不同 ( 共 16 项 )

◆ Changed channel class name 通道类名称变化

◆ Changed component class name 元件类名称变化

◆ Changed net class name 网络类名称变化

◆ Changed room definitions 区域定义的变化

◆ Changed Rule 设计规则的变化

◆ Channel classes with extra members 通道类出现了多余的成员

◆ Component classes with extra members 元件类出现了多余的成员

◆ Difference component 元件出现不同的描述

◆ Different designators 元件标示的改变

◆ Different library references 出现不同的元件参考库

◆ Different types 出现不同的标准

◆ Different footprints 元件封装的改变

◆ Extra channel classes 多余的通道类

◆ Extra component classes 多余的元件类

◆ Extra component 多余的元件

◆ Extra room definitions 多余的区域定义

B:Differences associated with nets 原理图和 PCB 上有关网络不同(共 6 项)

◆ Changed net name 网络名称出现改变

◆ Extra net classes 出现多余的网络类

◆ Extra nets 出现多余的网络

◆ Extra pins in nets 网络中出现多余的管脚

◆ Extra rules 网络中出现多余的设计规则

◆ Net class with Extra members 网络中出现多余的成员

C:Differences associated with parameters 原理图和 PCB 上有关的参数不同(共 3 项)

◆ Changed parameter types 改变参数类型

◆ Changed parameter value 改变参数的取值

◆ Object with extra parameter 对象出现多余的参数

这些规则设置有利与查找你在绘制 原理图时出现的问题,同时建议提高必要的规则等级,例如在violations associated with nets 这个项目栏内,floating net labels 原理图中有悬空的网络标签这项改为 error,这样在你放置网络标号时如果没有放置到电气栅格上时,会自动报警出现提示,有利于发现我们的错误。

对于规则部分,只有不断的编译,查错,随经验的积累,你会调整出自己认为完备的格式。

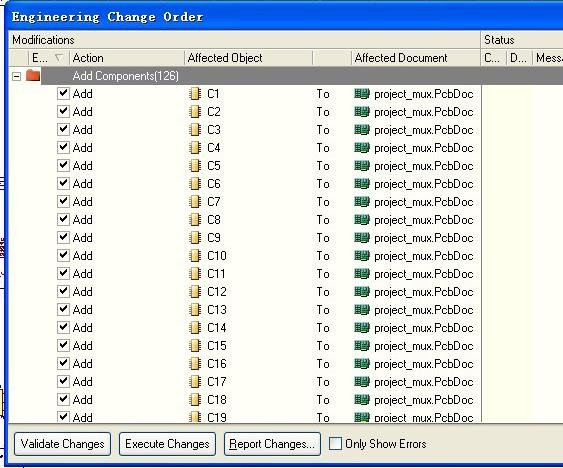

接下来就是对原理图的 DRC 测试,快捷键位 C+C,project 菜单的第一项即使,如果页面没有弹出 Message 的内容,可在右下角,System 中找到 Message,查阅编译信息,完成编译后将数据导入到 PCB 环境中,在菜单中 Design 选项中执行 Updata PCB document to ***.PcbDoc 中,显示下图

编译过程显示上图

将 only show Error 打钩,显示下图,主要是因为元器件 J1 没有封装,回到原理图,用快捷键 J+C 找到元件,双击元件,在 footprint 中添加相应的封装,

4.3 编译中出现错误,缺少封装

再次执行 Updata PCB document to ***.PcbDoc 中,显示下图,可以看到的是图中的 ERRORy已经没有。

4.4 添加封装重新导入

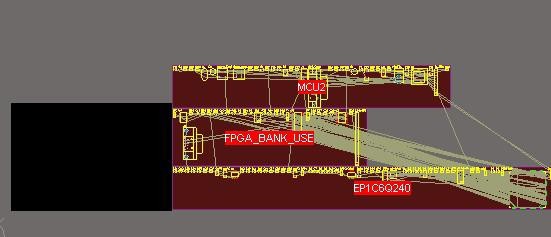

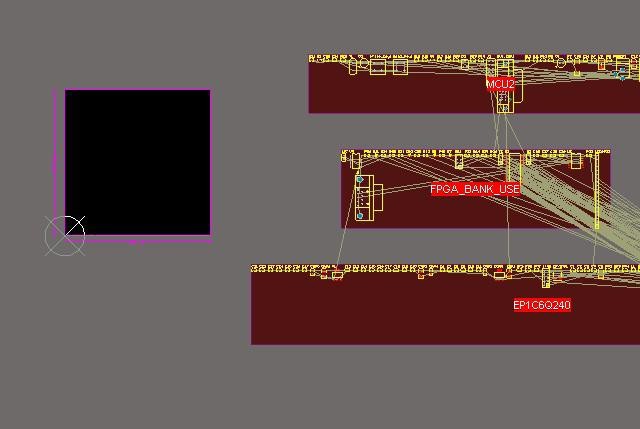

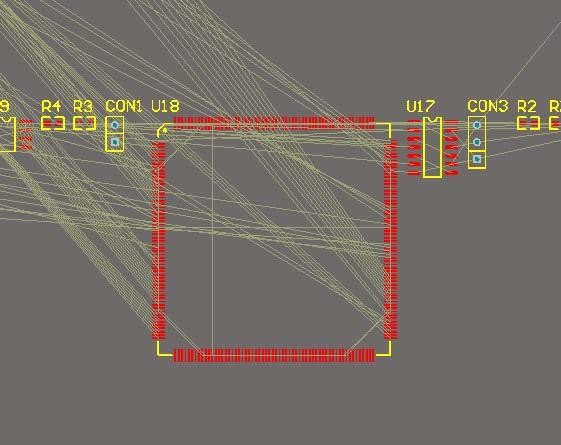

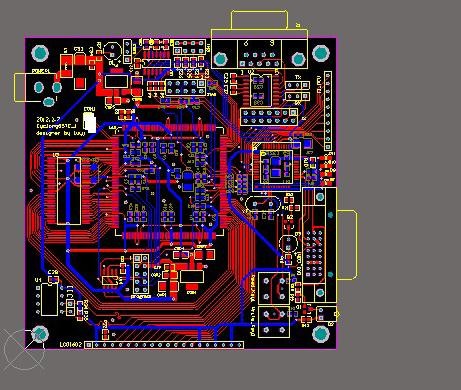

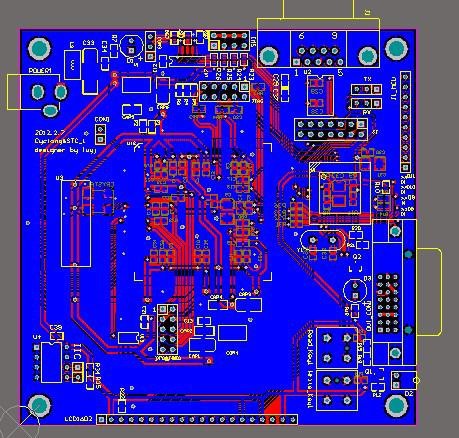

在 pcb 中会显示下图,可以看到不同 room 中,已经导入了相应的元件,接下来就是对 PCBh环境中的规则设置。

4.5 完成导入

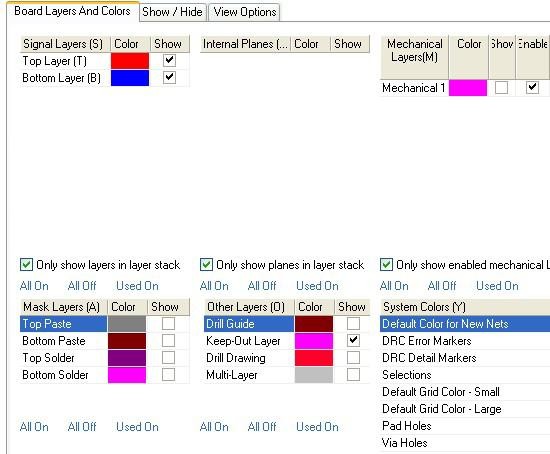

单击键盘 L 键弹出如图对话框,你可以去掉一些不必要的显示,以及修改相应的颜色,如Drill Guide 层显示,Drill Drawing 层显示。去掉的方法就是将 show 对应的对号去掉。

4.6 关于操作层的显示

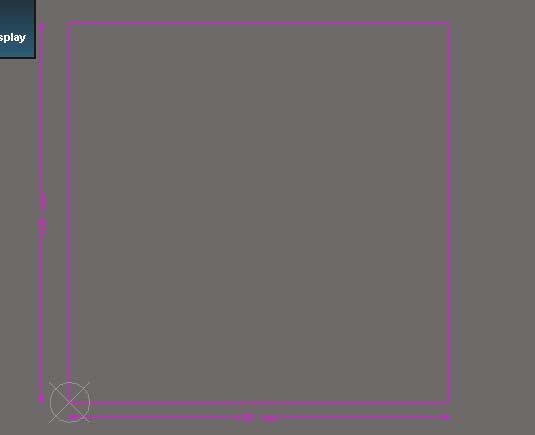

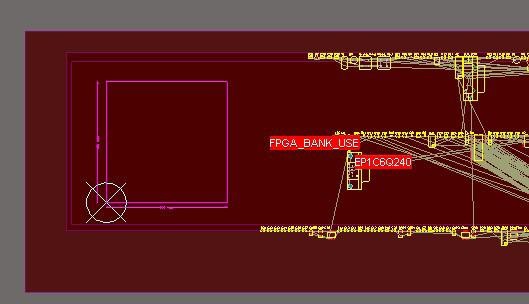

设置 PCB 板子的边界,在这一步,主要是为了每次启动 AD10 软件,可以将原件直接显示在中央,我主要介绍下快捷键操作,E+O+S 是坐标原点的设置(将输入法切换在英文格式),将 PCB 层切换在 Keep-out layer(切换方法,一种是小键盘区的 * 键,一种是用鼠标单击工作窗口的 Keep-out layer), 接着绘制边框,快捷键 P+L,绘制,完了放置尺寸标注。放置尺寸标注的方法有多种,这里说最直接的方法,P+D+D 快捷键,然后就从边框端点绘制。完成如下图,

4.7 工作区域的设置

接着用快捷键 D+S+R 绘制 pcb 的编辑环境,沿着左边原点绘制边界线,这样就生成下图的,黑色的就是将来放置原件和布线的区域,当然可以将这个区域绘制成任何希望的形状,在绘制过程中用 Shift + 空格在控制边界形状,如果要绘制圆形,以及镂空部分 PCB 工作区,则直接在 Keep-out layer 工作层绘制闭合区域,将来在机械加工的时候,PCB 板中闭合的区域就可以被切割掉,当然在机械层做这样的处理更为合理,但是好多加工厂建议之间在 Keep-out layer 绘制镂空去,这和最终的 GERBER 文件生成有关,可以减少层数,成本低,效率会高些。

鼠标拖动 room 将原件移动到工作区域附近。

4.8 移动 room

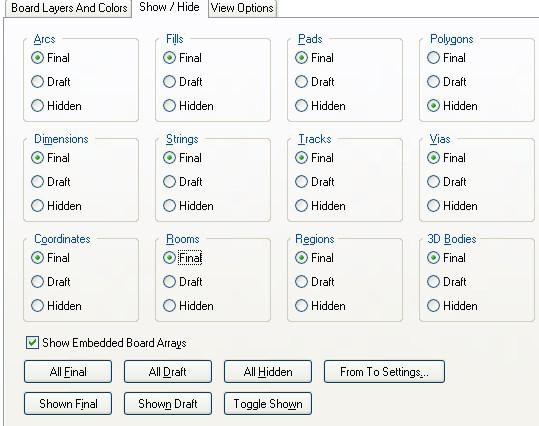

接下来谈谈对 room,有的绘图直接将 room 删掉,个人习惯吧,我常将 room 放大,使其涵盖工作的编辑区,然后将其隐藏,在需要的时候再将其显示出来,对与 room 的隐藏,快捷键 L,单击 Show/Hide ,然后弹出下图(截图为其局部)。常用的如 Polygons,strings,room,这些

4.9 部分元素的显示和隐藏

4.10 拖动后的 room 将编辑区包涵在内

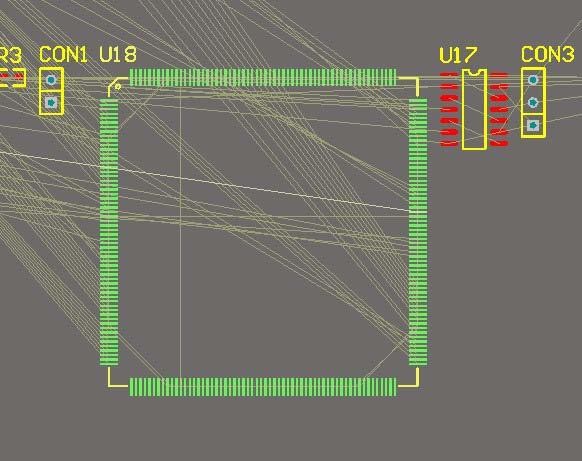

在原件 pin 间距小于默认值,会出现绿色的警告,这就引出了关于 PCB 布局布线的规则设置问题。

4.11 电气规则错误报警

PCB 规则的设置,在约束是 PCB 布局布线起着很重要的作用,不同的行业规则也是有很大差异的,虽然都是电子,但对于电源设计,高频信号设计等规则也是不同的。

PCB 中的规则设置在布局布线的前,需要对一些设计做具体的规则约束,想元件间间距,导线宽度,铺铜连接方法等

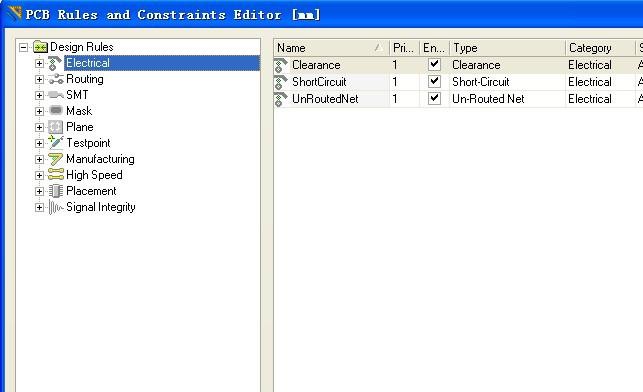

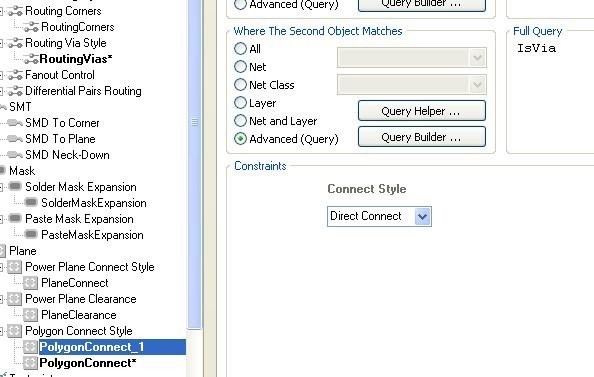

4.12 电气规则设置

4.2 布线规则设置与验证

在这里新添加 Clearance_1 规则,添加方法在 Clerance 中右击,点击 New rule,在右边的方框里点击 Advanced 接着点击 Query Helper,找到 IsRegion,添加,也可以直接输入,这项是设置关于铺铜的与元件,导线间的间距,当铺的为网格通,IsRegion 不能起到约束作用,需要填写 InPoly。

4.13 间距设置

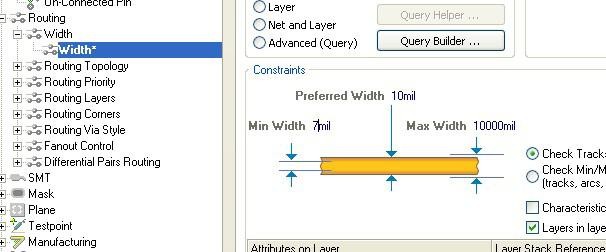

在布线时,不同的信号线的宽度不一样的,同时与 板子铜箔的厚度有关,通常为盎司来,0.5盎司的厚度的铜箔,40mil 走的电流为约 1A,

4.14 线宽范围设置

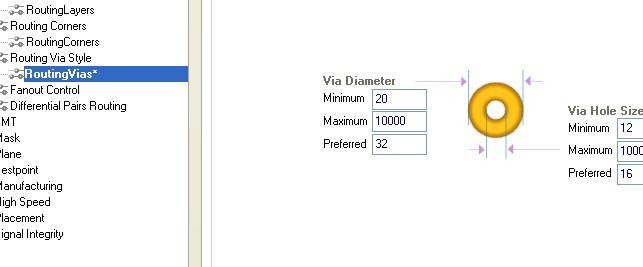

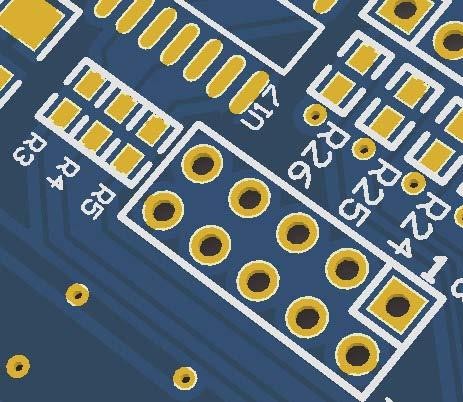

对于过孔,通常内外径之差不要小于 8mil,过小不利于加工处理,通常为 12*20,12*24,16*32,28*50 等,必要时可以做的更大,

4.15 过孔设置

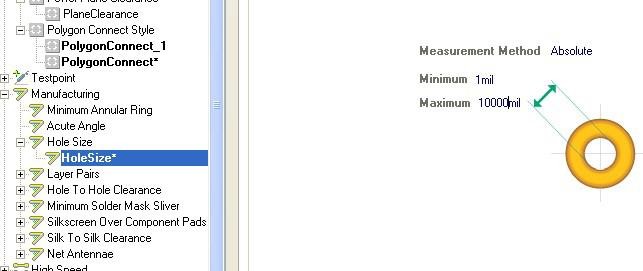

4.16 机械空的设置

4.17 过孔铺铜的连接,选取的 Dircet Connnect

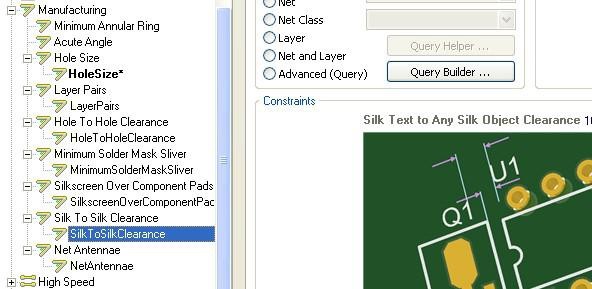

4.18 器件丝印间距

4.19 元件间的高度

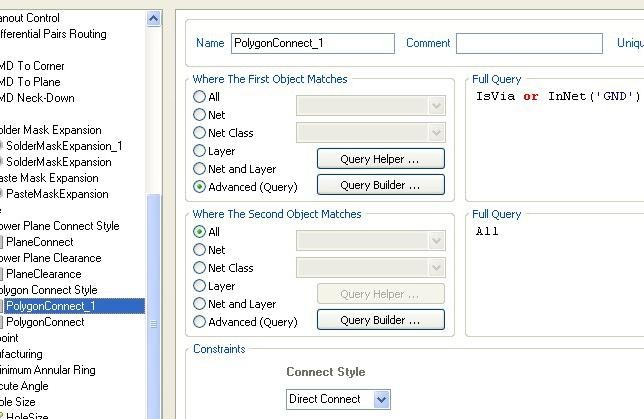

以上为一些基本的设置,当然对于一些特殊的,需要进行特殊的设置,比如对于某些管脚需要直接连接,或者某些网络需要保持特殊的间距,这时候需要添加特殊规则,其实这些规则仅仅是个指令,例如将 GND,添加在为直接连接,如下图 4.20。在类似的我们可以将做更多灵活的设定。

4.20 添加 InNet('GND')

4.21 完成设置后保存,警告消除

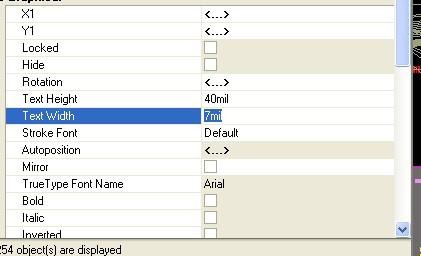

接下来说下全局修改,这也是一个很实用的方法,例如我们想把整体的丝印改为自己需要的大小,将某一类焊盘加大,或者对所有过孔盖油,而且这种方法同样实用与原理图设计,在原理图设计中如果有混合的 GND,AGND,DGND,如果有隐藏,可以通过这个全局让其显示,总之是个很方便的操作。下面以丝印为例

点击丝印,鼠标右击,Find Similar Objects 其中,

4.22 Texl Height 60mil same

4.23 修改 Texl Height 40mil width7mil,

点解键盘 Enter,完成操作,如果丝印未修改,就去查看你在这个操着过程中,是否漏掉选项,select matched 选项打勾才行的。

4.24 select matched

在放置元件时,有时候双面都要放元件,或者方向需要改变的时候,双击元件见 4.25 修改 Layer,顶层或者底层,Rotation,元件的方向设置

4.25 元件方向,层的设置

4.26 设置后的元件,注意丝印的位置需要整理

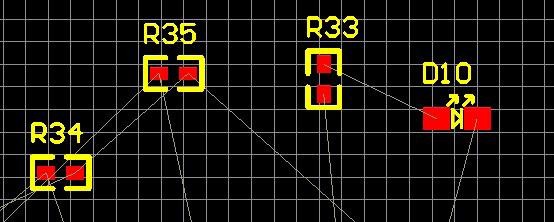

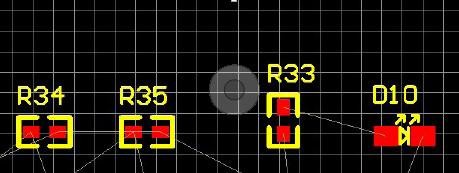

调整前的元件,如图 4.27 快捷键 A+A

4.27 元件任意位置

4.28 设置需要对齐的方向,Bottom

4.29 底边对齐

在布局完成后就是布线,布线注意线宽,以及过孔,常用 * 来改变布线层,并放置过孔,在放置过程中按 Tab 键,修改线宽,过孔的大小,对于一些布线规则,会在最后补充加以详细说明

添加泪滴 T+E

4.30 add tear

快捷键 P+G 显示铺铜,铺铜有实体铜和网格通,当板子受热不均,用网格,常用的还是实体铜,网格可以防范受热不均鼓起的现象,Solid 实体的,Hatched 网格,网路名和层这个根据需要设置连接网络,Conncet to Net , 将相同的铜连一起同时去掉死铜,Pour Over All same Net Objects选取 Remove Dead Copper,

4.31 铺铜

铺铜前后对比

4.32 铜层显示

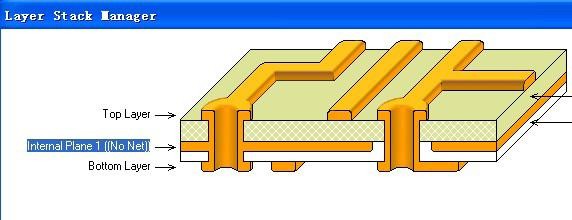

4.3 关于内电层

图为添加内电层

概念:正片和负片是底片的两种不同类型。

正片:简单地说就是,在底片上看到什么就有什么。

负片:正好相反,看到的就是没有的,看不到的就是有的。

正片:优点是所见所的,有比较完善的 DRC 检查。

正片:一般是我们讲的 pattern 制程 , 其使用的药液为碱性蚀刻正片若以底片来看 , 要的线路或铜面是黑色的 , 而不要部份则为透明的 , 同样地经过线路制程曝光后 , 透明部份因干膜阻剂受光照而起化学作用硬化 , 接下来的显影制程会把没有硬化的干膜冲掉 ,*****接着是镀锡铅的制程 , 把锡铅镀在前一制程 ( 显影 ) 干膜冲掉的铜面上 , 然后作去膜的动作 ( 去除因光照而硬化的干膜 )*****, 而在下一制程蚀刻中 , 用碱性药水咬掉没有锡铅保护的铜箔 ( 底片透明的部份 ), 剩下的就是我们要的线路 ( 底片黑色的部份 )…--> 下制程

负片:一般是我们讲的 tenting 制程 , 其使用的药液为酸性蚀刻,负片是因为底片制作出来后 , 要的线路或铜面是透明的 , 而不要的部份则为黑色的 , 经过线路制程曝光后 , 透明部份因干膜阻剂受光照而起化学作用硬化 , 接下来的显影制程会把没有硬化的干膜冲掉 ,于是在蚀刻制程中仅咬蚀干膜冲掉部份的铜箔 ( 底片黑色的部份 ), 而保留干膜未被冲掉属于我们要的线路 ( 底片透明的部份 )…--> 下制程

添加后的用快捷键 L,可以看到内电层

在实际布线上,电源层使用负片,会带来很多便捷,但是有的公司会要求电源层也用正片来处理,因为负片在的逻辑与平时布线相反,如果没有划分好负片网络很可能出现死铜,这对整个板子信号会带来影响的。尤其是电源层出现多个电源,在整个板子有 1,2V,2.5V,3.3V,5V 数模混合电源,容易导致电源分割失误、在分割时采用 P+L 划分不同网络的区域。

4.4 3D 试图观察,快捷键 2,3 分别进入 2 维和 3 维,之间进行切换

4.33 3D 图

图形方法,查看丝印是否与焊盘重叠,一旦重叠,生产出来后影响焊接,放大方法用 PgUp 键,或者滚轮,

4.34 放大 3D 图

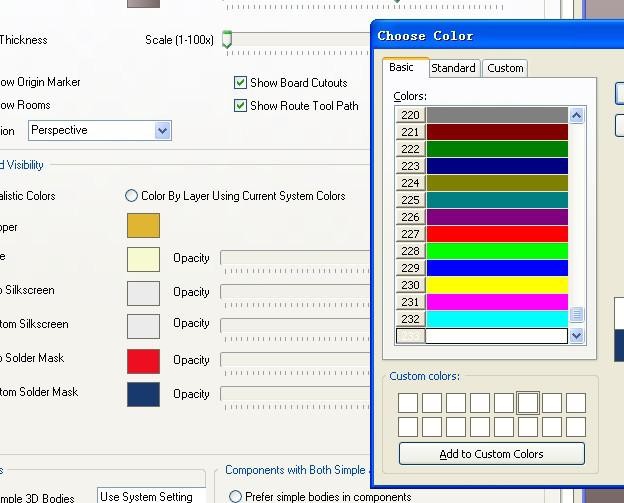

在查看过程中点击 L 键可以修改层的颜色,

4.35 图层颜色修改

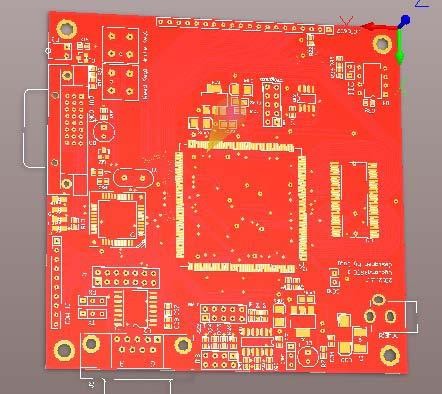

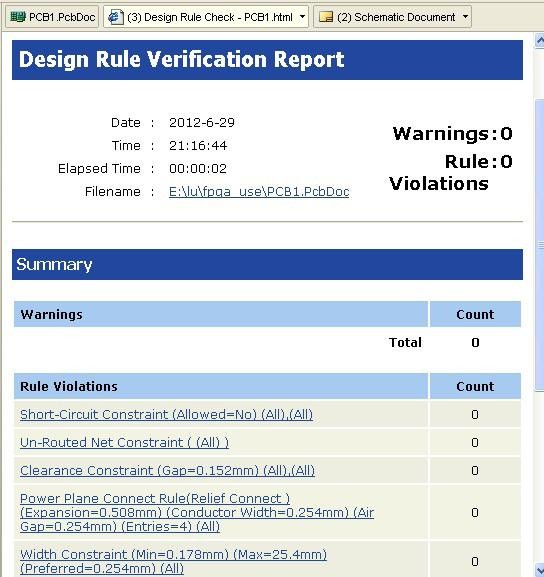

快捷键 T+D+R 设计规则测试,测试后显示为下图,表明元件连接正常。如果有错误,需要修改,知道完成。需要说明的是,这一步的操作可以放在调制丝印前进行。

4.36 完成规则测试

4.5 手动布线的常识

首先补充下关于电路板层次的知识

下面的这些摘自网络,网络也是个学习的资源、这里讲的是 protel99 的,altium 之是其升级版而已。

一、Signal Layers( 信号层 )

Protel99 提供了 16 个信号层:Top (顶层)、Bottom(底层)和 Mid1-Mid14(14 个中间层)。

信号层就是用来完成印制电路板铜箔走线的布线层。在设计双面板时,一般只使用 Top(顶层)和 Bottom(底层)两层,当印制电路板层数超过 4 层时,就需要使用 Mid(中间布线层)。

二、Internal Planes( 内部电源 / 接地层 )

Protel99 提供了 Plane1-Plane4(4 个内部电源 / 接地层)。内部电源 / 接地层主要用于 4 层以上印制电路板作为电源和接地专用布线层,双面板不需要使用。

三、Mechanical Layers( 机械层 )

机械层一般用来绘制印制电路板的边框(边界),通常只需使用一个机械层。有 Mech1- Mech4(4 个机械层)。

四、Drkll Layers( 钻孔位置层 )

共有 2 层:“Drill Drawing”和“Drill Guide”。用于绘制钻孔孔径和孔的定位。

五、Solder Mask( 阻焊层 )

共有 2 层:Top(顶层)和 Bottom(底层)。阻焊层上绘制的时印制电路板上的焊盘和过孔周围的保护区域。

六、Paste Mask( 锡膏防护层 )

nbsp; 共有 2 层:Top(顶层)和 Bottom(底层)。锡膏防护层主要用于有表面贴元器件的印制电路板,这时表帖元器件的安装工艺所需要的,无表帖元器件时不需要使用该层。

七、Silkscreen( 丝印层 )

共有 2 层:Top(顶层)和 Bottom(底层)。丝印层主要用于绘制文字说明和图形说明,如元器件的外形轮廓、标号和参数等。

八、Other( 其它层 )

共有 8 层:“Keep Out(禁止布线层)”、“Multi Layer(设置多层面)”、“Connect(连 接层)”“DRC Error(错误层)”、2 个“Visible Grid(可视网格层)”“Pad Holes(焊盘孔层)”和“Via Holes(过孔孔层)”。其中有些层是系统自己使用的如 Visible Grid(可视网格层)就是为了设计者在绘图时便于定位。而 Keep Put(禁止布线层)是在自动布线时使用,手工布线不需要使用。

对于手工绘制双面印制电路板来说,使用最多的是 Top Layers(顶层铜箔布线)、Bottom Layers(底层铜箔布线)和 Top Silkscreen(顶层丝引层)。每一个图层都可以选择一个自己习惯的颜色,一般顶层用红色、底层用蓝色、文字及符号用绿色或白色、焊盘和过孔用黄色

对于整个电路板,EMC 和 EMI 在很大程度上受元件的布局影响,大的公司有专门的PLAYOUT ENGINEER,作为普通的电子工程师,在方面的也应该充分重视,对于布局布线,规则太多了,不同的板子,高速信号射频板,与大功率电源板,以及模拟板,数字板,混合信号板,都是有很大差异的。对于这方面的网上有大量的总结,很值得借鉴。

对于电源部分的处理

为降低电源噪声的影响,对电源有时会加差模抑制和共模抑制的扼流圈,当然 TVS 抑制,RC滤波都有的,在布局是大多时候靠近接线端子,布线尽量宽,同时减少地的绕行。平时保证余量的情况下,40mil 走 1A 的电流,当然了,线的标准时按 0.5 盎司 / 英寸来估算的,具体的须参照实际设计的材质。

电源回路问题

对于信号的传导,大体上分两个路径,一个是沿实际连线,另一个是辐射,而构成回路时,信号沿着阻抗最低的路径返回,而不是阻值最低,而阻抗最经,路径最短,这样,信号有时出现绕行,而绕行时即会干扰别的信号,如果绕行路径不当,也会被别的信号干扰,总是EMC 是 PCB 布局布线经常讨论的话题。

对于线宽,线间距

对于线宽,首先是了解加工工艺的最小宽度,避免自己设计的 PCB 无法加工,通常用到的为10mil,基本上都大于 4mil,而电源部分,情况允许就用单独的电源层进行设计,独立的电源地层为信号提供很好的返回路径。对于线建议,一般的 3w,5w 原则,w 指的是导线宽度。3w 可以降低相邻信号 70% 的串扰吧,实际也没做过测试,当然,对于高速信号,线间距还是有要求的,

对于差分对信号

对于查分信号,有时需要控制阻抗,这样,查分走线宽度和正负信号之间的间距也可以用软件计算的得出,同时,差分对于差分对之间的间距也尽量大于 3 倍以上的差分对间距,差分对之间相互抵消,降低的是差模干扰,对外的主要是共模干扰。

对模数字信号

模拟信号算是敏感信号,而数字信号抗干扰能力相对强些,在同一块 PCB 上布局时,将数模分开,降低数字信号对模拟信号的干扰,有时会用到隔离电路,降低数模信号之间的串扰。

总之,对于高电压,电路板需要开槽,加大爬电距离等。对于不同行业的 PCB 设计都有不同的规定,这里只是类举,感兴趣了可以在网上搜相关信息,还是很多

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?