摘 要

本报告给出一个基于FPGA+两片DDR2组成的核心板、带有4路视频输入和VGA接口的开发板进行的视频图像采集和处理系统的设计。使用TW2867进行视频输入信号的编码,存储到DDR2中,通过FPGA和ARM的联合控制,通过I2C总线进行通信,进行数字图像处理,实现了单通道视频信号输入屏幕显示、4通过视频信号输入4分屏显示、边沿检测算法,将处理结果通过VGA接口连接到LCD显示器上进行显示。本报告从硬件设计和软件设计两个方面对该基于FPGA的视频图像处理系统的工作过程做了详尽描述。

关键词:视频图像处理、FPGA、边沿检测、4分屏显示

1、设计目的

图像处理技术和机器视觉作为一门前沿的技术,为人们的生活和工作带来了极大的便利和愉悦。由于视频信号的数据量大,信号较为复杂,这就要求视频信号处理系统具有实时采集、大容量存储和实时处理的特点。本报告提出基于现场可编程门阵列FPGA的视频图像采集与处理系统设计方案,利用FPGA并行处理快速的特点,辅以图像处理算法,用以获得不同需求的视频图像,并通过VGA显示器进行实时显示。

2、设计任务与性能指标

本系统中主要是通过AV接口实现视频图像采集,将采集到的4路模拟电视信号进行格式编码转换成数字信号,存储在DDR2中作为缓存,供FPGA处理器进行数字图像的处理,处理的结果再通过视频编码芯片转换为模拟电视信号通过VGA接口完成基于LCD显示器的4分屏视频图像显示功能,在图像处理中完成边缘检测算法的实现。

3、系统总体设计与工作原理

本系统由视频图像采集模块、存储模块、显示模块以及相关配置电路模块组成。采集模块通过视频通过解码芯片TW2867将通过AV接口连接的摄像头拍摄到的视频模拟信号转变为ITU-RBT656格式的数字视频信号;存储模块选取解码后的一帧图像数据的有效大小存入DDR2存储器中,在处理进行前和处理进行中,作为未得到处理的图像数据信息的缓存;显示模块从存储器中读出图像数据,再通过视频编码芯片ADV7123视频D/A转换芯片进行格式转换输出模拟信号,通过VGA接口在LCD液晶显示器上进行显示处理后的效果和采集显示的视频信息。

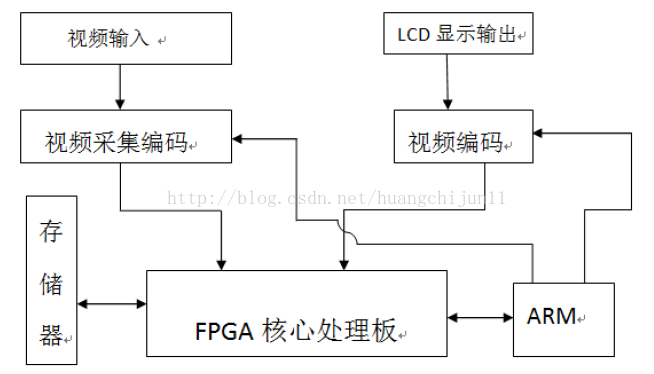

在原理框图1中可以看到有4路视频输入信号,选择4路输入信号是因为要实现4分屏分割显示4路摄像头采集到的信息,因为摄像头硬件资源的欠缺,只使用了两个摄像头但是原理是完成实现了,只要安装够4个视频输入就一定可以显示4路视频信息。

图1系统设计原理

3 . 1 系统硬件设计

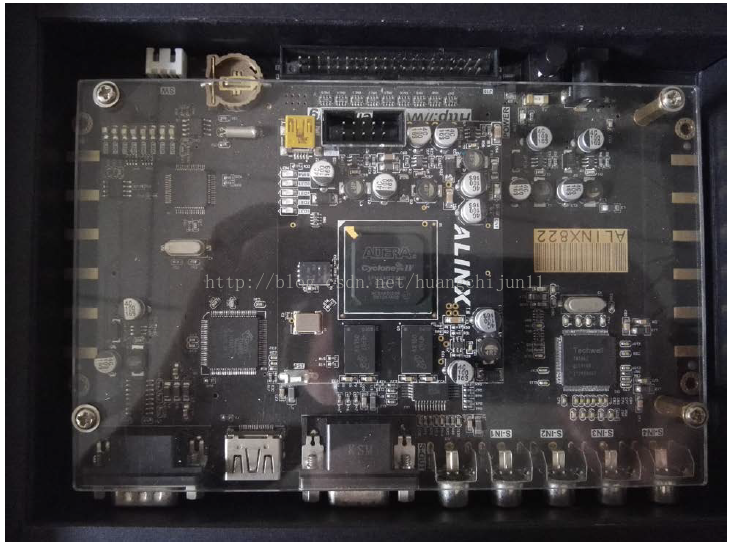

因为本系统设计是基于黑金动力社区的FPGA视频处理开发平台实验板进行的,因此所使用的硬件电路也是该开发板上搭载的实验器件,均是已经较为成熟的视频图像采集与处理硬件设备。实验板型号为ALINX822 REV3.0,在该实验板上整个开发板的结构继承了一贯的核心板和扩展板的模式进行设计的。核心板主要由FPGA+两片DDR2构成,承担视频图像处理的核心算法,充分利用了FPGA并行处理的能力,加上两片DDR2构成32bit总线,整个系统的带宽高达10Gb/s,两片DDR2容量高达2Gbit,满足视频处理过程中对高缓冲区的需求。该实验板选用的FPGA为ALTERA公司CYCLONE IV系列中速度级别最高的C6级别,可以实现FPGA和DDR2之间的时钟频率达到200M,DDR2内部400M,充分满足了四路1080P视频处理的需求。

图2开发板实物图

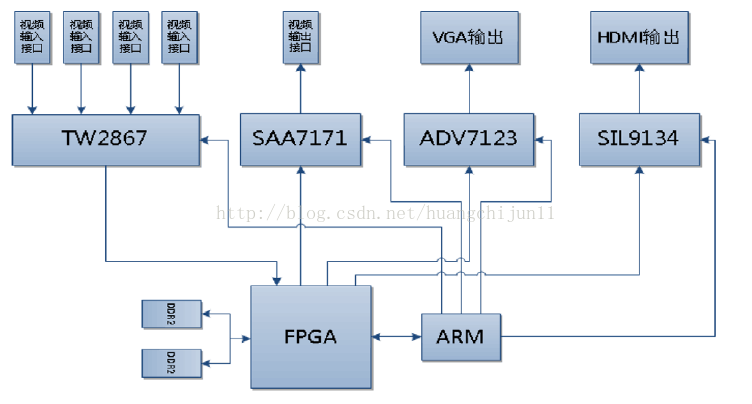

上图2是使用的开发板的实物图,从上面可以看到其实验板的型号,搭载的器件的一些型号信息,中间的即为核心板,核心板下面则是一块更大面积的扩展板,扩展板上则分布着VGA接口、HDMI接口、视频输出接口、视频输入接口、ARM控制器、扩展口、SD卡槽等器件。从下图3中可以看到整个开发板的系统结构图。

图3开发板结构图

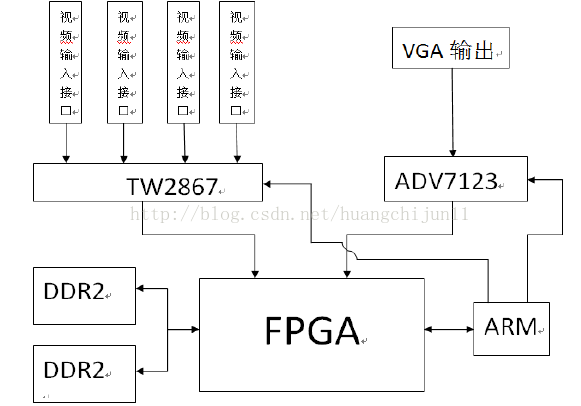

本系统所使用到的器件框架结构图在图4中可以清晰地看到,跟整个开发板结构图相比,没有使用到视频输出接口和HDMI接口,其他则都用到了。TW2867是为了将视频输入接口采集到的视频信号进行编码成数字信号,ADV7123是将经过处理后的数字信号转为模拟电视信号,以供VGA接口连接显示器进行LCD屏的显示。

图4 硬件设计原理框图

3.2单元电路设计

1,采集模块

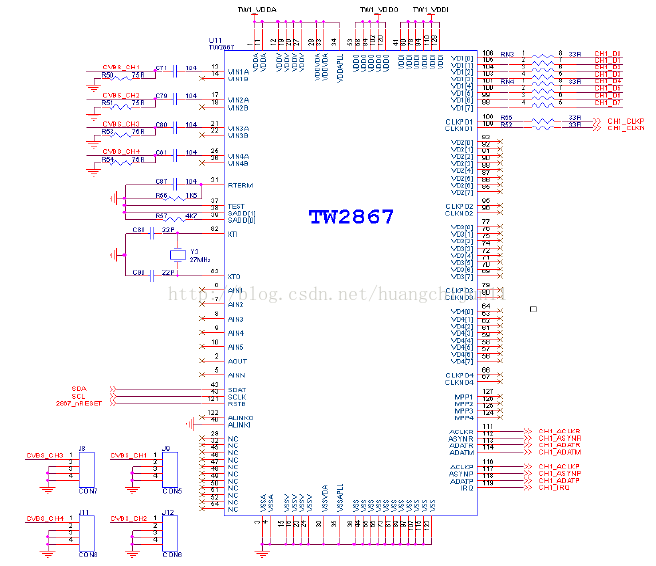

采集模块是选用了Techwell公司的TW2867,可以输入4路符合视频信号,PAL/NTSC/SECAM自动识别,输出BT656,可多路复用总线,FPGA端解复用,节省IO,其中TW2867的IIC接口和复位引脚与STM32F103相连,通过STM32F103来对TW2867进行初始化和控制操作,其他引脚与FPGA相连。在图5中,可以看到4路视频输入接口跟TW2867相连接,实现4路视频输入。

与ARM对应引脚如下表1所示:

表1 ARM引脚对应表

| 引脚名称 |

ARM引脚 |

| SDA |

39 |

| SCL |

40 |

| 2867_NRESET |

41 |

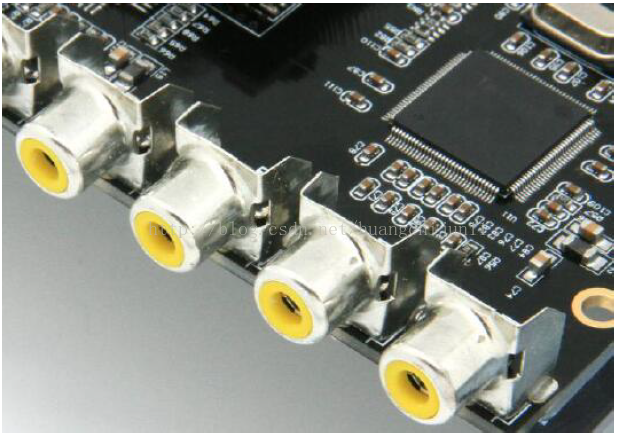

图5视频输入接口实物图

与FPGA对应引脚如下表2所示:

表2 FPGA引脚对应表

| 引脚名称 |

FPGA引脚 |

| cvbs_in_cikp |

P20 |

| cvbs_in_cikn |

N19 |

| cvbs_in_data[0] |

M19 |

| cvbs_in_data[1] |

N20 |

| cvbs_in_data[2] |

M20 |

| cvbs_in_data[3] |

T17 |

| cvbs_in_data[4] |

P17 |

| cvbs_in_data[5] |

R17 |

| cvbs_in_data[6] |

N18 |

| cvbs_in_data[7] |

N17 |

图6电路设计连接图

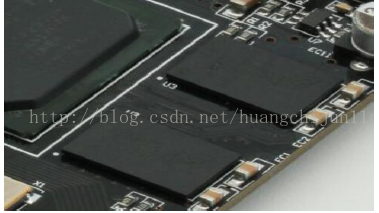

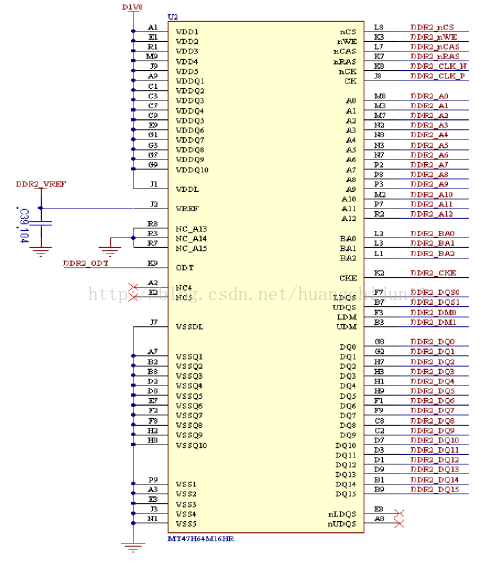

2,存储模块

本部分完成图像数据在DDR2中的帧存,为后端图像进一步处理做好准备,图像数据采集后需要进行图像处理,在处理进行前和处理进行中,未得到处理的图像数据信息需放置在帧缓存中。存储模块是使用了DDR2芯片,容量为1Gbit,两片DDR2芯片构建32bit总线模式,2G容量,带宽高达10Gb,可以满足4路1080p视频处理的需求。

图7 DDR2实物图

图8 DDR2电路图

在下表3中可以看到DDR2引脚对应表:

表3 DDR2引脚对应表

| 引脚名称 |

FPGA引脚 |

引脚名称 |

FPGA引脚 |

| mem_addr[0] |

U10 |

mem_addr[8] |

AA3 |

| mem_addr[1] |

Y6 |

mem_addr[9] |

U13 |

| mem_addr[2] |

T16 |

mem_addr[10] |

V6 |

| mem_addr[3] |

R14 |

mem_addr[11] < |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3024

3024

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?