用Verilog实现计数器

本实验使用了quartus和modelsim

- 六进制简单计数器

- 复杂计数器

六进制计数器

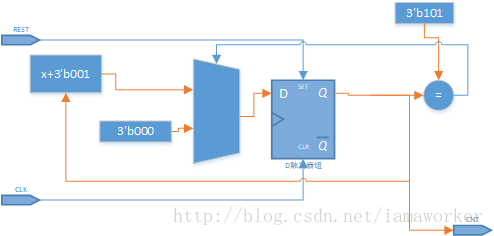

手绘版RTL图

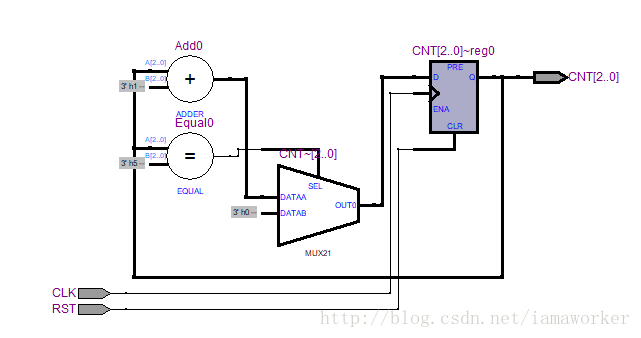

quartus自动生成的RTL图

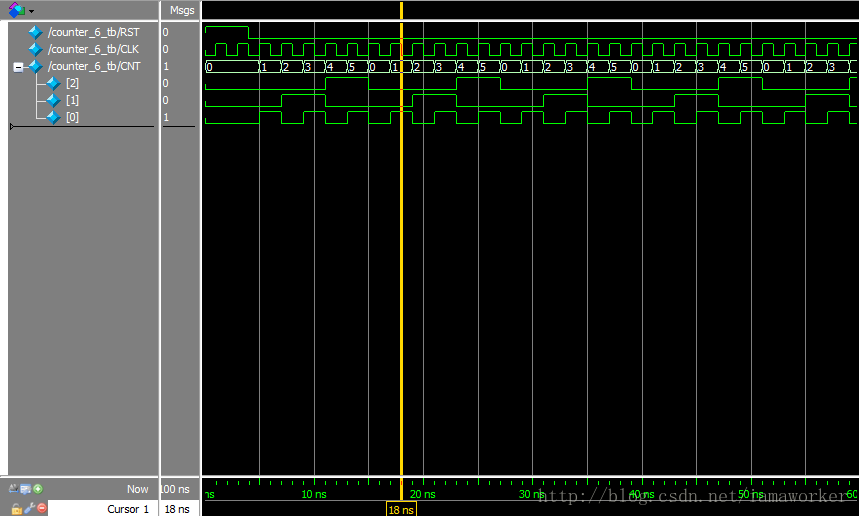

- modelsim仿真波形图

Markdown 是一种轻量级标记语言,它允许人们使用易读易写的纯文本格式编写文档,然后转换成格式丰富的HTML页面。 —— [ 维基百科 ]

代码

counter_6.v代码:

module counter_6(

input CLK,

input RST,

output reg [2:0] CNT

);

parameter MAX=3'b101;

always @(posedge RST,posedge CLK)

begin

if(RST)

begin

CNT<=3'b000;

end

else

begin

if(CNT==MAX)

begin

CNT<=3'b000;

end

else

begin

CNT<=CNT+3'b001;

end

end

end

endmodule

counter_6_tb.v代码:

module counter_6_tb();

reg RST;

reg CLK;

wire [2:0] CNT;

counter_6 counter(

.CLK(CLK),

.RST(RST),

.CNT(CNT));

initial

begin

CLK=1'b0;

RST=1'b1;

#4 RST=1'b0;

end

always #1 CLK<=~CLK;

endmodule

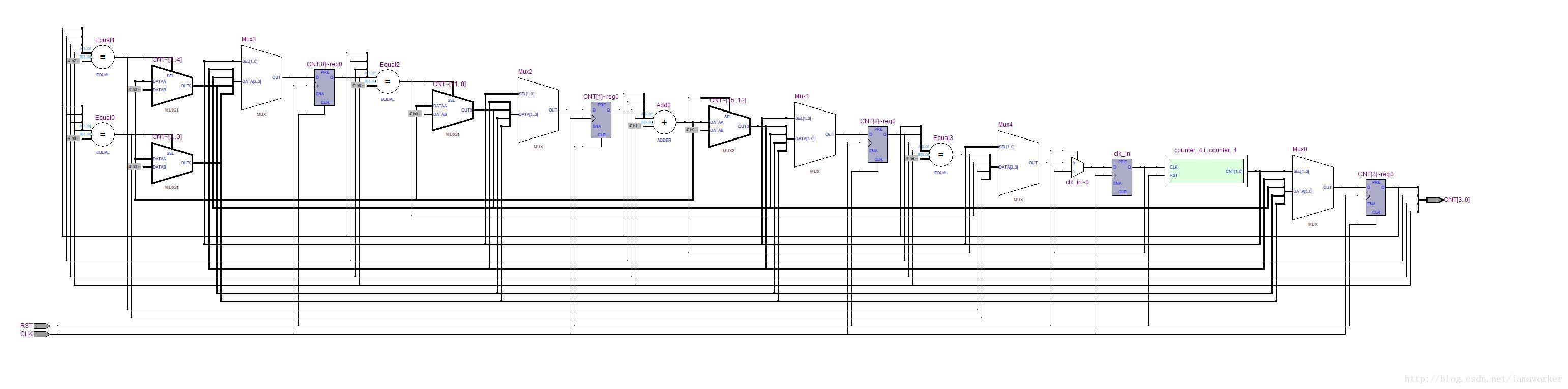

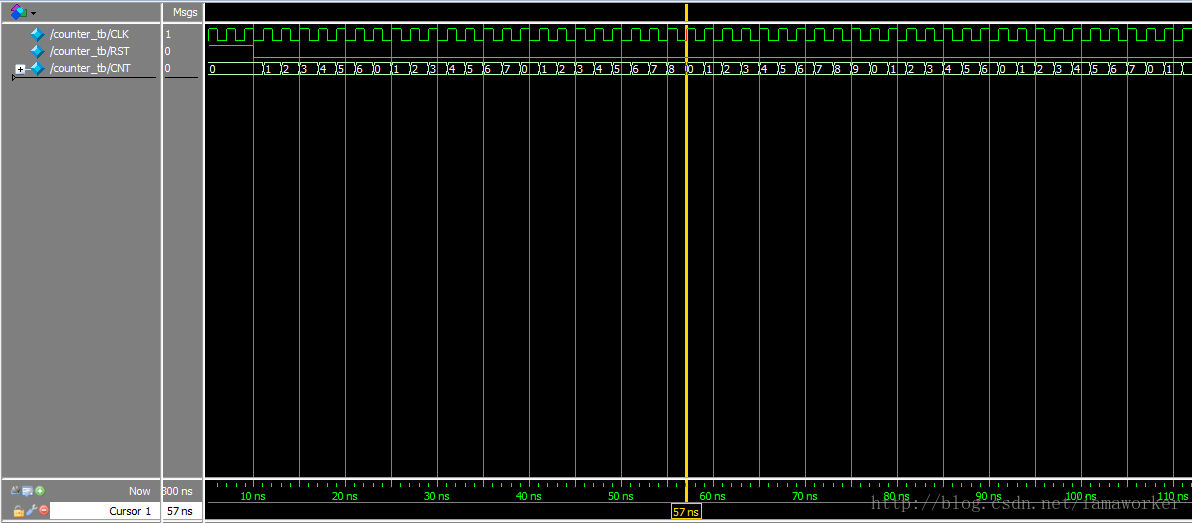

复杂计数器

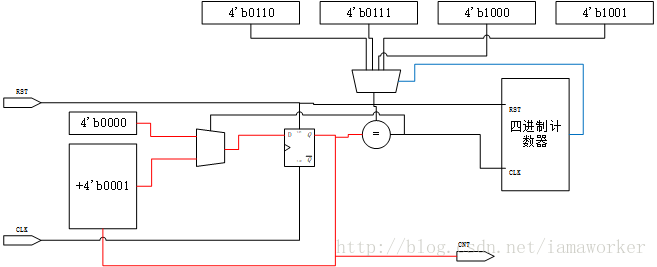

- 手绘版RTL图

- quartus自动生成的RTL图

- modelsim仿真波形图

counter_4.v代码:

input RST,

output reg [1:0] CNT);

parameter MAX=2'b11;

always @(posedge RST,posedge CLK)

begin

if(RST)

begin

CNT<=0;

end

else

begin

if(CNT==MAX)

begin

CNT<=0;

end

else

begin

CNT<=CNT+2'b01;

end

end

end

endmodule

counter.v代码:

input RST,

input CLK,

output reg [3:0] CNT);

parameter MAX_0=4'b0110;

parameter MAX_1=4'b0111;

parameter MAX_2=4'b1000;

parameter MAX_3=4'b1001;

reg clk_in;

wire [1:0] cnt_out;

counter_4 i_counter_4(

.RST(RST),

.CLK(clk_in),

.CNT(cnt_out));

initial

begin

clk_in<=0;

end

always @(posedge RST,posedge CLK)

begin

if(RST)

begin

CNT<=4'b0000;

end

else

begin

case(cnt_out)

2'b00:

begin

if(CNT==MAX_0)

begin

CNT<=4'b0000;

clk_in<=1;

end

else

begin

CNT<=CNT+1;

clk_in<=0;

end

end

2'b01:

begin

if(CNT==MAX_1)

begin

CNT<=4'b0000;

clk_in<=1;

end

else

begin

CNT<=CNT+1;

clk_in<=0;

end

end

2'b10:

begin

if(CNT==MAX_2)

begin

CNT<=4'b0000;

clk_in<=1;

end

else

begin

CNT<=CNT+1;

clk_in<=0;

end

end

2'b11:

begin

if(CNT==MAX_3)

begin

CNT<=4'b0000;

clk_in<=1;

end

else

begin

CNT<=CNT+1;

clk_in<=0;

end

end

endcase

end

end

endmodule

counter_tb.v代码:

reg CLK;

reg RST;

wire [3:0] CNT;

counter i_counter(

.CLK(CLK),

.RST(RST),

.CNT(CNT));

initial

begin

CLK<=0;

RST<=1;

#2 RST<=0;

end

always

begin

#1 CLK<=~CLK;

end

endmodule

3529

3529

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?