时钟控制逻辑

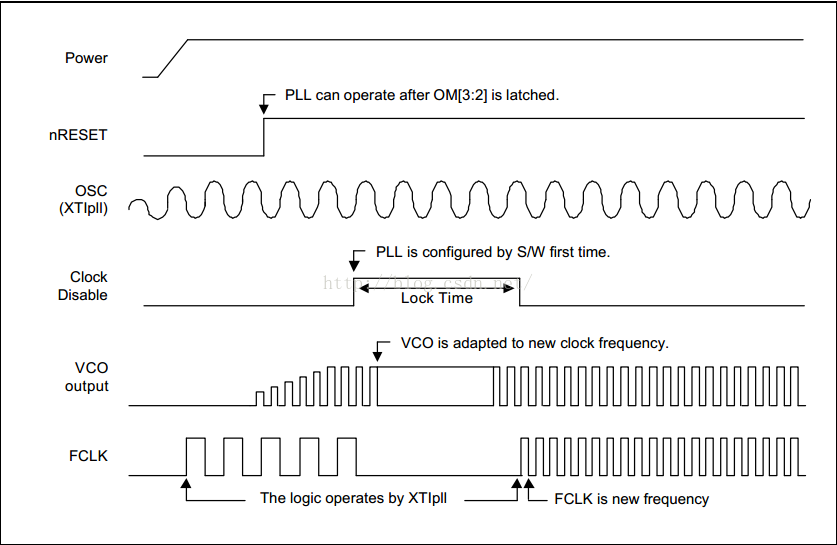

时钟控制逻辑决定时钟源是PLL还是外部时钟。当PLL配置为新的的频率值,时钟控制逻辑将禁止FCLK,直到经过PLL锁定时间后PLL输出稳定。时钟控制逻辑同样作用于上电复位和掉电恢复模式。

上点复位

晶振在几毫秒之内开始振荡,OSC时钟稳定之后,nRESET释放,PLL就根据默认配置运作。然而,PLL刚刚上电后并不稳定,所以在软件配置PLLCON之前,Fin直接用作FCLK(而非Mpll),即使在复位后用户不想更改PLLCON的默认值,用户也应通过软件写入相同的值。

当PLL配置为新的频率,它会从启锁定时序,产生新的频率,FCLK可在锁定时间后配置为PLL输出。

在正常模式下改变PLL设置

用户可以通过写PMS值来改变频率,PLL锁定时间也会自动插入。锁定期间,S3C2440A内部逻辑块没有时钟供应。

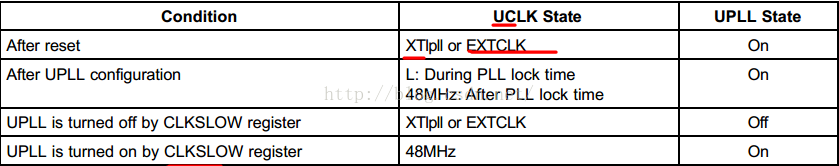

USB时钟控制,USB主控接口和USB器件接口需要48Mhz的时钟。在S3C2440A内,有专用的PLL为USB生成48Mhz时钟。只有配置UPLL之后,UCLK才会生成。

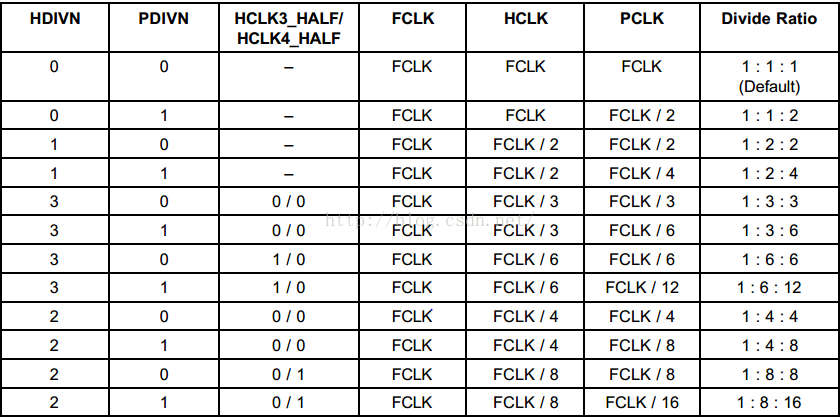

FCLK,HCLK和PCLK

FCLK被ARM920T使用;

HCLK被AHB总线使用,被ARM920T,内存控制器,中断控制器,LCD控制器,DMA和USB主控模块使用。

PCLK由APB总线使用,由外设诸如,WDT,IIS,I2C,PWM定时器,MMC接口,ADC,,GPIO,RTC和SPI使用。

S3C2440A支持在FCLK,HCLK和PCLK之间支持可选比率。这个比率由HDIVN 和CLKDIVN 的PDIVN 控制

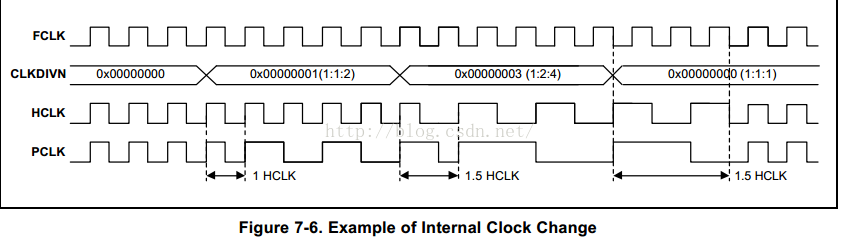

当设定了PMS的值,就需要设置CLKDIVN寄存器,CLKDIVN的值在锁定时间之后有效。这个值在复位和改变电源管理模式时仍然可用。

CLKDIVN寄存器的设置值在1.5个HCLK之后 也会有效。但是,只有将比率从默认的1:1:1变到其他的比率时才会出现1个HCLK使CLKDIVN寄存器值有效。

注意:

1、CLKDIVN的值需要谨慎设置,不要让FCLK和PCLK超过其限定值。

2、如果HDIVN不为0,CPU总线模式必须从快速模式改变为异步总线模式(S3C2440A不支持同步总线模式),所用的指令是:

mrc p15,0,r0,c1,c0,0

orr r0,r0,#R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

如果HDIVN不是0,CPU总线模式是快速模式,CPU将使用HCLK,这个特性可以用来使CPU的频率减半或者跟多,而不影响HCLK和PCLK.

3407

3407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?