转自:http://blog.csdn.net/k331922164/article/details/47623501

一、前言。

Signaltap是嵌入式逻辑分析仪,说到嵌入式,很容易让人想起ARM,其实Signaltap跟ARM没有半毛钱关系。这里的嵌入是嵌到FPGA的内部。

如果你用过Signaltap,就会发现,每次都要综合整个工程,再下载代码,然后才可以使用Signaltap,这说明了Signaltap是由一些逻辑电路组成,而不是仿真。

请不要把Signaltap和Modelsim混为一谈(如果是一样的话,就不用起两个名字了),就算两个软件的界面上的波形很像。

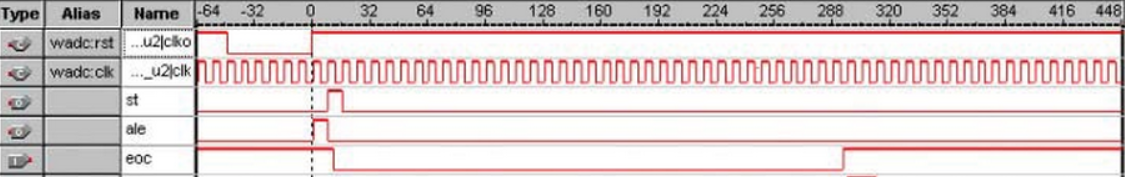

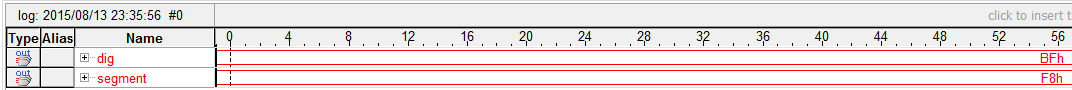

以下是Signaltap界面上的波形(代表实际的波形)。

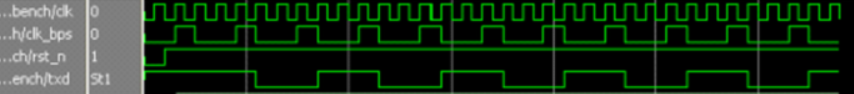

以下是Modelsim界面上的波形(代表仿真的波形)。

二、基本操作。

首先,要确保你的工程能成功综合,并且所消耗的资源不能为0。

然后在Quartus界面下,点开Tools菜单,打开SIgnaltap。

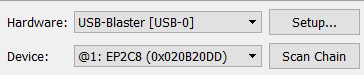

在SIgnaltap界面下,确保Jtag和FPGA开发板能用。

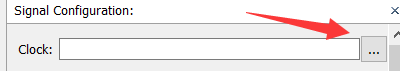

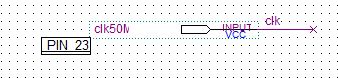

设置主时钟,点击红色箭头所指的地方。

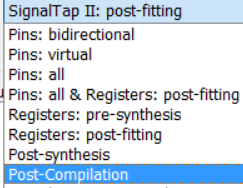

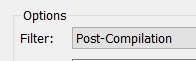

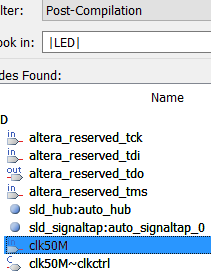

在Filter下,一般是选择Post-Compliation(综合后)。

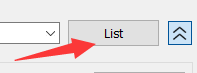

点击List,可以看到节点名。

可以看到由原理图或者HDL文件的节点名了,这里选择clk50M。

这个clk50M不是随便选的,是原理图上的全局时钟,这里用晶振的时钟做为Signaltap的采样时钟,你也可以选PLL倍频后的时钟,这都是看具体情况而定。

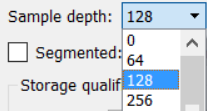

选择采样深度,也就是采多少个点,这也是看具体情况而定,深度越大,需要的资源越多,这里选择128。

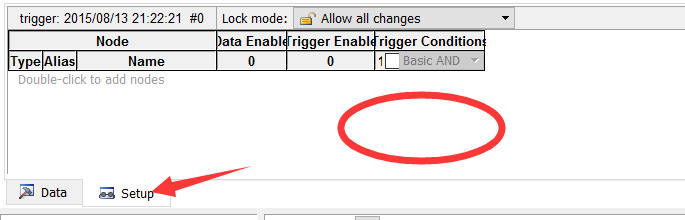

确保已选中Setup标签(红色箭头所指,选中为白色,未选中为灰色),然后双击红圈所示区域。

Filter同样选择综合后,同样点List列出所有节点。

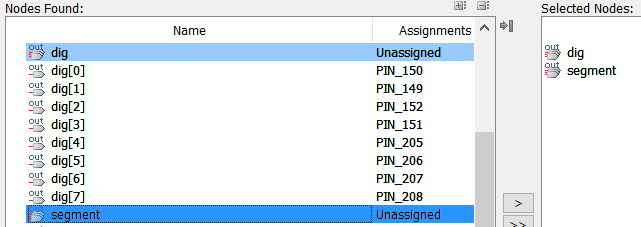

选择你想要观察的节点,这里选的是dig和segment。

dig和segment,同样在原理图(或者HDL文件)中有出现过的,是有效的节点名。

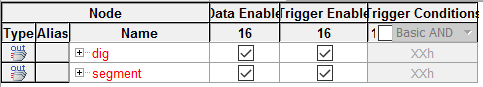

成功添加节点的话,会在Setup和Data标签下,出现下图所示。

好了,现在你可以在Quartus界面下,点Save all以保存所有文件,然后综合,再到Signaltap界面下,选择sof文件,下载(红色箭头所示的图标)。

成功下载sof的话,可以看到Ready to acquire。而Instance Manager右边有四个图标,分别代表单次运行,连续运行,停止和读数据。

点连续运行,就能看到Signaltap在采集数据了(数据在不断地跳,难以观察)。

如果你不停止掉Signaltap,是不能综合代码的。

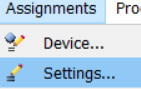

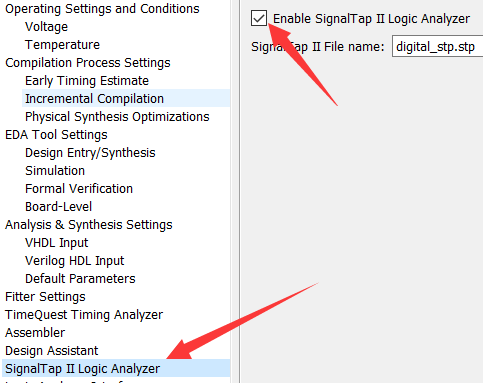

因为使用Signaltap,所以会额外消耗更多的资源,如果不想使用Signaltap的话,可以在Assignments->Settings设置一下,如下图所示。

只要去掉Enable SignalTap II Logic Analyzer前面的勾就可以了,这样,综合出来的电路就不带Signaltap了(资源会减少)。

三、高级操作。

1、条件触发。

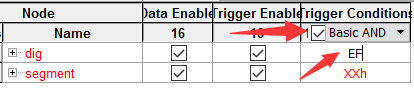

先停止Signaltap,然后在Setup标签下,勾选条件触发下面的Basic AND,然后在下面输入想要的触发条件,这里填的是EF,意思是当dig(8bit)为十六进制的EF时,就会触发Signaltap采样,而其它情况不触发。其中Basic AND是所有触发条件相与之后为真,就触发采样,当然也可以选择Basic OR(相或为真就触发采样)和Advanced。

如果不满足触发条件,Signaltap就一直显示Waiting for trigger。

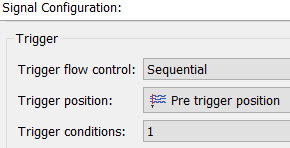

一般用上面的方法设置条件触发就够用了,如果有特殊要求,就用Signal Configuration下的条件触发,会有更强大的功能。

2、文件输出。

在File->Export,可以把Signaltap采样到的数据,保存为其它格式的文件,其中有csv,tbl,bmp,jpg,vcd,这五种格式可选。其中csv格式适合配合MATLAB使用。

3、数据格式。

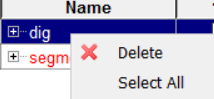

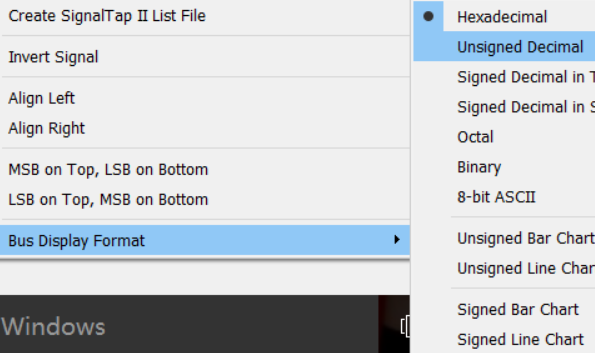

在需要观察的节点上,右击。

然后在Bus Display Format下,可以选择不同的数据格式,以方便观察。其中unsigned/signed line chart是用来观察连续信号的波形,如DDS下的sin/cos,或者是FSK,QAM等。

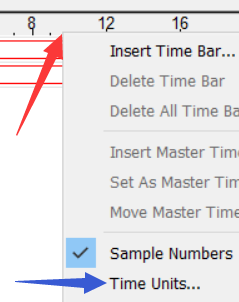

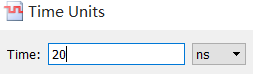

4、设置时间单位。

在红色箭头所指的地方,右击一下,选择Time Units,可以设置时间单位。

我这里的采样时钟是50M,所以,周期是20ns。

这样,Signaltap每采一个数据,所需要的周期就是20ns。为什么这个时间单位需要人手设定?就是因为Signaltap不带频率计的功能(下面在Signaltap内部原理有讲述)。

5、MATLAB与Signaltap联合使用。

首先,要把signaltap运行起来,采集到数据。

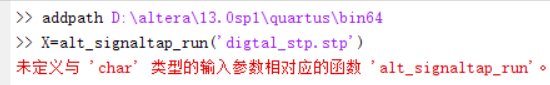

然后,在MATLAB下,添加quartus的bin文件的路径(32位的添加bin,64位的添加bin64),然后调用alt_signaltap_run函数就可以了,但是我这里却找不到该函数,实际是有这个dll的,路径也添加正确,该方法未果。

四、Signaltap内部原理。

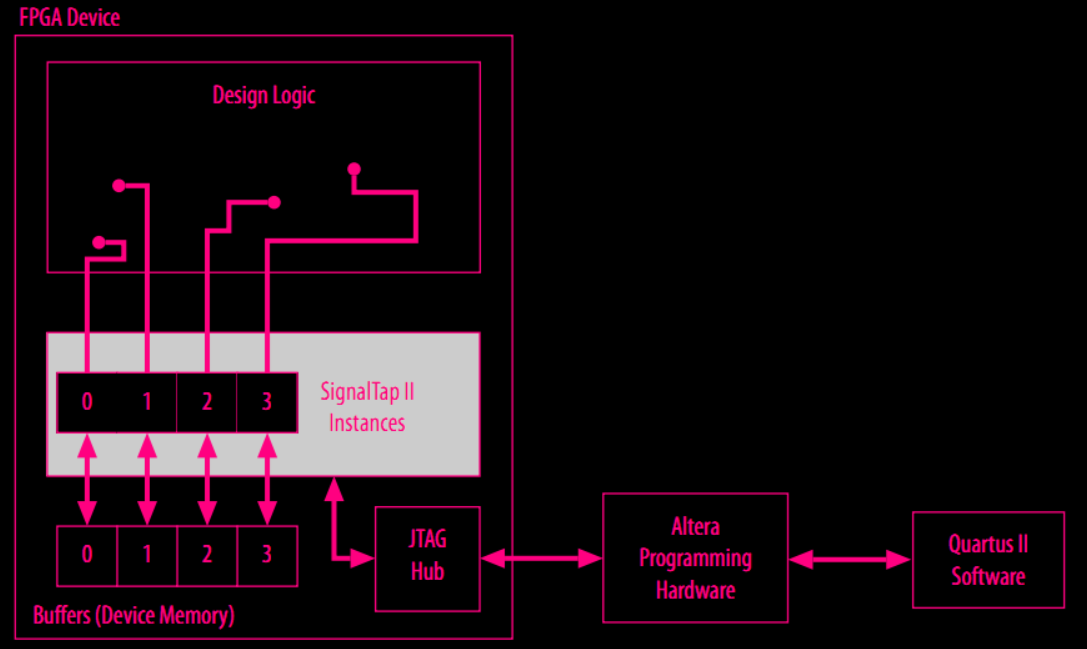

上图是signaltap的内部结构图,它是利用JTAG边界扫描的原理来读取FPGA内部节点的值,然后送到buffer(缓冲器),再由JTAG把数据送到quartus下的signaltap软件。

整个过程,都只有读取数据的作用,至于数据的频率(如DDS下的sin信号的频率)是无法直接知道的,只能让设计者自己计算得出。

五、其它问题。

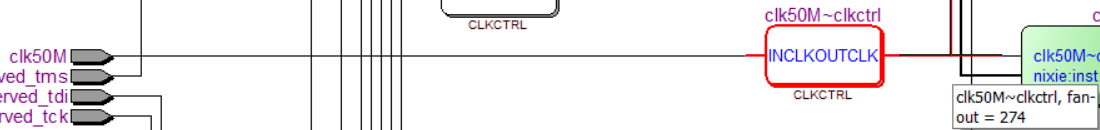

1、为什么在clk50M下面,会产生clk50M~clkctrl这个信号?

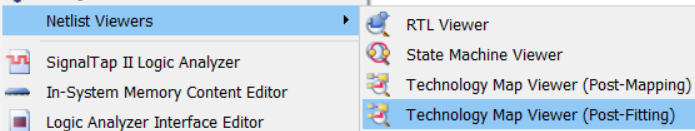

在工艺映射表(适配后),可以查看到这个信号。

其实clk50M~clkctrl就是clk50M的buffer而已,用于提高扇出系数,这里fan-out=274。

2、为什么加了Signaltap之后,原来能用的代码,变得不能用?

因为Signaltap本身需要占用一些逻辑资源,而这些逻辑资源影响了综合器的布局布线,所以有些时候加了Signaltap,时序反而乱了。不过,也有加了Signaltap时序变好的情况。

3、既然Signaltap采出来的信号是实际的波形,但是某些时候却跟实际的不相符?

就算是用Signaltap采出来的波形,也是需要遵循采样定理的,如果不满足采样定理,那么采出来的波形不能代表实际的波形。

而且Signaltap里面的触发器本身有滤波的作用,所以有些很小的毛刺,采不到,但是用示波器可以看出来。

945

945

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?