AXI是高级扩展接口,在AMBA3.0中提出,AMBA4.0将其修改升级为AXI4.0。AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

1.简介

1.1 关于AXI协议

AMBA AXI协议支持支持高性能、高频率系统设计。

- 适合高带宽低延时设计

- 无需复杂的桥就能实现高频操作

- 能满足大部分器件的接口要求

- 适合高初始延时的存储控制器

- 提供互联架构的灵活性与独立性

- 向下兼容已有的AHB和APB接口

关键特点:

- 分离的地址/控制、数据相位

- 使用字节线来支持非对齐的数据传输

- 使用基于burst的传输,只需传输首地址

- 分离的读、写数据通道,能提供低功耗DMA

- 支持多种寻址方式

- 支持乱序传输

- 允许容易的添加寄存器级来进行时序收敛

1.2 AXI架构

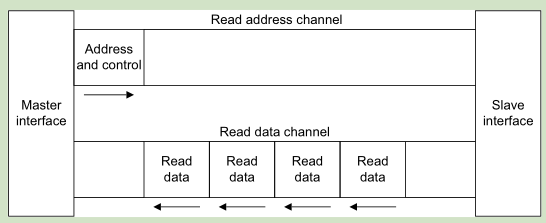

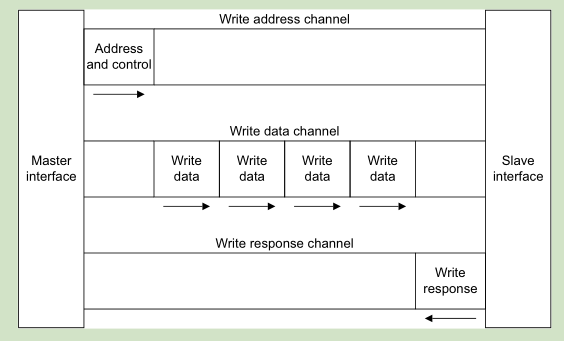

AXI协议是基于burst的传输,并且定义了以下5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

地址通道携带控制消息用于描述被传输的数据属性,数据传输使用写通道来实现“主”到“从”的传输,“从”使用写响应通道来完成一次写传输;读通道用来实现数据从“从”到“主”的传输。

图 1-1 读架构

图 1-2 写架构

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit)和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,“主”无需等待“从”对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16...1024bit)和字节线(用于指示8bit 数据信号的有效性)。

写响应通道:“从”使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

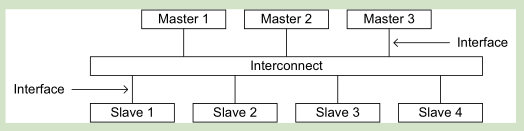

图 1-3 接口与互联

AXI协议提供单一的接口定义,能用在下述三种接口之间:master/interconnect、slave/interconnect、master/slave。

可以使用以下几种典型的系统拓扑架构:

- 共享地址与数据总线

- 共享地址总线,多数据总线

- multilayer多层,多地址总线,多数据总线

在大多数系统中,地址通道的带宽要求没有数据通道高,因此可以使用共享地址总线,多数据总线结构来对系统性能和互联复杂度进行平衡。

寄存器片(Register Slices):

每个AXI通道使用单一方向传输信息,并且各个通道直接没有任何固定关系。因此可以可以在任何通道任何点插入寄存器片,当然这会导致额外的周期延迟。

使用寄存器片可以实现周期延迟(cycles of latency)和最大操作频率的折中;使用寄存器片可以分割低速外设的长路径。

2.信号描述

表 2-1 全局信号

| 信号名 | 源 | 描述 |

| ACLK | 时钟源 | 全局时钟信号 |

| ARESETn | 复位源 | 全局复位信号,低有效 |

表 2-2 写地址通道信号

| 信号名 | 源 | 描述 |

| AWID |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1399

1399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?