这一周忙里偷闲,利用晚上的琐碎时间跑了一个录音芯片的后端PD流程,由于之前在课堂上学的数字EDA仅限于书本概念,一些概念的理解只是停留在表面,实践之后的确豁然开朗了很多,里面很多技术细节绝不是课堂上翻几页PPT可以草草概括的。有了这次体验,不论是自己即将升入研二做项目还是对之后的找工作也是大有裨益的,也绝对比以后靠面试前临时多看几本书,狂背一堆概念有用的多。多余的话就BB到这了,下面就和大家简单分享一下,大神们不喜勿碰。

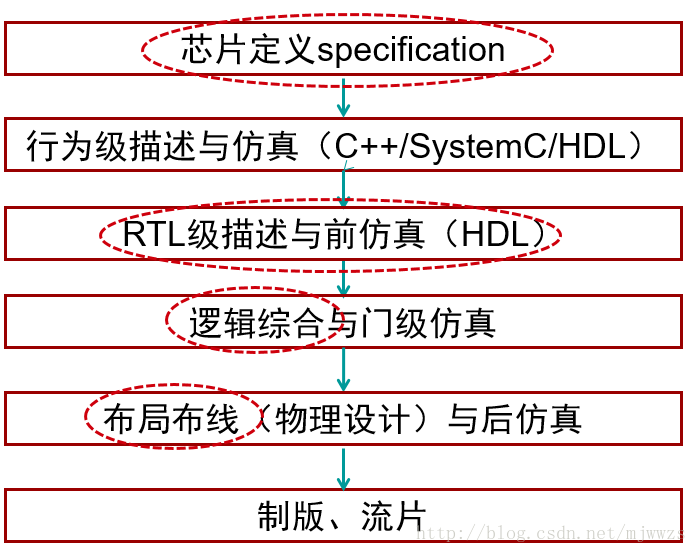

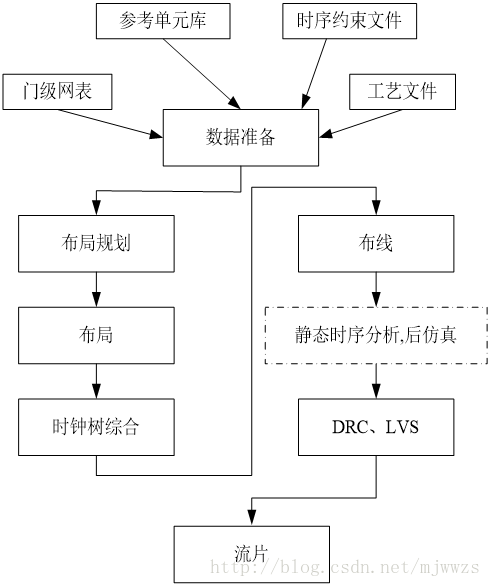

首先设计一个芯片,首先得知道相关的设计需求,也就是定义spec,随着数字IC的快速发展,大型IP的直接调用也节省了不少冗余重复的体力劳动,IP多种多样,也就自然而然有IP的选型,再加上工艺、封装的确定。这些都定下来后,我们就开始了我们的行为级描述与仿真,也就是前端工程师要开始码Verilog了,当然在设计大型的SOC或者涉及到复杂算法的通信芯片时,我们还要辅之以Matlab建模,一般用Simulink搭系统来验证集成的正确性或算法的有效性。用Verilog描述好电路系统时,接下来便要进入验证,验证的方法就多种多样了,像业界主流的用UVM方法学进行模块级验证,来确保整体的功能Coverage,这又要求验证工程师与设计工程师充分沟通,了解芯片的功能定义以及具备扎实的SV功底,Testbench包含尽可能多的情况。这些都完成之后,便可Code Freeze,接下来就交给后端工程师进行物理实现了。像现在的高校的话考虑到后端流程的复杂性以及在整个设计周期耗费的时间,都会选择用FPGA进行原型验证,这也就是我为什么写下本文的用意,希望和我一样都还在读书的学生能对后端设计有一个大概的了解,能够弥补这块高校和企业之间的断档,也能为以后迅速成为后端设计工程师提前打一些基础。整个IC Design Flow如下图所示:

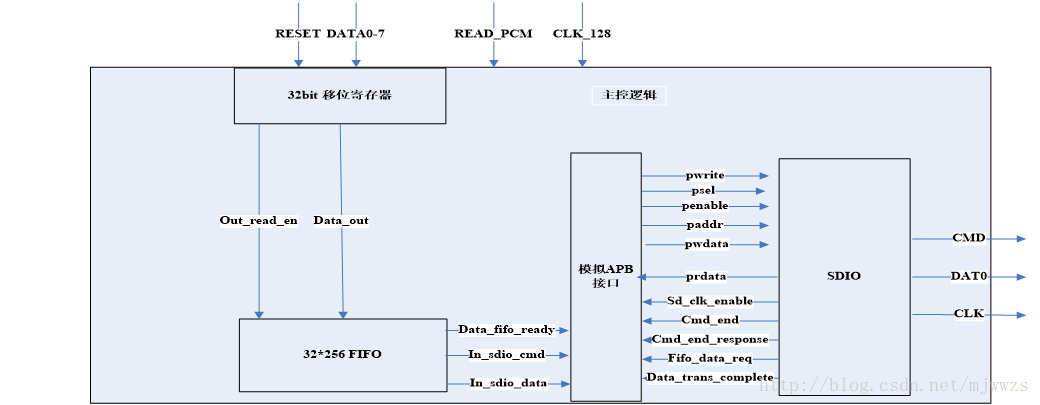

前端的设计和VCS仿真工作在这就不做阐述,不过为了方便大家对所要设计的芯片有个整体设计框架的了解,给出整体模块连接结构图如下:

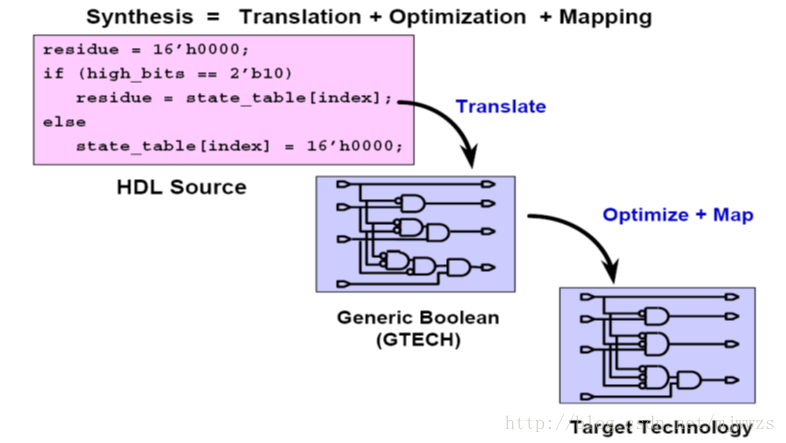

首先就要进入综合阶段,这部分最后要实现的就是把RTL源代码转换成门级网表,电路的逻辑综合过程一般由三个步骤组成,即:

综合=转化+优化+映射

常用的综合工具有Synopsys公司的Design Compiler 和Candance公司的Enconter RTL Compiler。

Design Compiler有两种界面供用户使用,一种是命令界面,一种是图形界面。在UNIX命令行下分别执行以下命令可以分别进入上述两种界面:

unix% dc_shell-t (命令界面)

unix% design_vision (图形界面)

Design Compiler支持TCL(Tool Command Language)语言,它是公开的业界标准界面语言。DC-Tcl在TCL的基础上扩展丰富了TCL,使用户可以更加灵活方便地运用TCL命令来对电路进行分析和优化。

DC中包含了多种工具,如DFT Compiler,Power Compiler,HDL Compiler,Library Compiler等,使得DC具有强大的功能,成为业界最流行的综合工具。综合考虑,我们此次也是选择的DC。

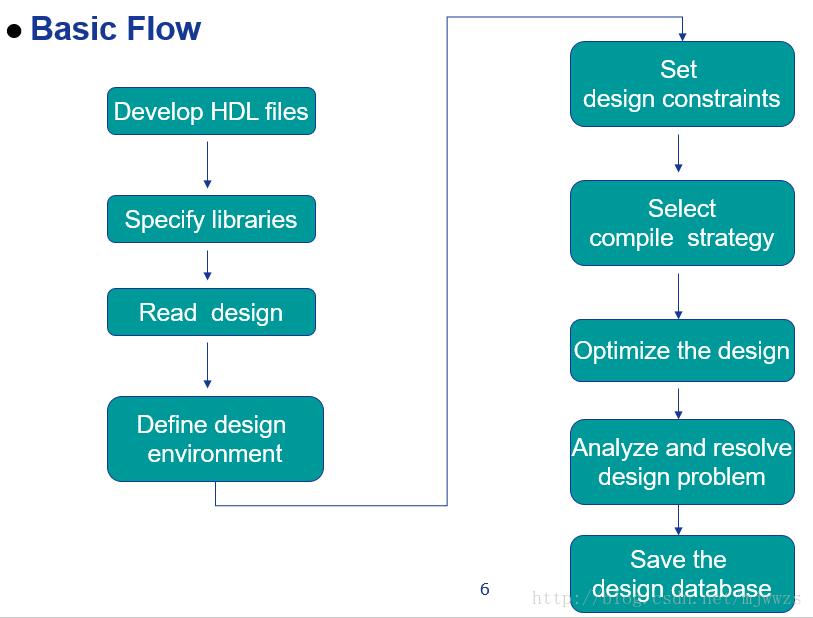

综合的基本流程包括:准备RTL代码->定义库->读入设计->定义设计环境->设置设计约束->设置综合策略->优化设计->分析和解决设计的问题->保存设计数据

接着就进入我们的综合实验部分,主要分以下几个步骤:

1.熟悉设计,获得设计目标和要求,如芯片的时钟频率,外部接口的时序要求等。

2.设置.synopsys_dc.setup文件

3.启动DC,读入RTL代码,并写出RTL级代码的ddc文件。

unix%dc_shell

dc_shell> source –echo –verbose read_file.tcl

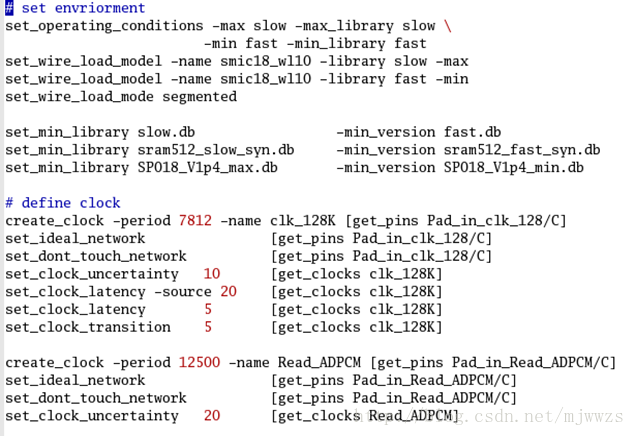

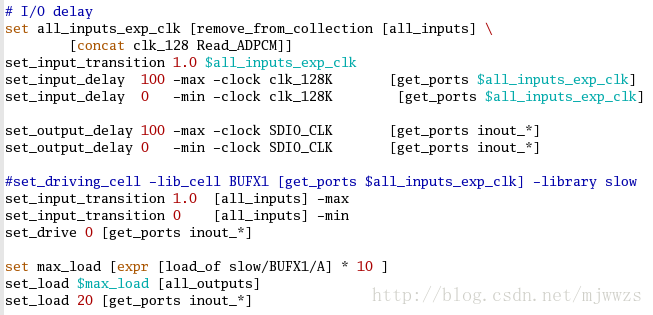

4.设置约束。

dc_shell> source –echo –verbose constraints.tcl

5.综合,优化

dc_shell> compile_ultra -no_autogroup

6.查看报告

dc_shell> report_constraint -all_violarors

7.保存文件

dc_shell> write –format ddc –hierarchy –output Recordchiptop.ddc

可以看到整个dc的流程都是run tcl脚本,一开始要对.synopsys_dc.setup文件进行设置,后续的tcl主要是对芯片内部时钟,I/O口,Environment以及DRC的一些约束,像跑完上面整个流程,report都通过的话,可以把所用的tcl按顺序整合成一个main_flow.tcl脚本,方便下次直接一次性完成综合。

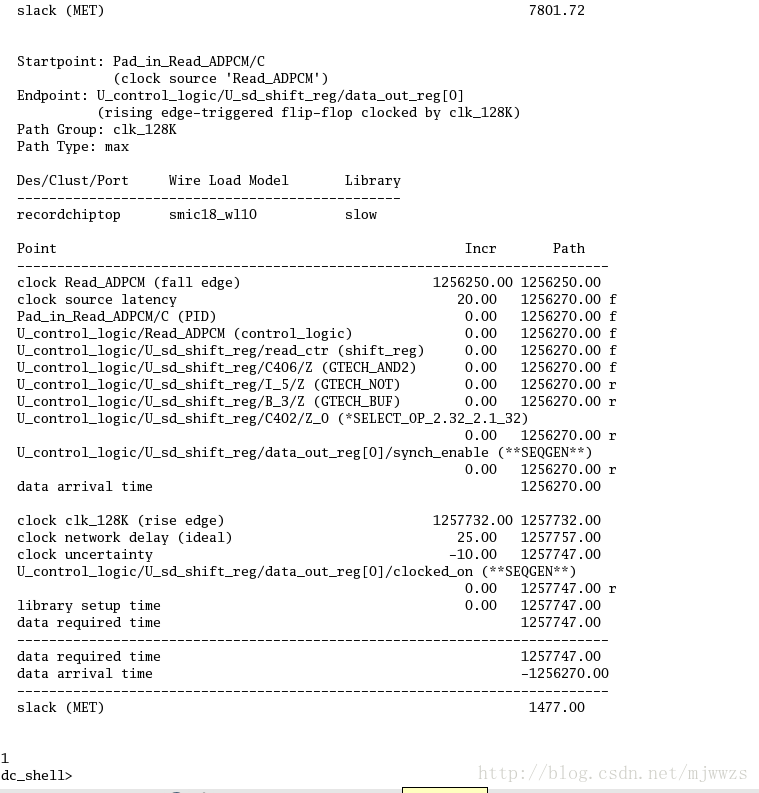

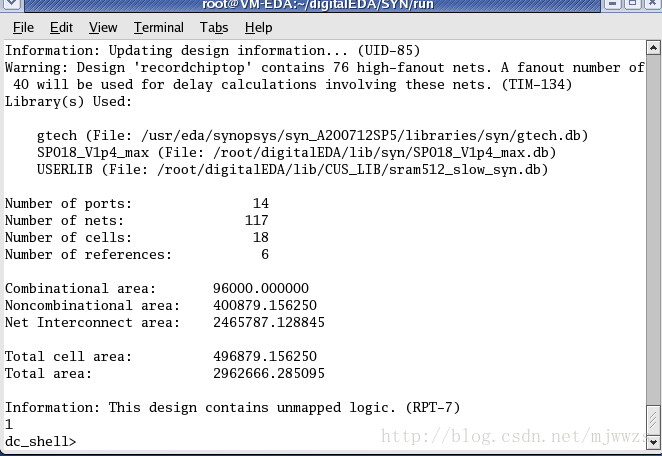

在dc_shell中键入report_area和report_timing便可查看电路的面积和时序报告,尤其是时序是否满足要求的建立/保持时间,看total slack是否大于0。一般在dc中只检查建立时间,因为它直接与clock相关,hold不予考虑,因为在后面P&R阶段,Hold的违规能通过插入Buffer解决。

经过反复的综合后,设计已达到要求。需输出相应的文件,如门级网表,sdc文件等,以便后续的时序分析和验证。通过静态时序分析和形式验证来验证综合的正确与否,其中静态时序分析可以更加准确地分析时序,从而检查综合的时序是否正确;而形式验证则用数学的方法验证综合出的电路与原电路的功能是否一致。在验证通过后才可以进行下一步的布局布线,否则还要重新综合。

接着就进入物理设计阶段,也就是把我们前面生成的门级网表转化成foundry可用于掩膜的版图信息。常用的布局布线工具有Synopsys公司的IC Compiler、 Astro和Candance公司的SOC-Enconter。IC Compiler是synopsys公司继Astro之后推出的另一款P&R工具(物理设计通常简称为布局布线,place and route),Astro常用于10nm工艺一下超深亚微米级的布局布线。

输入IC Compiler 的有:门级网表、库文件、时序约束。

输出IC Compiler 的是layout(常用格式是GDSII)。

整个流程中,除了floorplan阶段需要较多的手工活之外,placement、CTS、routing阶段可以说就是设计者通过修改脚本和约束,然后让工具自动完成工作。这也是IC Compiler工具强大之处。在这里,就要着重强调一个CTS的概念:

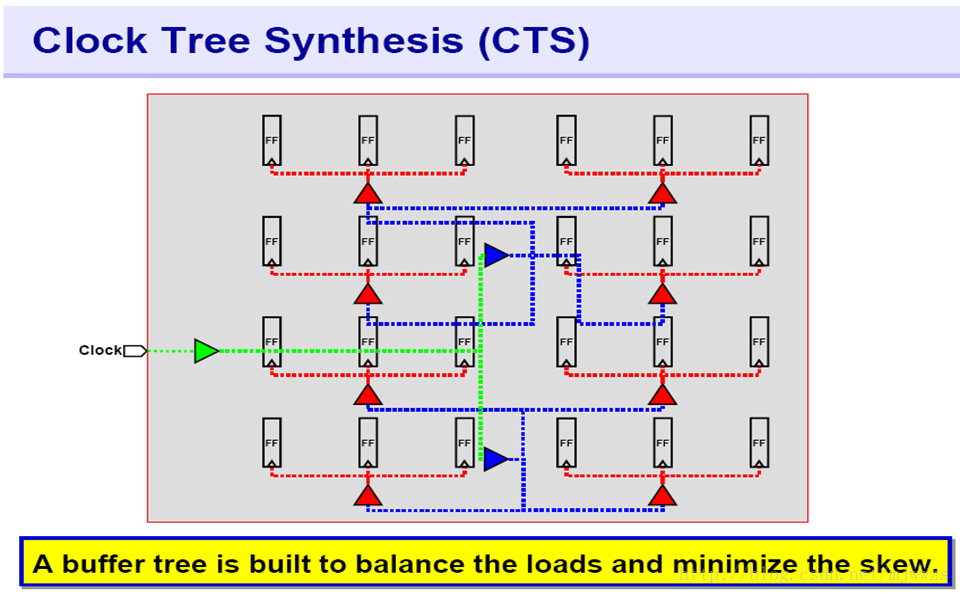

在大规模集成电路中,大部分时序元件的数据传输是由时钟同步控制的时钟频率决定了数据处理和传输的速度,时钟频率是电路性能的最主要的标志。在集成电路进入深亚微米阶段,决定时钟频率的主要因素有两个,一是组合逻辑部分的最长电路延时,二是同步元件内的时钟偏斜(clock skew),随着晶体管尺寸的减小,组合逻辑电路的开关速度不断提高,时钟偏斜成为影响电路性能的制约因素。时钟树综合的主要目的是减小时钟偏斜。

以一个时钟域为例,一个时钟源点(source )最终要扇出到很多寄存器的时钟端(sink),从时钟源扇出很大,负载很大,时钟源是无法驱动后面如此之多的负载的。这样就需要一个时钟树结构,通过一级一级的buffer去驱动最终的叶子结点(寄存器)。

Clock_opt 完成之后,一般都应该使用一个命令psynopt去做一次增量优化,psynopt这个命令的作用就是在原有基础上做增量优化。在placement阶段,place_opt之后,也需要用psynopt做一次增量优化,可以参考看run_icc_record.tcl脚本。在做完CTS之后,即run_icc_record.tcl里面CTS部分,可以报出时序信息,通过以下命令报时序信息:

report_constraint –all 报出所有时序违规(violations),正如前文中提到的,我们暂且只关注setup违规,setup违规直接制约频率能跑多高,对于hold的违规只需要通过插buffer增加延时就可以解决。

report_clocks 报出时钟的信息

report_timing –from -to 报出具体路径的时序信息

以上命令都可以加-help选项查看帮助信息,如report_timing –help,想查看一个命令的详细用法,可以man 命令,如man report_timing。

P&R完成后,就进入后仿阶段,为什么要后仿,后仿的目的在于消除或减小理论结果与实际结果之间的差异 ,版图生成以后,版图中的连线及连线间的寄生电阻,寄生电容,甚至寄生电感(现阶段一般后仿不包括电感)都是前仿中没有添加的,亦即,前仿的网表中认为各根连线的电阻电容均为零。事实并非如此,如果这些寄生电阻电容效应足够大,那么实际做出的电路就和前仿差别较大。后仿需要考虑版图中实际连线的RC延时。ICC生成版图之后,ICC会写出一个电路网表,star_rc_xt 抽取版图寄生参数,PT获得寄生参数信息后写出sdf(standard delay format)文件,用于反标入电路网表。后仿真的对象是由ICC生成的电路网表,后仿真是电路级的仿真,仿真反标入了由PT产生的sdf文件 。

Sign-off阶段就是进行DRC和LVS物理验证。

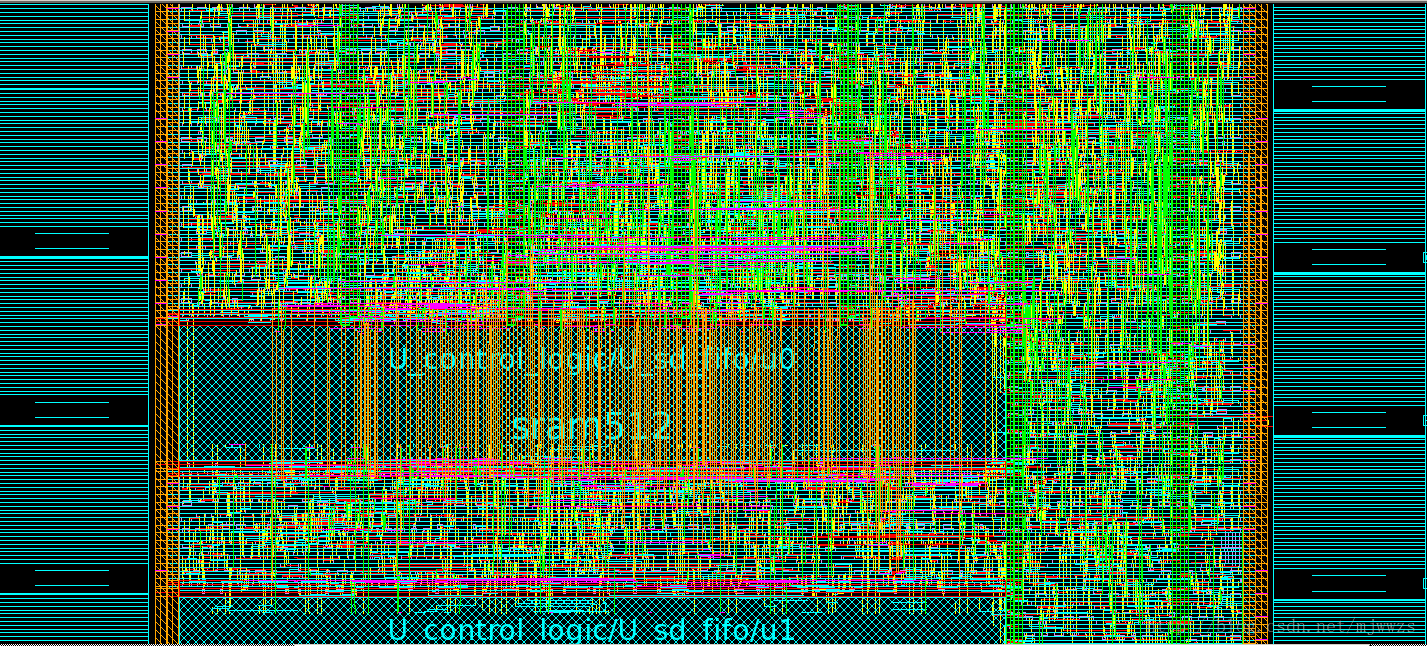

这里本人也是用的icc_shell的图形交互界面来完成物理设计,也是写tcl,跑脚本让工具完成相关工作。最后完成的总版图如下:

1293

1293

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?