Tiny210 U-BOOT(六)----DDR内存配置

1.S5PV210内存芯片简介

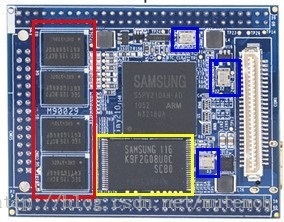

最左边的四片就是内存芯片,是DDR2-800,这表示数据传输频率为800MHz,外部时钟频率200MHz,内部时钟频率为100MHz;因为内部一次传输的数据就可供外部接口传输4次,虽然以DDR方式传输,但数据传输频率的基准——外部时钟频率仍要是内部时钟的两倍才行。

我的板子上显示芯片型号为K4T1G084QF,打开三星的DDR2芯片命名规则文档(这个文档上网去搜索):

1~3. 比较简单,表示是DDR2内存;

4~5. Density,表示容量为1Gbit = 1Gbit/8 = 128MByte

6~7. Bit Organization,表示数据有多少bit,这里是08,则表示数据为8bit,四片拼起来,数据线就是32位。

8. # of Internal Banks,表示多少Bank,这里是4,表示为8个Banks

9. Interface, VDD, VDDQ,这里解释一下这两个电压的意思

VDD:北桥芯片供电电压或者存储芯片的输入缓冲和核心逻辑的供电电压。

VDDQ:存储芯片的输出缓冲供电电压。

Q : SSTL_18, 1.8V, 1.8V,根据芯片手册得出这两个电压为1.8V

10. Generation

F : F-die,这是什么意思???

芯片上型号K4T1G084QF,再往上看,会看到有四个BCF7的字母,接着看代表什么意思

12. Package

B : FBGA (Lead-Free & Halogen-Free, Flip Chip),表示这FBGA封装,FBGA是Fine-Pitch Ball Grid Array(意译为“细间距球栅阵列”)的缩写

13. Temp, Power

C : Commercial Temp.(0°C ~ 85°C), Normal Power,表示工作的温度范围和供电

14~15. Speed (Wafer/Chip Biz/BGD: 00)

F7 : DDR2-800 (400MHz@CL=6, tRCD=6, tRP=6),表示为DDR2-800的内存

分析完成,开发板上共有4片这样的内存芯片,总容量就是128M*4=512M

2.分析硬件原理图

2.1 从芯片角度

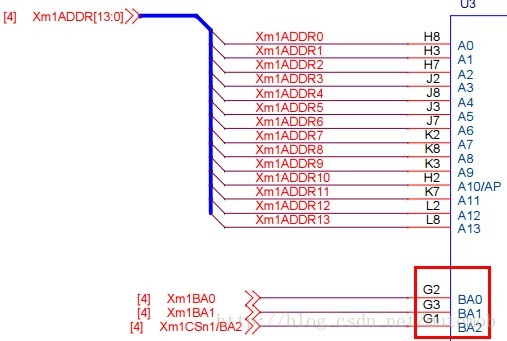

地址线:

A0-A13 14根

BA0,BA1,BA2

3根BA线表示这个芯片被分成了2^3=8个Bank,每个Bank则为128M/8=16M

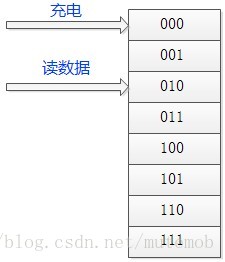

这里出现一个问题,为什么128M里面还要划分出8个Bank?

前面在Nand Flash的时候,我曾经分析过,由于DDR是不自备充电电路的,所以,每隔一段时间,内存控制器就会刷新一次电路,也就是要充一次电,如果只有一个Bank,那么结果就是在某一时刻,要么都充电,要么都不充电。

像上面这样分成了8个Bank,当我对000充电的时候,我还可以在010或是剩下的别的Bank中读取数据,这样就减小了等待的时间,不用说当电路刷新时,不能读取数据了。

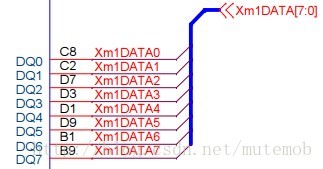

数据线:DQ0-DQ7*4 = 8bit * 4chips = 32bit

控制线:nCS,nRAS,nCAS

nCS:片选信号,当这个芯片被片选后,这个芯片就使能了,如果这芯片地址线上有地址,那么基本上数据线上就要出数据了。

地址线是A0-A13,是14根线,2^14=16K (128M = 2^27),所以地址线上地址要发两次,一次发行地址,一次发列地址,这就是行列地址复用--nRAS,nCAS这两根线的作用。

14 + 14 = 28根 + BA0/BA1/BA2 = 2^31=2G,最大支持2G的内存

128M = 2^27,27 - 3 = 24,行地址14根,所以,发过来的列地址是24-14=10

所以说,这个操作顺序是,先片选,CS拉低,然后,当RAS拉低时,表示传过的是行地址,是A0-A13,14位;当CAS拉低时,表示传过来的是列地址,是A0-A9,那列地址多的几位怎么办呢?很简单,用来扩展内存,谁说一片内存芯片就只能128M了?

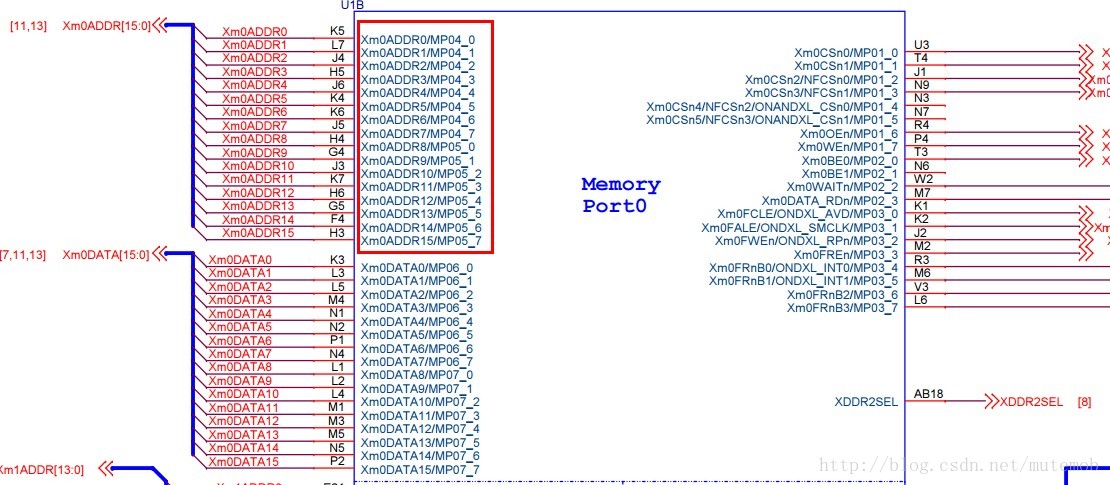

2.2 从处理器角度

地址线 Xm1ADDR0-Xm1ADDR13

Xm1BA0, Xm1BA1, Xm1CSn1/BA2

数据线 Xm1DATA0-Xm1DATA31

控制线 Xm1CSn0, Xm1RASn, Xm1CASn

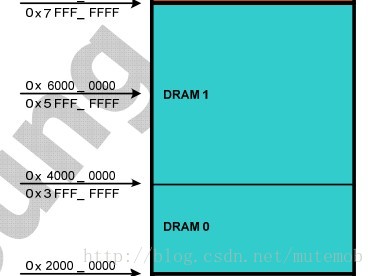

对于地址线前面的Xm1,可以参看核心板的原理图中内存的总图,整个内存分为三块,Memory Port0/Memory Port1/Memory Port2,Memory Port1/Memory Port2分别对应于芯片手册P29页中Memory Map中的DRAM0/DRAM1,可以分别接两组不同的DDR内存

而Memory Port0接的是SRAM,他的地址线是0~15,没有行地址,列地址,没有复用,所以他的容量就是2^16=64K

2.3DDR芯片手册

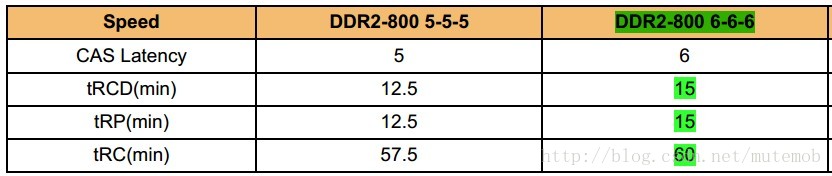

前面在查看芯片的型号命名规则时最后两位,我们的板子上是F7

14~15.

Speed (Wafer/Chip Biz/BGD: 00)

F7 : DDR2-800 (400MHz@CL=6,

tRCD=6, tRP=6),表示为DDR2-800的内存

打开K4T1G084QF.pdf的DDR芯片手册,P4的Key

Features,由此我们得知,我们要看的是DDR2-800 6-6-6

这里又多出和几个我们不认识的东西----CL,tRCD,tRP,看字面意思,大概来猜应该是一些时间,从芯片手册的命名规则上特意用一个字母代号来标识这三个东西,这肯定是非常重要的影响内存性能的某些时间参数。这里,有必要把DDR的工作原理重新梳理一下,这样,才能理解这些参数的意义。

本文详细解析了DDR2-800内存芯片的特性,包括其容量、速度和封装信息,并从硬件原理图的角度阐述了地址线、数据线和控制线的功能。同时,从处理器角度解释了内存总图中不同内存模块的连接方式,以及如何通过行地址和列地址复用实现高效数据传输。最后,结合DDR芯片手册,深入剖析了关键参数CL、tRCD和tRP的含义及其对内存性能的影响。

本文详细解析了DDR2-800内存芯片的特性,包括其容量、速度和封装信息,并从硬件原理图的角度阐述了地址线、数据线和控制线的功能。同时,从处理器角度解释了内存总图中不同内存模块的连接方式,以及如何通过行地址和列地址复用实现高效数据传输。最后,结合DDR芯片手册,深入剖析了关键参数CL、tRCD和tRP的含义及其对内存性能的影响。

7072

7072

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?