RAL model 就是RALF 规定的最高的hierarchy, 一般为sys 或者block。RAL model中定义了field的backdoor和frontdoor操作:peek, poke, read, write.

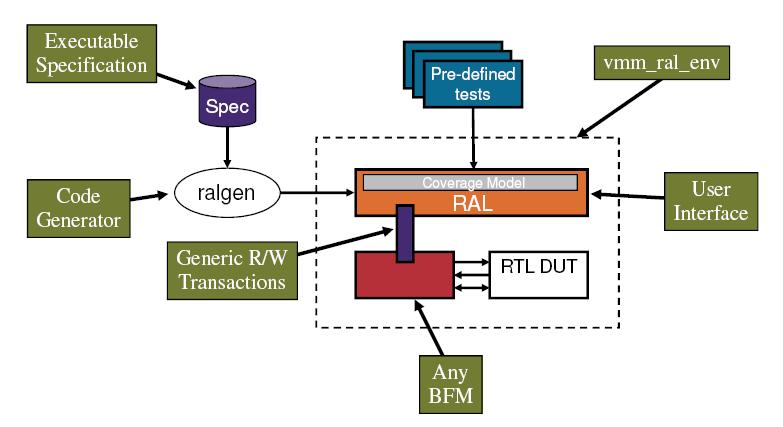

下图展示了RAL的env

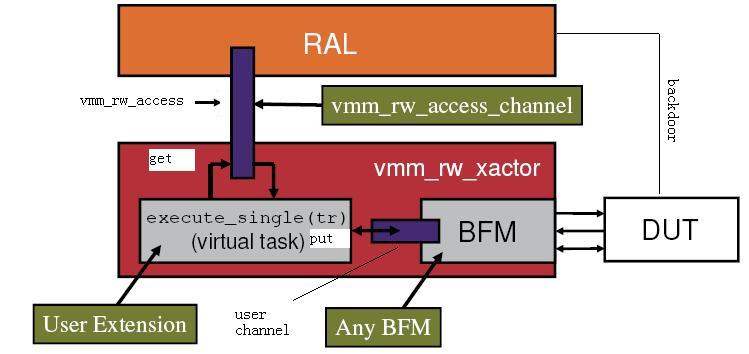

synopsys AE recommand that in vmm_rw_xactor, we use an output channel instead of BFM handler, 这样使得层次更清晰。由此会出现多个channel (RAL channel, generator channel)输入到BFM中,我们可以使用vmm_scheduler加以灵活的实现。

但是个人觉得使用BFM 的handler可以直接对BFM的channel进行操作,有效地插入transaction。

vmm_rw_access 由vmm_data扩展而来,定义了一些读写操作必须的成员,如kind, addr, data。 RAL的RWXactor,由vmm_rw_xactor扩展而来。它接受RAL过来的vmm_rw_access数据包,在execute_single函数中把这个数据包变成BFM channel能够传递的格式。至于RAL的环境说明如下:vmm_ral_env类从vmm_env派生出来。我们只需要用在原来环境的基础上,用vmm_ral_env 替代 vmm_env. 在vmm_ral_env里面做一些额外的工作,

1) 例化ral_model 并在构造函数里面直接注册 ( ral.set_model)

2) 例化RAL RWXactor, 并注册在build的时侯注册(ral.add_xactor), 注意add_xactor函数在add vmm_rw_xactor 后自动start这个xactor,所以我们在env中看不到启动RAL RWXactor。

3) 用定义hw_reset取代reset_dut达到RAL能反复reset dut。

如何使用预定义的testcase?

1) `define RAL_TB_ENV tb_env

2) vcs ..... $VCS_HOME/etc/vmm/sv/RAL/tests/hw_reset.sv

Backdoor Access

peek/poke : backdoor直接零时间访问,不影响register semantics,

backdoor read/write 直接零时间访问,但会象front-door一样影响register semantics

Access Path

vmm_ral::BFM, vmm_ral::BACKDOOR, vmm_ral::DEFAULT.

可以设定default access path是哪一种 env.ral_model.default_access=vmm_ral::BACKDOOR

HDL path

提一点, register MODER[3] ( ethreg%d.MODER_0.DataOut ); //这里 %d将被array index 代替。

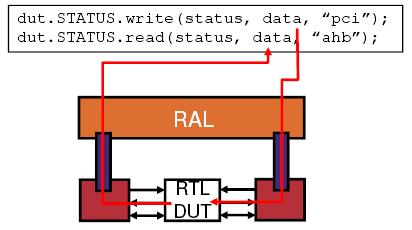

multi-physical interface 譬如DUT同时拥有AHB和PCI接口,各个接口有自己的memory映射,那么我们需要引入domain的概念,RALF如下:

access 这些register的时候要指明domain, 如下

由上可以看出每个domain拥有自己的vmm_rw_access_channel. 同样add_xactor(vmm_rw_xactor, domain)时也要指明domain.

multi-protocol with same interface,定义多个domain, 每个domain 拥有自己的transactor,但是BFM的handler指向同一个。如下:

register remap。这时候还是给每套register mapping 定义一个domain。

如果design中的register分散在各个零碎的module中,那么可以考虑在给register写hdl_path时全部带上各个module的instance。 如果两个rail,就机械的写出两个block。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?