十七、线程

线程的量级比进程小,其代码和存储区可共享,而且所消耗的资源比典型的进程小的多。

1、 线程的使用

1) begin ••••end顺序执行、fork•••join并行执行

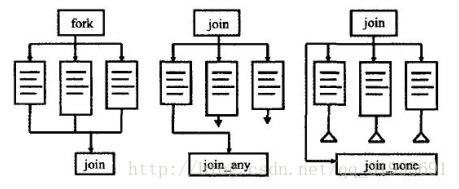

2) fork•••join、fork•••join_none、fork••••join_any的区别

注意:1)fork•••join_none块后的那个语句执行早于fork_none内的任何语句。

3) fork•••join_any块对块内语句进行调度,当完成第一个语句后,父线程才继续执行,其他停顿线程也得继续执行。

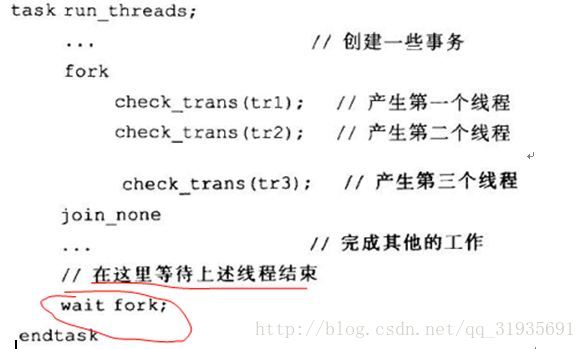

2、 等待所有的衍生线程

可以通过wait fork语句来等待所有子线程结束

例:

3、 在线程间共享变量

避免使用全局变量,这样容易导致漏洞。

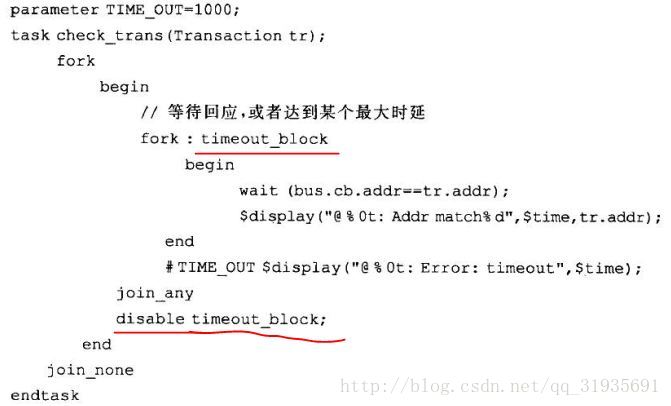

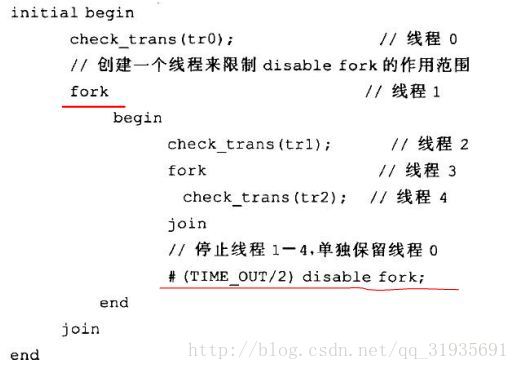

4、 停止线程的方法

使用disable语句可以用于停止systemverilog中的线程

停止单个线程:例

停止多个线程,例:

十八、线程间的通信

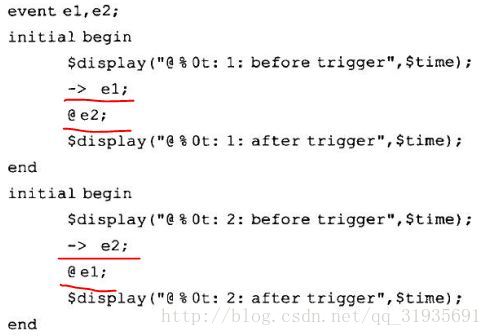

1、 事件

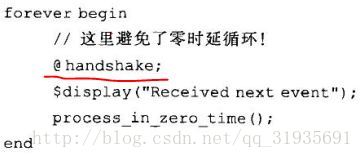

1)在事件边沿阻塞:例

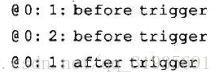

其输出结果如下:

2)等待事件的边缘触发方法

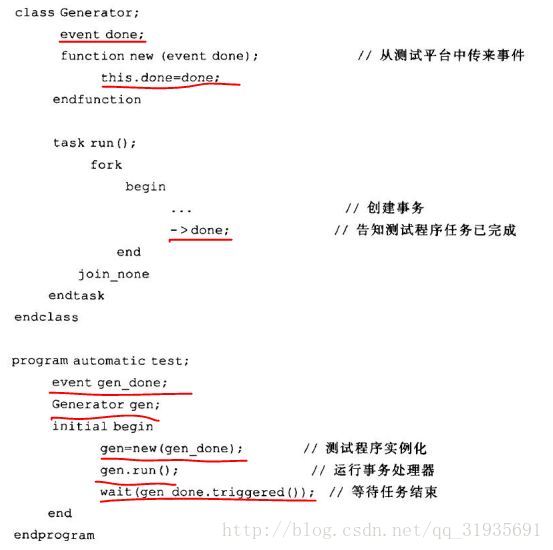

4) 传递事件

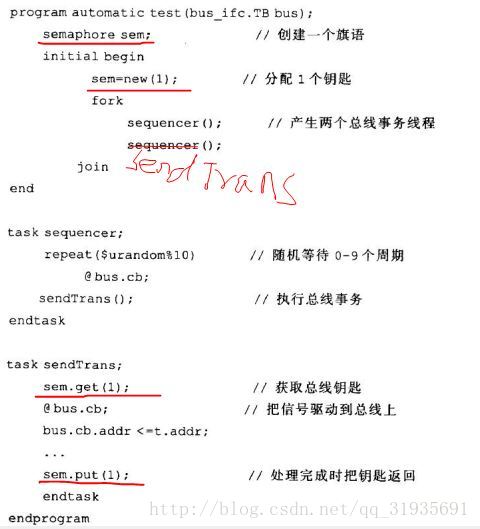

2、 旗语的使用方法

New方法可以创建一个带当个或多个钥匙的旗语,使用get可以获取一个或多个钥匙,而put则可以返回一个或多个钥匙,如果试图获取一个旗语而不希望被阻塞,可以使用try_get()函数

例:

如果需要使用带多个钥匙的旗语,需要注意:1)你返回的钥匙可以比你取出来的多。2)当你的测试程序需要获取和返回多个钥匙时,务必谨慎。

3、 信箱的使用方法

两个线程之间传递信息可以通过信箱。信箱可以简单的理解为一个具有源端和收端的fifo。

信箱是一种对象,必须调用new函数来进行实例化

使用put任务可以把数据放入信箱里,而使用get任务则可以移除数据。如果信箱为满,则put会阻塞;如果为空,则get会阻塞。Peek任务可以获取对信箱里数据的拷贝而不移除它。

注意:可以在信箱中放入句柄,但不能是对象。务必在一个信箱里只放入一种类型的数据。

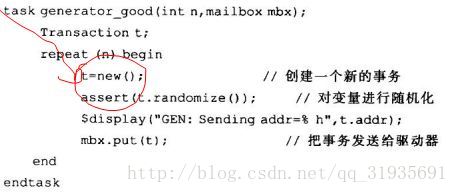

创建多个对象的发生器的正确方法:例

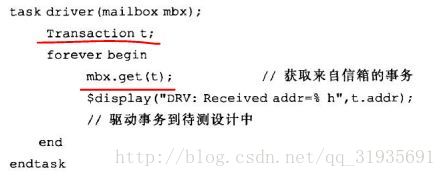

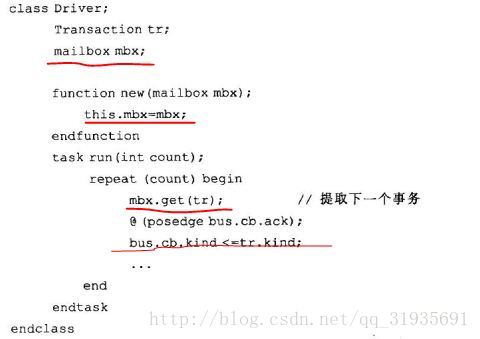

接收信箱的事务驱动器:例

使用信箱实现对象的交换,例:

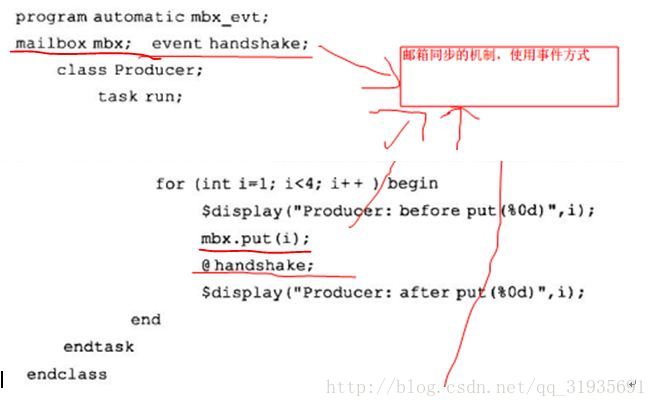

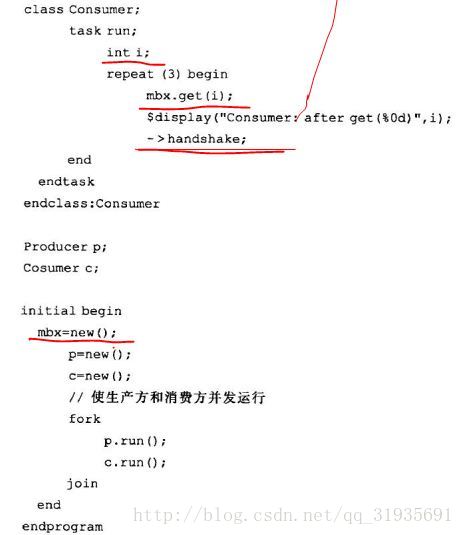

使用信箱和事件来实现线程同步的方法:

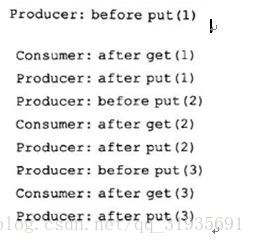

输出结果为:

549

549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?