说S5PV210的体系结构实际上是ARMv7架构下的Cortex-A8的体系结构。

1 ARM的编程模式

大部分ARM提供三种指令集: ARM指令集(32bit)、Thumb指令集(16bit)、Thumb2指令集(16&32bit)

- Thumb指令集是对ARM指令集的一个子集重新编码得到的,指令长度为16位。

- 通常在处理器执行ARM程式时,称处理器处于ARM状态;当处理器执行Thumb程式时,称处理器处于Thumb状态。

- Thumb指令集中的数据处理指令的操作数仍然为32位,指令寻址地址也是32位的。

- Thumb2指令集是Thumb指令集的一个扩充,既包含了16位也包含了32位,几乎可以提供与ARM相同的功能,但是指令密度(单位内存所存放的指令数)与Thumb指令集相似。有了Thumb2指令集就不再需要在ARM与Thumb两者之间切换了,因为用Thumb2就够了!

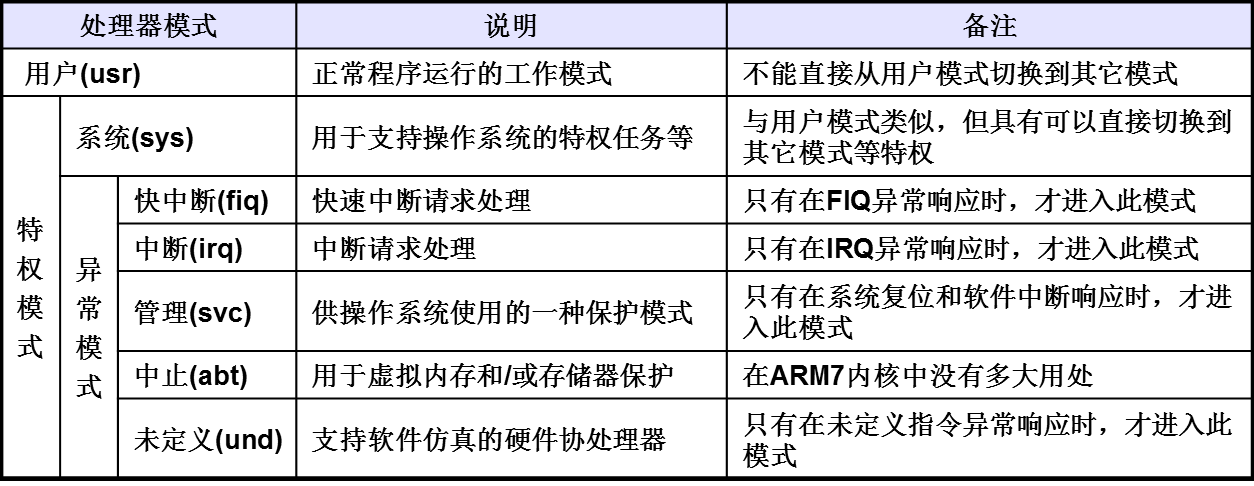

2 ARM的七种工作模式

S5PV210共有以下七种工作模式:

从图中可以注意到,用户模式是唯一的非特权模式。而在特权(privilege)模式中,只有系统模式是非异常模式。

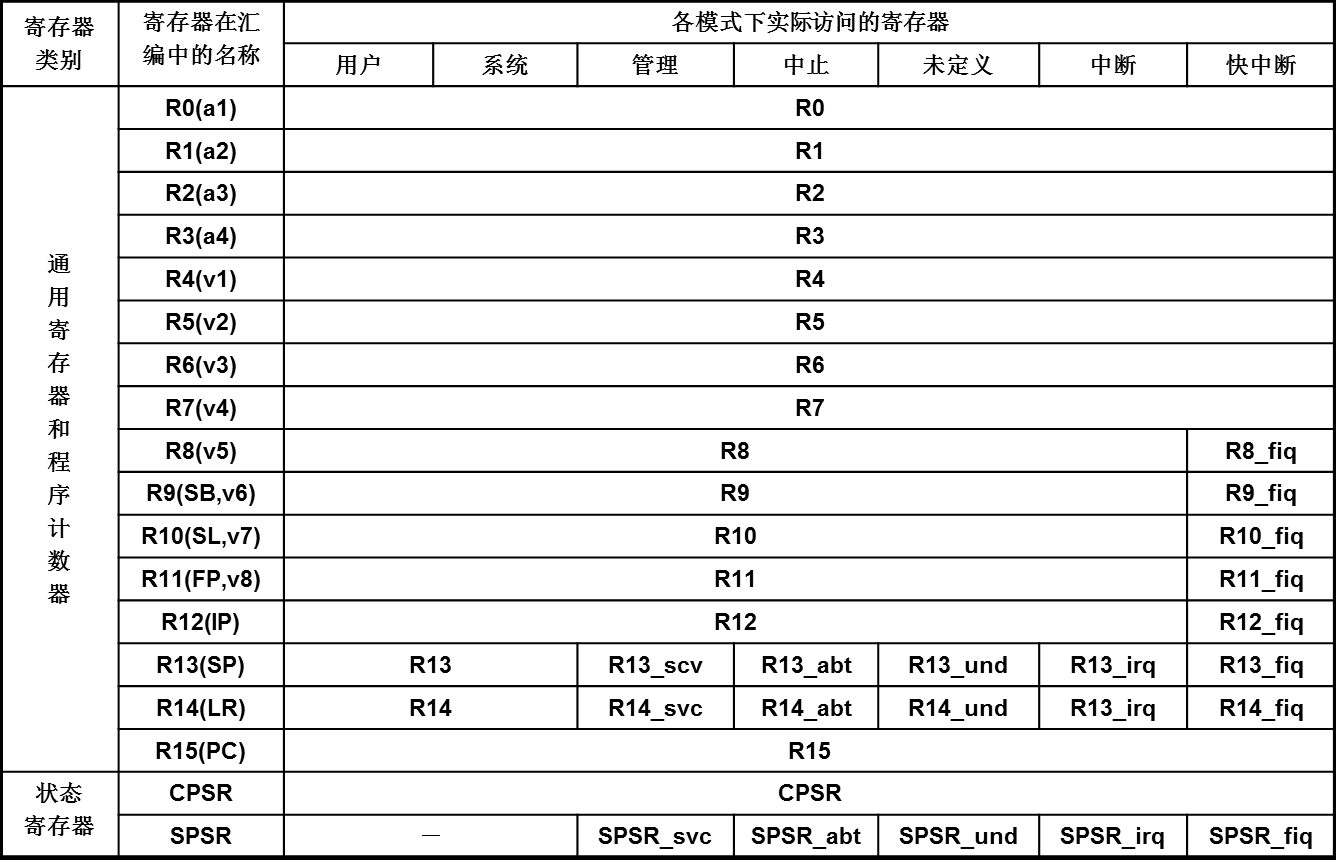

3 ARM的通用寄存器

CPU内的寄存器有两类,一类是通用寄存器,一类是外设使用的特殊功能寄存器(SFR)。这里讲述的是通用寄存器。CPU内部共有37个通用寄存器,但是在不同的模式下可以操作的寄存器是不同的,但每种模式下最多可以操作18个寄存器。如下图所示:

从上图中可以看出以下几点:

- a) 用户模式与系统模式共用一组寄存器。

- b) 5种异常模式有各自的R13、R14和SPSR。

- c) R13用作堆栈指针,故也叫SP;R14用作保存返回地址,故也叫链接寄存器LR;R15用作程序计数器,故也叫PC;CPSR记录当前CPU的状态;SPSR是CPSR的复制。

- d) 寄存器R8~R12有两个分组的物理寄存器。一个用于除FIQ模式之外的所有寄存器模式,另一个用于FIQ模式。在发生FIQ中断后,处理器不必为保护寄存器而浪费时间,从而加速了FIQ的处理速度。

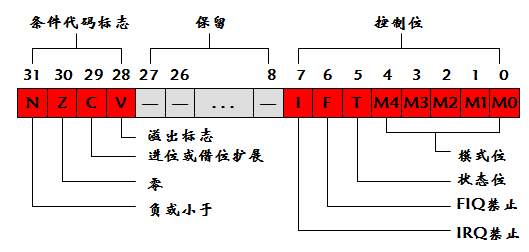

4 CPSR:当前程序状态寄存器

5是T位,切换处理器状态,0是ARM状态,1是Thumb状态;

6~7分别表示I,F中断禁止位,I= 1,禁止IRQ,F= 1,禁止FIQ;

M[0:4]位的定义如下:

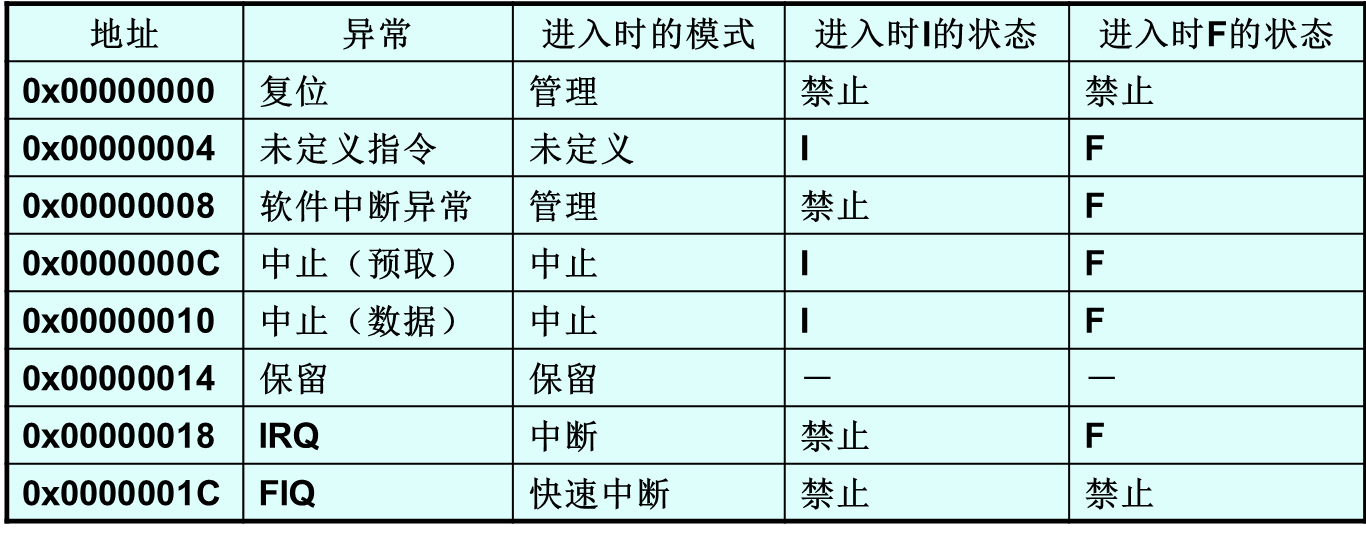

5 ARM的异常处理

异常向量表

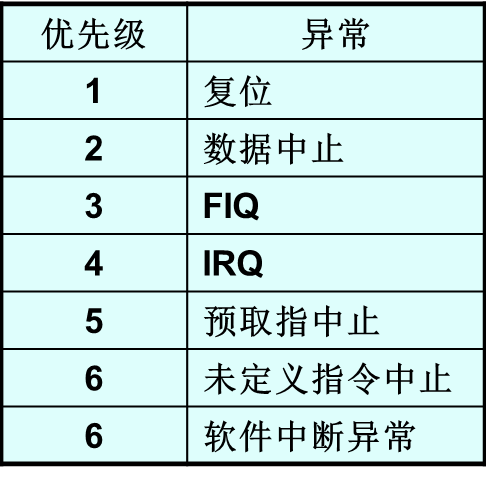

异常优先级

异常的进入:

当一个异常导致模式切换时,内核自动的做如下处理:

- 将异常处理程序的返回地址(加固定的偏移量)保存到相应异常模式下的LR;

- 将CPSR的当前值保存到相应异常模式下的SPSR;

- 设置CPSR为相应的异常模式;

- 设置PC为相应异常处理程序的中断入口向量地址,跳转到相应的异常中断处理程序执行;

异常的退出:

当异常处理程序结束时,异常处理程序必须:

- 返回到发生异常中断的指令的下一条指令处执行,即就是说将LR中的值减去偏移量后移入PC;

- 将SPSR的值复制回CPSR;清零在入口处置位的中断禁止标志。

383

383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?