2.11 VGA

2.11.1 信号定义

所有类型的COM Express模块都应当定义一个模拟VGA RGB接口,接口由3个模拟彩色信号(Red、Green、Blue)组成,数字水平和垂直同步信号,专用的I2C总线用于DDC获得监视器的性能参数。信号如表23:

| 信号 | 脚 | HDSUB5脚 | 描述 | I/O | 注释 |

| VGA_RED | B89 | 1 | VGA红色分量,驱动37.5欧姆负载 | O模拟 | 模拟输出 |

| VGA_GRN | B91 | 2 | VGA绿色分量,驱动37.5欧姆负载 | O模拟 | 模拟输出 |

| VGA_BLU | B92 | 3 | VGA兰色分量,驱动37.5欧姆负载 | O模拟 | 模拟输出 |

| VGA_HSYNC | B93 | 13 | VGA水平同步信号 | O 3.3V CMOS |

|

| VGA_VSYNC | B94 | 14 | VGA垂直同步信号 | O 3.3V CMOS |

|

| VGA_I2C_CK | B95 | 15 | DDC I2C时钟 | O 3.3V CMOS |

|

| VGA_I2C_DAT | B96 | 12 | DDC I2C数据 | I/O 3.3V CMOS |

|

| GND |

| 5,8,10 | 地 |

|

|

| DDC_POWER |

| 9 | DDC电源,用于监视器的EEPROM供电 |

| 电源 |

| N.C |

| 4,11 | 不连接 |

|

|

2.11.2 VGA连接器

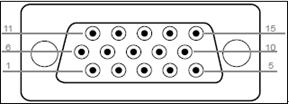

图26 VGA连接器HDSUB15

2.11.3 VGA参考设计

图27 VGA参考设计

2.11.4 布线考虑

2.11.4.1 RGB模拟信号

载板上R、G、B每个信号应该有一个150欧姆的下拉电阻,在监视器里应该有一个75欧姆的输入电阻。

RGB信号的频率高达350MHz,所以应该特别注意信号的完整性及EMI。应该有一个PI滤波器,如参考设计图所示,PI滤波器由两个10pF的电容和一个120欧姆@100MHz的磁珠构成。推荐把PI滤波器和终端电阻尽可能防止在VGA连接器附近。

2.11.4.2 HSYNC和VSYNC信号

COM Express模块输出的同步信号是3.3V的,因为VGA监视器可能驱动同步信号是5V,所以有必要使用高阻非双向的缓冲器。见参考设计图。

为了优化ESD保护,添加低容性钳位二极管到监视器的同步信号上,这些钳位二极管应该放在5V电源平面和地平面之间,并尽可能距离VGA插座近。

2.11.4.3 DDC接口

COM Express提供了一个专用I2C总线用于VGA接口,从而实现DDC借款,用来读出CRT监视器的特定扩展显示表示数据(EDID)。I2C总线也是3.3V的,而大部分DDC是5V的,所以放置100K欧姆的上来电阻在5V电源和每个DDC线之间。DDC接口的电平偏移电路被需要。

另外Schottky二极管必须放置在5V和DDC上拉电阻之间。

见参考设计原理图。

2.11.4.4 ESD保护/EMI接口

所有的VGA信号需要ESD保护和EMI滤波器。见参考设计。参考设计使用了CM2009这个芯片。很多其他的保护和电平偏移解决方案可以选择,如Semtech提供多种低容性的ESD抑制器件,比如RCLAMP502B。

2.13 AC’97和HDA数字音频接口

COM Express规范定义了7个信号,用于支持载板上的数字AC’97和HD接口芯片。HD音频使用同AC’97一样的数字信号接口。但AC’97和HD的Codec是不同的。

2.13.1 信号定义

表26 音频Codec信号描述

| 信号 | 脚 | 描述 | I/O |

| AC_RST# | A30 | CODEC复位 | O 3.3V Suspend CMOS |

| AC_SYNC | A29 | 串行采样速率同步 | O 3.3V CMOS |

| AC_BITCLK | A32 | CODEC的串行位时钟12.228MHz | O 3.3V CMOS |

| AC_SDOUT | A33 | 音频串行数据输出流 | O 3.3V CMOS |

| AC_SDIN0 AC_SDIN1 AC_SDIN2 | B30 B29 B28 | 来自CODEC[0:2]的音频串行数据输入流 | I 3.3V Suspend CMOS |

COM Express模块支持的音频接口在其手册上应该能够说明。如果模块仅支持AC’97接口,它就不可能支持HAD Codecs

某些COM模块既支持AC’97又支持HAD接口,这时,在模块的BIOS中应该有个选择,只能选择其一,不可能两个混合使用。

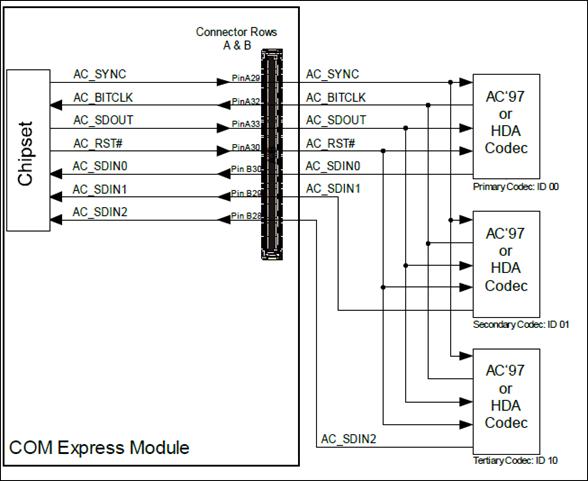

AC’97或HDA Codec通常作为主codec来连接,codec的ID是00,使用数据线AC_SDIN0,可以还有2个Codecs:ID:01(连接到AC_SDIN1),ID:10(连接到AC_SDIN1)。

连接主音频Codec到AC_SDIN0,确保对应的位时钟信号AC_BITCLK连接到模块AC’97/HDA接口。

AC_BITCLK由一个在AC97实现电路里的主CODEC的24.576MHz的晶体或晶体振荡器提供。这个晶体在HAD中并不要求,这个时钟也可以驱动第二个或第三个音频CODEC,如果有多个CODEC被使用。

注意:Intel915GM和945GM芯片集同时支持AC97和HAD格式。Intel965GM及之后的移动芯片集仅支持HDA。

图30 多个音频CODEC配置

2.13.2 参考设计

2.13.2.1 AC’97

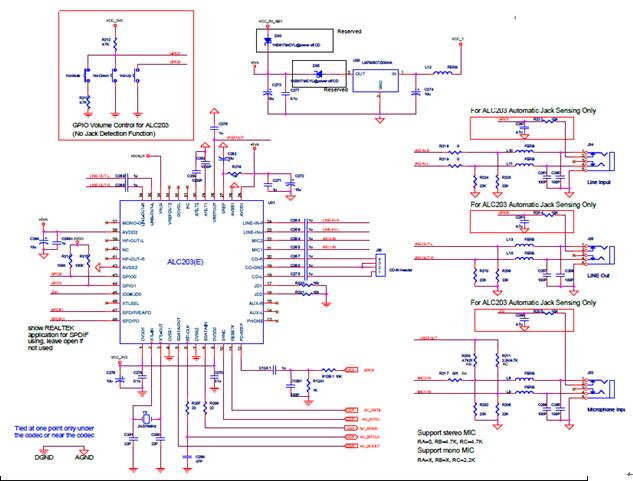

图31 AC’97参考设计

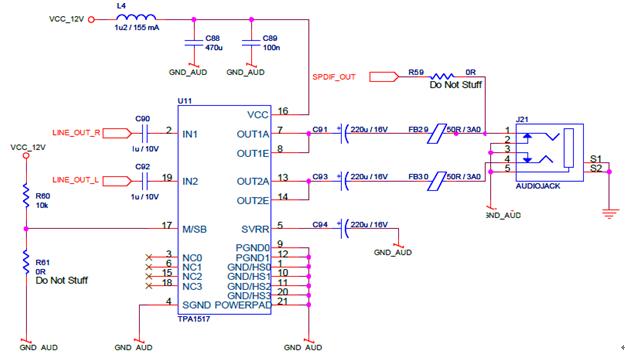

图32 音频放大器:

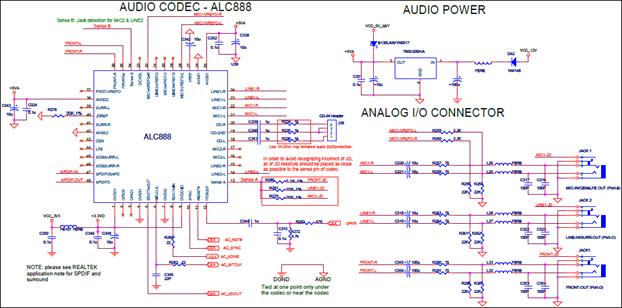

2.13.2.2 高清音频(HDA)

图33 HDA参考设计

2.13.3 布线考虑

良好的布局和布线有利于最大限度发挥音频CODEC性能。应该遵守下面的一些规则:

线的目标阻抗是55欧姆+-15%

模拟信号的地返回路径必须给与特别考虑。

接近模拟音频信号的数字信号一定不要跨过电源平面走线。尽量远分开模拟和数字信号。

把载板的模拟电路和数字电路分开。

使数字信号特别是时钟信号远离模拟输入和电压参考脚。

提供独立的模拟和数字地平面。并且模拟器件在模拟地平面之上,数字器件在数字地平面之上;在模拟平面之上布模拟信号线,同样在数字平面之上布数字信号线。两个地平面必须分开0.05英寸宽的间隙。

旁路和去藕电容的位置应该尽可能离IC脚近。

晶体应该尽可能离CODEC近。HDA通常在CODEC上并不要求晶体。

不要完全隔离模拟/音频地平面同载板的地平面。提供一个单点(0.25到0.5英寸宽),在此处,模拟/绝缘的地平面连接到主地平面。

任何信号都不要跨越两个地平面的间隙。因为这会引起地回环,这会引起很大的EMI噪声,从而降低模拟和数字信号的质量。

3534

3534

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?