ar9300EepromDumpSupport

|===================== Header Information ====================|

| Major Version 3 | Minor Version 3328 |

|-------------------------------------------------------------|

| Checksum 0x007F | Length 0x0202 |

| RegDomain 1 0x0030 | RegDomain 2 0x3A30 |

| TX Mask 0x003A | RX Mask 0x0034 |

| rfSilent 0x3035 | btOptions 0x3A30 |

| deviceCap 0x3600 | |

| MacAddress: 0x32:3A:30:33:3A:30 |

| OpFlags: [0x22] 11A 0, 11G 1 |

| OpFlags: Disable 5HT40 0, Disable 2HT40 0 |

| OpFlags: Disable 5HT20 0, Disable 2HT20 1 |

| eepMisc: [0x0a] endian 0 |

| Cal Bin Maj Ver 0 Cal Bin Min Ver 0 Cal Bin Build 0 |

| Device Type: UNKNOWN [0] |

| Customer Data in hex |

|= 50 01 50 00 00 00 00 00 00 1C 00 A4 00 00 00 00 =|

|= FF 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0D =|

|= 0E 0E 03 00 2C E2 00 02 0E 1C 0C 00 E0 E0 00 00 =|

|= E0 E0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 =|

|=============================================================|

|=========== 2GHz Modal Header ===========|

| Ant Chain 0 0x34323230 |

| Ant Chain 1 0x34323230 |

| Ant Chain 2 0x34343432 |

| Ant Chain common 0x32303432 |

| Antenna Gain Chain 0 50 |

| Antenna Gain Chain 1 48 |

| Antenna Gain Chain 2 52 |

| Switch Settling 50 |

| TxRxAttenuation Ch 0 50 |

| TxRxAttenuation Ch 1 48 |

| TxRxAttenuation Ch 2 52 |

| RxTxMargin Chain 0 52 |

| RxTxMargin Chain 1 52 |

| RxTxMargin Chain 2 50 |

| adc desired size 50 |

| pga desired size 48 |

| xlna gain Chain 0 52 |

| xlna gain Chain 1 50 |

| xlna gain Chain 2 50 |

| tx end to xpa off 48 |

| tx end to rx on 52 |

| tx frame to xpa on 50 |

| thresh62 50 |

| noise floor thres 0 48 |

| noise floor thres 1 52 |

| noise floor thres 2 52 |

| Xpd Gain Mask 0x34 |

| Xpd extern 50 |

| IQ Cal I, Q Chain 0 50, 50 |

| IQ Cal I, Q Chain 1 48, 50 |

| IQ Cal I, Q Chain 2 52, 48 |

| pdGain Overlap 26.0 dB |

| Analog Output Bias (ob) 50 |

| Analog Driver Bias (db) 50 |

| Xpa bias level 48 |

| Xpa bias level freq 0 0X3230 |

| Xpa bias level freq 1 0X3432 |

| Xpa bias level freq 2 0X3230 |

| pwr dec 2 chain 26.0 dB |

| pwr dec 3 chain 26.0 dB |

| txFrameToDataStart 52 |

| txFrameToPaOn 50 |

| ht40PowerIncForPdadc 50 |

| bswAtten Chain 0 48 |

| bswAtten Chain 1 52 |

| bswAtten Chain 2 50 |

| bswMargin Chain 0 50 |

| bswMargin Chain 1 48 |

| bswMargin Chain 2 52 |

| switch settling HT40 50 |

|=========================================|

|========================== Spur Information =========================|

| 11G Spurs in MHz (Range of 0 defaults to channel width) |

| 4073.5 | 3662.3 | 6721.6 | 6721.6 | 6721.6 |

|< 4.9-=- 5.0>|<11.2-=-11.7>|<11.2-=-11.7>|<11.2-=-11.7>|<11.2-=-11.7>|

|=====================================================================|

|================== Power Calibration Information Chain 1 =================|

|================== pdadc pwr(dBm) =================|

| 2472 | 2484 | 2412 | 2417 | |

|==============|==============|==============|==============|==============|

| | | | | |

| PD_Gain 2 | | | | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| | | | | |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G CCK | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| 1 | 0.0 | 0.0 | 0.0 |

| 2 | 0.0 | 0.0 | 0.0 |

| 5.5 | 0.0 | 0.0 | 0.0 |

| 11 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G OFDM | 2300 | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| 6-24 | 0.0 | 0.0 | 0.0 | 0.0 |

| 36 | 0.0 | 0.0 | 0.0 | 0.0 |

| 48 | 0.0 | 0.0 | 0.0 | 0.0 |

| 54 | 0.0 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G HT20 | 2300 | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| HT MCS0 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS1 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS2 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS3 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS4 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS5 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS6 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS7 | 0.0 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G HT40 | 2300 | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| HT MCS0 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS1 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS2 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS3 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS4 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS5 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS6 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS7 | 0.0 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

|===================== Header Information ====================|

| Major Version 3 | Minor Version 3328 |

|-------------------------------------------------------------|

| Checksum 0x007F | Length 0x0202 |

| RegDomain 1 0x0030 | RegDomain 2 0x3A30 |

| TX Mask 0x003A | RX Mask 0x0034 |

| rfSilent 0x3035 | btOptions 0x3A30 |

| deviceCap 0x3600 | |

| MacAddress: 0x32:3A:30:33:3A:30 |

| OpFlags: [0x22] 11A 0, 11G 1 |

| OpFlags: Disable 5HT40 0, Disable 2HT40 0 |

| OpFlags: Disable 5HT20 0, Disable 2HT20 1 |

| eepMisc: [0x0a] endian 0 |

| Cal Bin Maj Ver 0 Cal Bin Min Ver 0 Cal Bin Build 0 |

| Device Type: UNKNOWN [0] |

| Customer Data in hex |

|= 50 01 50 00 00 00 00 00 00 1C 00 A4 00 00 00 00 =|

|= FF 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0D =|

|= 0E 0E 03 00 2C E2 00 02 0E 1C 0C 00 E0 E0 00 00 =|

|= E0 E0 00 00 00 00 00 00 00 00 00 00 00 00 00 00 =|

|=============================================================|

|=========== 2GHz Modal Header ===========|

| Ant Chain 0 0x34323230 |

| Ant Chain 1 0x34323230 |

| Ant Chain 2 0x34343432 |

| Ant Chain common 0x32303432 |

| Antenna Gain Chain 0 50 |

| Antenna Gain Chain 1 48 |

| Antenna Gain Chain 2 52 |

| Switch Settling 50 |

| TxRxAttenuation Ch 0 50 |

| TxRxAttenuation Ch 1 48 |

| TxRxAttenuation Ch 2 52 |

| RxTxMargin Chain 0 52 |

| RxTxMargin Chain 1 52 |

| RxTxMargin Chain 2 50 |

| adc desired size 50 |

| pga desired size 48 |

| xlna gain Chain 0 52 |

| xlna gain Chain 1 50 |

| xlna gain Chain 2 50 |

| tx end to xpa off 48 |

| tx end to rx on 52 |

| tx frame to xpa on 50 |

| thresh62 50 |

| noise floor thres 0 48 |

| noise floor thres 1 52 |

| noise floor thres 2 52 |

| Xpd Gain Mask 0x34 |

| Xpd extern 50 |

| IQ Cal I, Q Chain 0 50, 50 |

| IQ Cal I, Q Chain 1 48, 50 |

| IQ Cal I, Q Chain 2 52, 48 |

| pdGain Overlap 26.0 dB |

| Analog Output Bias (ob) 50 |

| Analog Driver Bias (db) 50 |

| Xpa bias level 48 |

| Xpa bias level freq 0 0X3230 |

| Xpa bias level freq 1 0X3432 |

| Xpa bias level freq 2 0X3230 |

| pwr dec 2 chain 26.0 dB |

| pwr dec 3 chain 26.0 dB |

| txFrameToDataStart 52 |

| txFrameToPaOn 50 |

| ht40PowerIncForPdadc 50 |

| bswAtten Chain 0 48 |

| bswAtten Chain 1 52 |

| bswAtten Chain 2 50 |

| bswMargin Chain 0 50 |

| bswMargin Chain 1 48 |

| bswMargin Chain 2 52 |

| switch settling HT40 50 |

|=========================================|

|========================== Spur Information =========================|

| 11G Spurs in MHz (Range of 0 defaults to channel width) |

| 4073.5 | 3662.3 | 6721.6 | 6721.6 | 6721.6 |

|< 4.9-=- 5.0>|<11.2-=-11.7>|<11.2-=-11.7>|<11.2-=-11.7>|<11.2-=-11.7>|

|=====================================================================|

|================== Power Calibration Information Chain 1 =================|

|================== pdadc pwr(dBm) =================|

| 2472 | 2484 | 2412 | 2417 | |

|==============|==============|==============|==============|==============|

| | | | | |

| PD_Gain 2 | | | | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| 0 0.00 | 0 0.00 | 0 0.00 | 0 0.00 | |

| | | | | |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G CCK | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| 1 | 0.0 | 0.0 | 0.0 |

| 2 | 0.0 | 0.0 | 0.0 |

| 5.5 | 0.0 | 0.0 | 0.0 |

| 11 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G OFDM | 2300 | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| 6-24 | 0.0 | 0.0 | 0.0 | 0.0 |

| 36 | 0.0 | 0.0 | 0.0 | 0.0 |

| 48 | 0.0 | 0.0 | 0.0 | 0.0 |

| 54 | 0.0 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G HT20 | 2300 | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| HT MCS0 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS1 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS2 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS3 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS4 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS5 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS6 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS7 | 0.0 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

============================Target Power Info===============================

| 2G HT40 | 2300 | 2300 | 2300 | 2300 |

|==============|==============|==============|==============|==============|

| HT MCS0 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS1 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS2 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS3 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS4 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS5 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS6 | 0.0 | 0.0 | 0.0 | 0.0 |

| HT MCS7 | 0.0 | 0.0 | 0.0 | 0.0 |

|==============|==============|==============|==============|==============|

=======================Test Group Band Edge Power========================

上面的数据是读取驱动的数据而来;其代码为:

ar9300EepromDumpSupport(struct ath_hal *ah, void **ppE)

{

printk("ar9300EepromDumpSupport \n");

*ppE = &(AH9300(ah)->ah_eeprom);

return sizeof(ar9300_eeprom_t);

}

上面的可以知道,获取的是结构体

typedef struct ospreyEeprom {

u_int8_t eepromVersion;

u_int8_t templateVersion;

u_int8_t macAddr[6];

u_int8_t custData[OSPREY_CUSTOMER_DATA_SIZE];

OSPREY_BASE_EEP_HEADER baseEepHeader;

OSPREY_MODAL_EEP_HEADER modalHeader2G;

OSPREY_BASE_EXTENSION_1 base_ext1;

u_int8_t calFreqPier2G[OSPREY_NUM_2G_CAL_PIERS];

OSP_CAL_DATA_PER_FREQ_OP_LOOP calPierData2G[OSPREY_MAX_CHAINS][OSPREY_NUM_2G_CAL_PIERS];

u_int8_t calTarget_freqbin_Cck[OSPREY_NUM_2G_CCK_TARGET_POWERS];

u_int8_t calTarget_freqbin_2G[OSPREY_NUM_2G_20_TARGET_POWERS];

u_int8_t calTarget_freqbin_2GHT20[OSPREY_NUM_2G_20_TARGET_POWERS];

u_int8_t calTarget_freqbin_2GHT40[OSPREY_NUM_2G_40_TARGET_POWERS];

CAL_TARGET_POWER_LEG calTargetPowerCck[OSPREY_NUM_2G_CCK_TARGET_POWERS];

CAL_TARGET_POWER_LEG calTargetPower2G[OSPREY_NUM_2G_20_TARGET_POWERS];

OSP_CAL_TARGET_POWER_HT calTargetPower2GHT20[OSPREY_NUM_2G_20_TARGET_POWERS];

OSP_CAL_TARGET_POWER_HT calTargetPower2GHT40[OSPREY_NUM_2G_40_TARGET_POWERS];

u_int8_t ctlIndex_2G[OSPREY_NUM_CTLS_2G];

u_int8_t ctl_freqbin_2G[OSPREY_NUM_CTLS_2G][OSPREY_NUM_BAND_EDGES_2G];

OSP_CAL_CTL_DATA_2G ctlPowerData_2G[OSPREY_NUM_CTLS_2G];

OSPREY_MODAL_EEP_HEADER modalHeader5G;

OSPREY_BASE_EXTENSION_2 base_ext2;

u_int8_t calFreqPier5G[OSPREY_NUM_5G_CAL_PIERS];

OSP_CAL_DATA_PER_FREQ_OP_LOOP calPierData5G[OSPREY_MAX_CHAINS][OSPREY_NUM_5G_CAL_PIERS];

u_int_t calTarget_freqbin_5G[OSPREY_NUM_5G_20_TARGET_POWERS];

u_int8_t calTarget_freqbin_5GHT20[OSPREY_NUM_5G_20_TARGET_POWERS];

u_int8_t calTarget_freqbin_5GHT40[OSPREY_NUM_5G_40_TARGET_POWERS];

CAL_TARGET_POWER_LEG calTargetPower5G[OSPREY_NUM_5G_20_TARGET_POWERS];

OSP_CAL_TARGET_POWER_HT calTargetPower5GHT20[OSPREY_NUM_5G_20_TARGET_POWERS];

OSP_CAL_TARGET_POWER_HT calTargetPower5GHT40[OSPREY_NUM_5G_40_TARGET_POWERS];

u_int8_t ctlIndex_5G[OSPREY_NUM_CTLS_5G];

u_int8_t ctl_freqbin_5G[OSPREY_NUM_CTLS_5G][OSPREY_NUM_BAND_EDGES_5G];

OSP_CAL_CTL_DATA_5G ctlPowerData_5G[OSPREY_NUM_CTLS_5G];

} __packed ar9300_eeprom_t;

其中这个&(AH9300(ah)->ah_eeprom 地址的值是怎么来的了,这里要加一个打印信息来看看代码的执行流程,目前有一点可以确认的是,WiFi的MAC地址的值来自于上面的macAddr 这个字段。

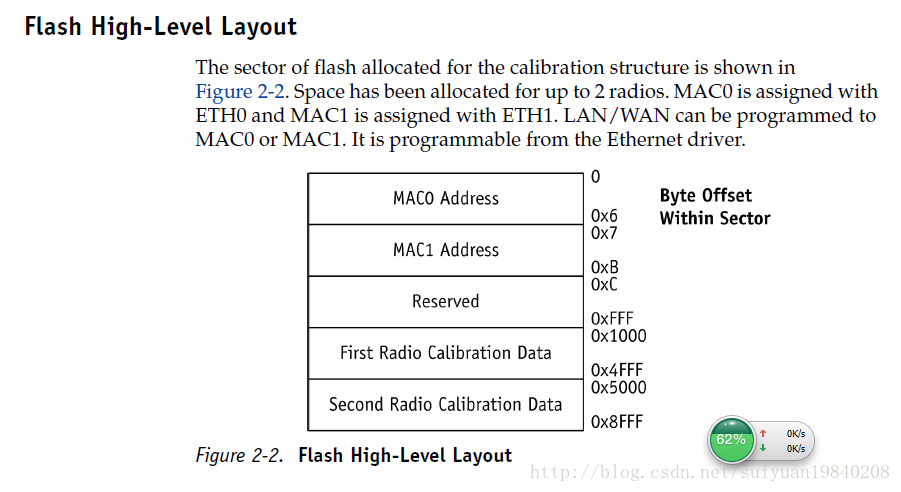

2:分区数据格式

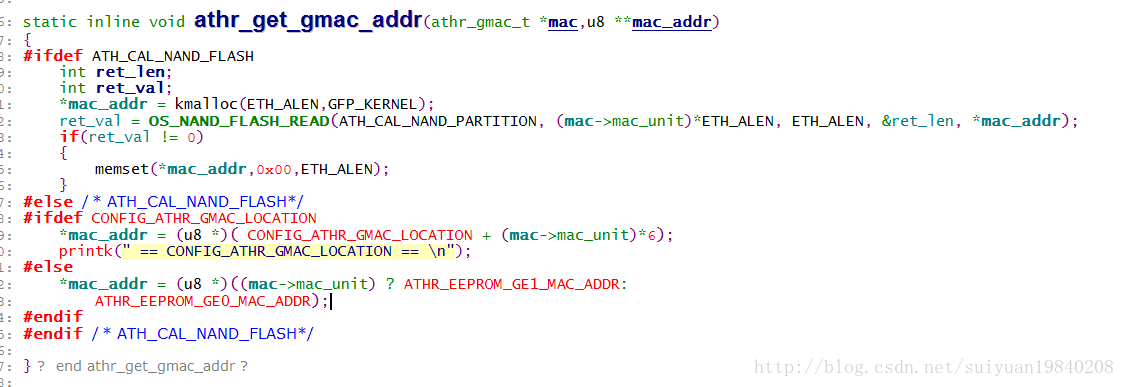

有上面的可以知道,在此分区的最前面的字节可以用来定义MAC地址,为Atheros Ethernet的MAC地址。在其代码

默认的MAC地址从地址:CONFIG_ATHR_GMAC_LOCATION 处来进行获取,CONFIG_ATHR_GMAC_LOCATION的定义如下:

#define CONFIG_AG7240_MAC_LOCATION 0xbfff0000

185

185

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?