问题描述:Xilinx FPGA新手,Xilinx又出了个vivado,比ISE安装占的空间小,但是对芯片的支持不如ISE多。估计是ISE为了兼容之前的许多功能,导致越来越大了吧。开始不知道是直接用vivado还是先从ISE入手Xilinx FPGA,毕竟vivado以后是趋势,会替代掉ISE了的,但是估计关于vivado的资料不会特别多。考虑刚入门,于是先在Xilinx官网将vivado for windows和ISE for windows的安装包都下载了下来。先安装了ISE进行入门的学习了。

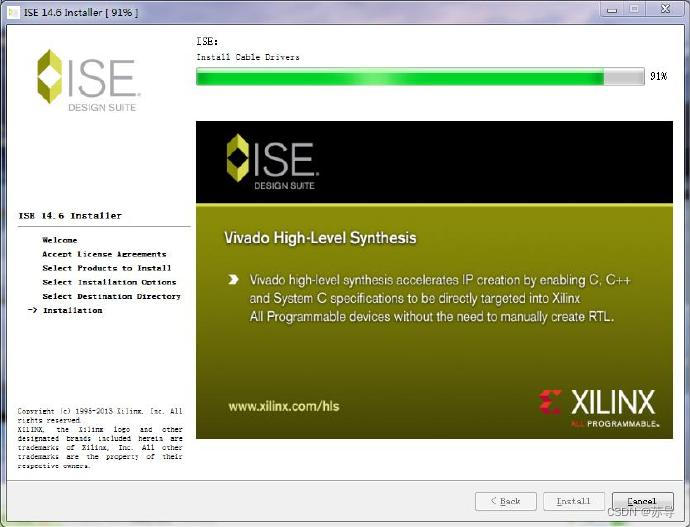

安装完成后会提示添加license,当前版本是试用版本的。具体的将试用版变成专业版可以上网搜索下解决办法。

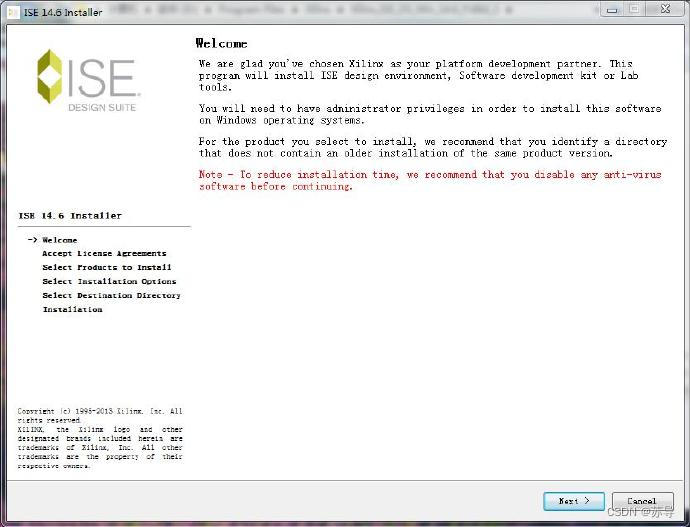

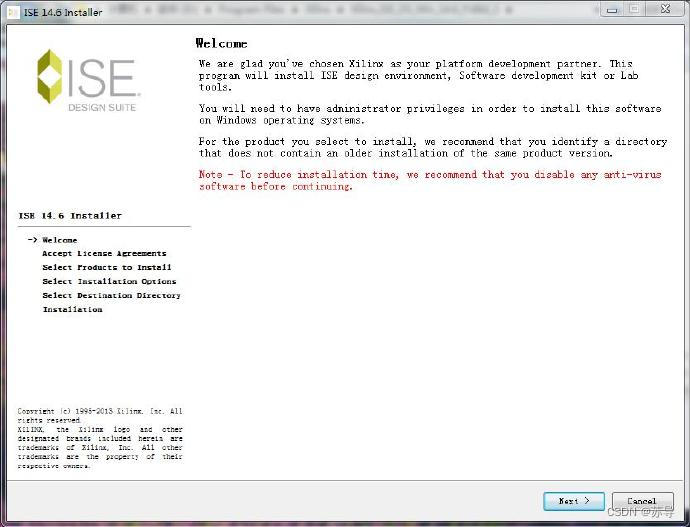

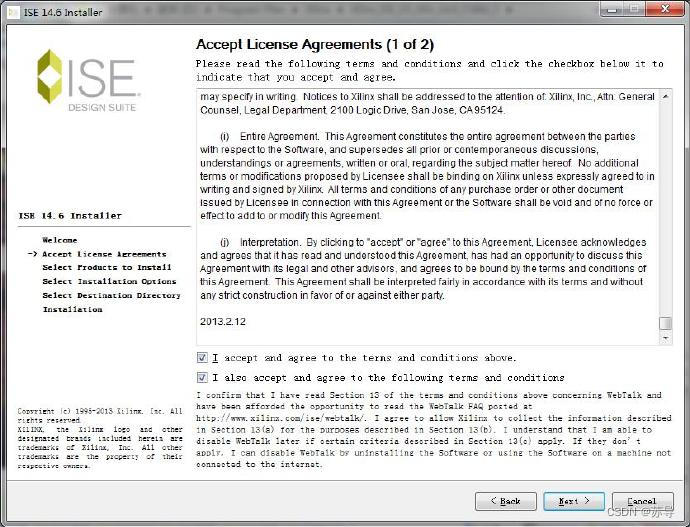

安装过程:

下载Xilinx官网的安装包可能会要求先下载一个java下载器,下载完成即可(下载的是ISE系统版本,下载完成的安装包大小为5.88G,真够多的)。然后解压要安装的ISE那个安装包,解压完双击xsetup.exe开始ISE的安装之旅了。

准备工作:首先将其他的程序关闭,比如杀毒软件(安装过程中可能提示发生错误--可能由磁盘空间不足引起,实际可能是杀毒软件的影响造成的),将连接的USB接口的比如JTAG线,U盘等拔掉,不然会导致USB线驱动安装失败。

以下是安装过程中的几个画面,注意安装路径要用全英文,不要有特殊字符和空格。

安装完成后会提示添加license,当前版本是试用版本的。具体的将试用版变成专业版可以上网搜索下解决办法。

2716

2716

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?