当判决树有特权编码时应该利用if/else结构。

另一方面,case结构常常利用在所有条件互不相容的情况。为了在verilog中实现完全相同的功能,一个case语句可以利用。

case(1)

ctrl[0]: rout<=in[0];

ctrl[1]: rout<=in[1];

ctrl[2]: rout<=in[2];

ctrl[3]: rout<=in[3];

endcase

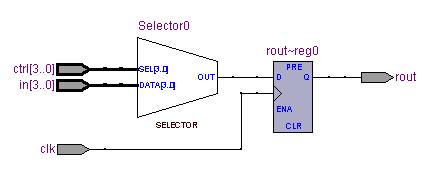

由于case语句是if/else结构的一个有效替代的事实,许多初学者以为这是自动地无特权判决树实现,对于更严格的VHDL语言这个碰巧是正确的,但是对verilog不是这样,可以在下图中看到verilog的具体实现图。

默认的是特权被译码来设置多路选择器上相应的使能引脚,这导致许多设计者落入陷阱。为了去除这个特权编码,利用综合的伪指令“parallel_case”来实现真正的并行结构。但是并不提倡这么做。去除特权后的结构图如下:

如果case语句的条件没有一个是成立的,综合工具已经把寄存器的输出返回送到判决树作为一个缺省条件。对设计者来说,一个好的习惯是显式给出缺省条件,这个缺省可能或不可能是当前数值,它避免了工具自动地锁存当前值。

一个类似于parallel_case语句的综合伪指令是full_case伪指令。这个伪指令通知综合工具,所有的情况已经覆盖,不要求一个隐含的缺省条件。不过,这同样是不推荐使用的,会带来风险,因为用这些伪指令会引起仿真和综合之间的失配。下面是同时使用full_case和parallel_case的结构图:

483

483

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?