调试ds2781的时候可谓艰难啊,但是调完了一个模拟的iic时序之后单总线的时序竟然迎刃而解了。

下面总结一下调试的过程:

我使用ds2781的快速模式(OVD高电平)

1. 首先要有一个芯片的datasheet

这里写链接内容

2. 其次测试设备:示波器,逻辑分析仪

3. 根据手册上的时序写代码进行调试

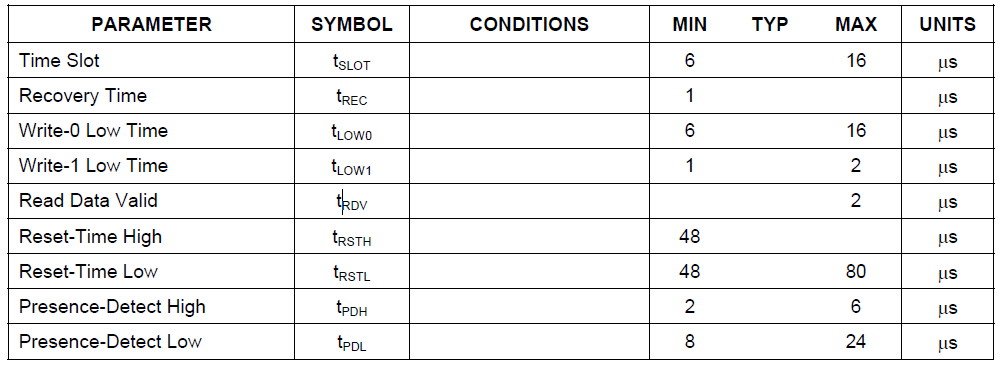

时隙

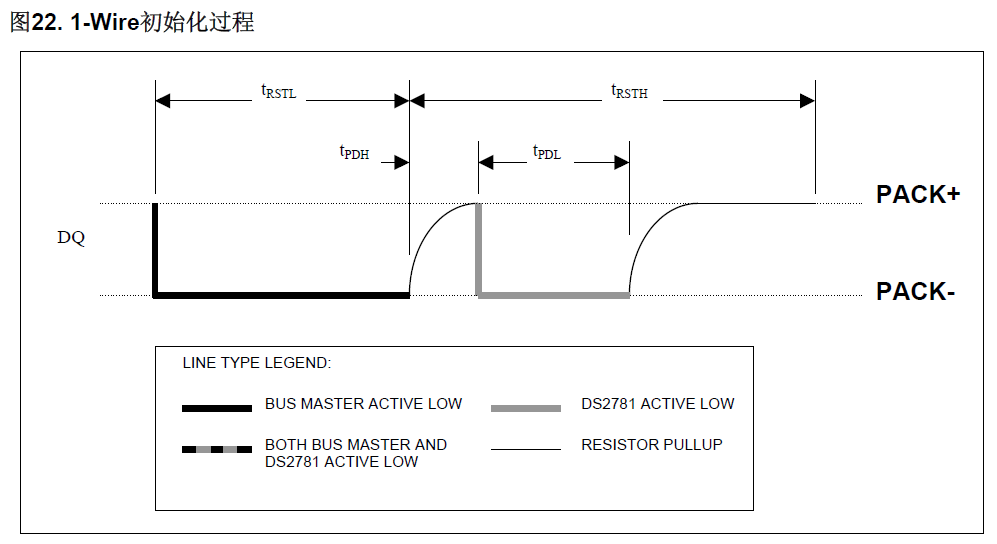

复位时序

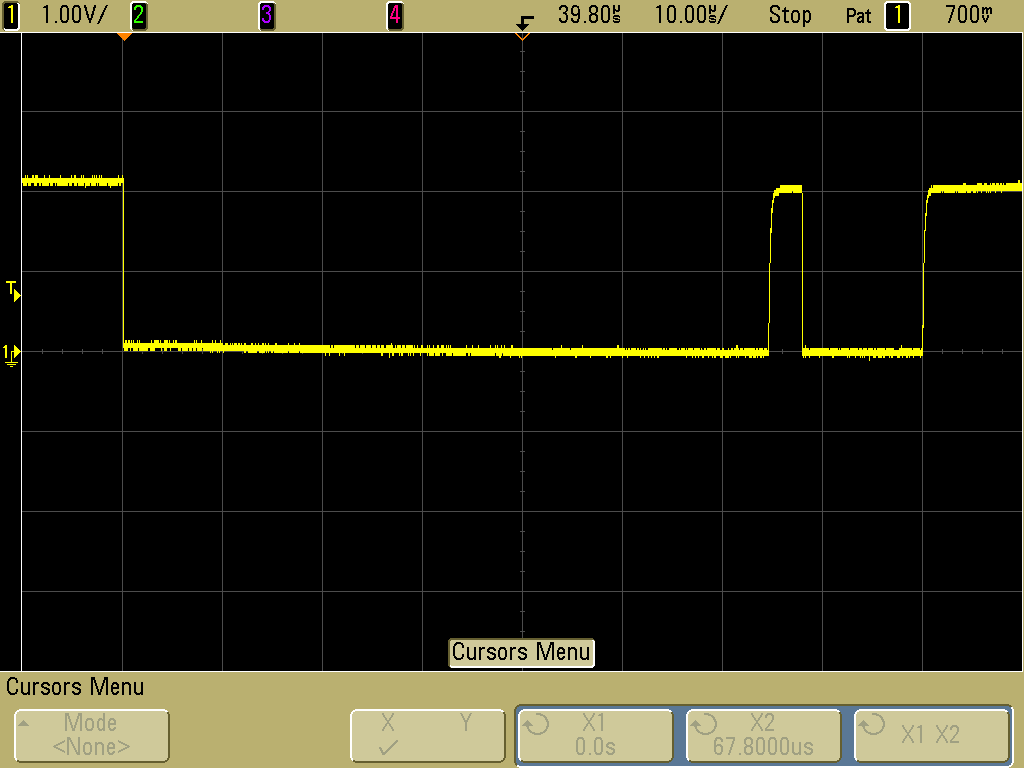

关于与复位时序,手册说明:

与DS2781的任何通信都必须从初始化过程开始,如上图所示。复位脉冲之后的在线应答脉冲表明DS2781已经准备

好接收网络地址命令。总线主机发出 (Tx) 持续tRSTL时间的复位脉冲。然后总线主机释放数据线,进入接收模式

(Rx)。然后由上拉电阻将1-Wire总线拉至高电平。DS2781检测到DQ引脚的上升沿后,将等待tPDH时间,然后发出持

续时间为tPDL的在线应答脉冲。

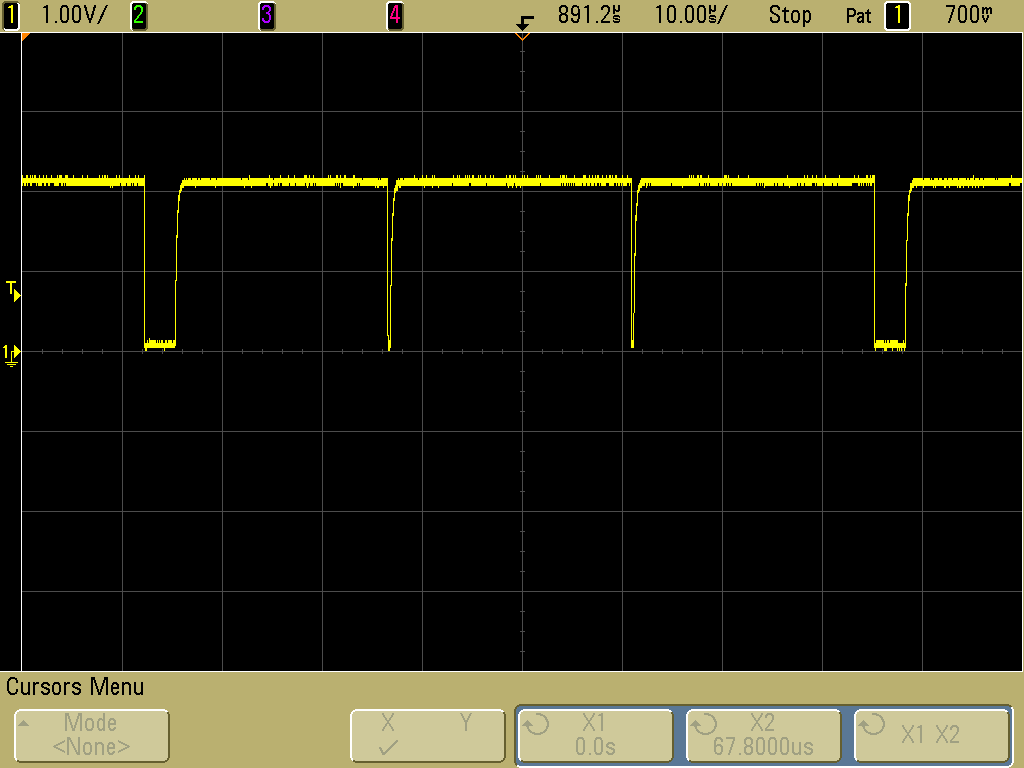

我调试的时候的复位波形是这样的:

要对照着时隙,我的三个参数分别是:65us,3us,12us。对应手册的 48-80us,2-6us,8-24us。

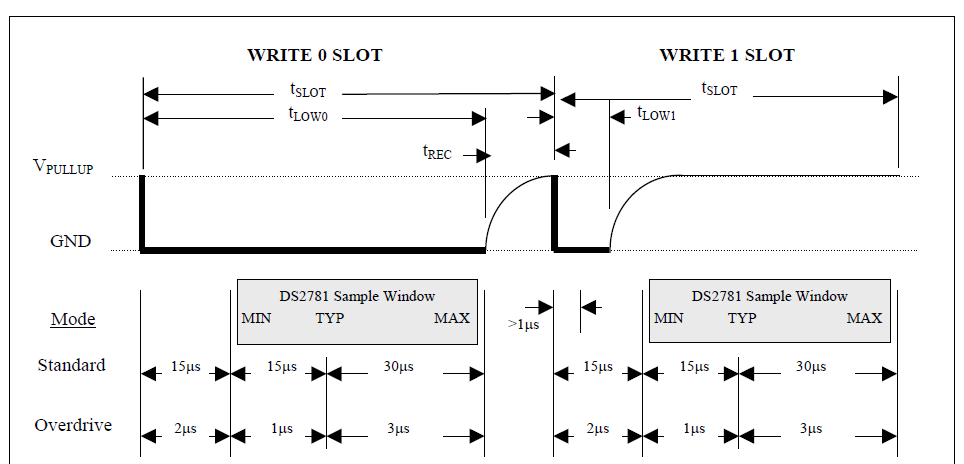

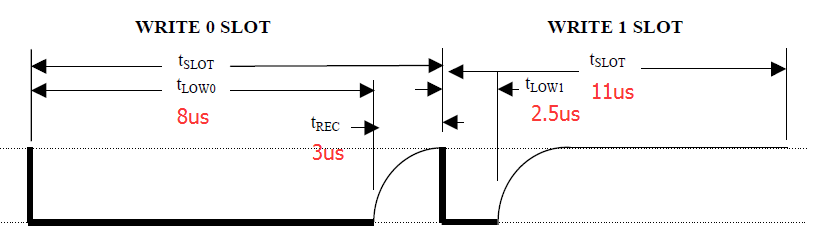

写0写1时序

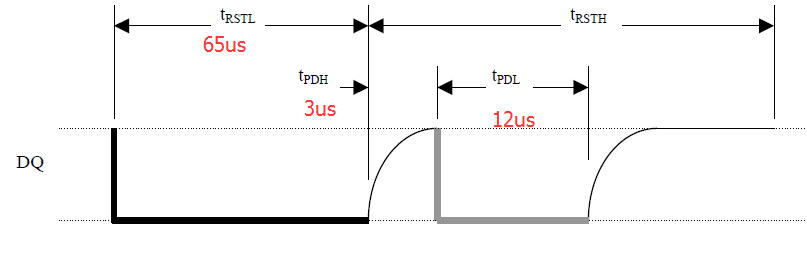

关于写时序,手册上这样说明:

当总线主机将1-Wire总线从逻辑高 (无效) 电平拉至逻辑低电平时,开始写时隙。写时隙有两种类型:写1和写0。所

有写时隙必须保持tSLOT的时间,并且两个写时隙之间需要1μs的最小恢复时间 (tREC)。DS2781将在线路下降沿之后的

15μs至60μs之间 (高速模式下在2μs至6μs之间) 采样1-Wire总线数据。如果采样时总线为高电平,则为写1时隙。如

果采样时总线为低电平,则为写0时隙 (参见图23)。总线主机若要产生写1时隙,必须先拉低总线,然后释放,在写

时隙开始后的15μs (高速模式下为2μs) 之内将总线拉至高电平。主机若要产生写0时隙,必须拉低总线,并在写时隙

持续时间内保持为低电平。

我调试的时候的波形是这样的:

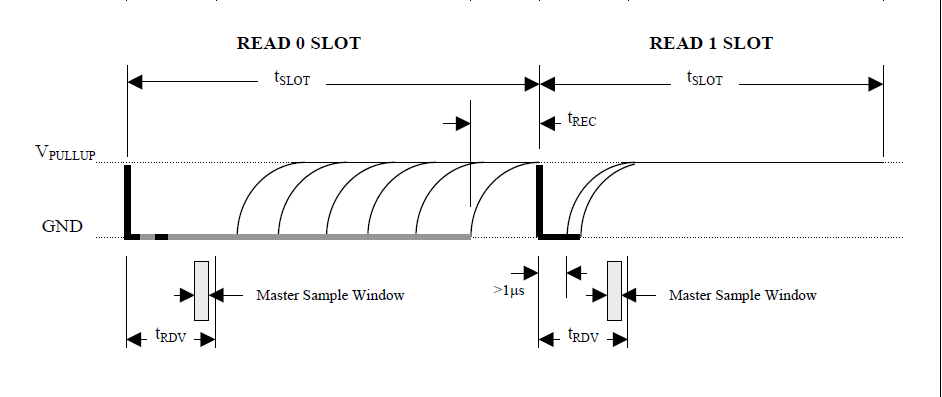

读0读1时序

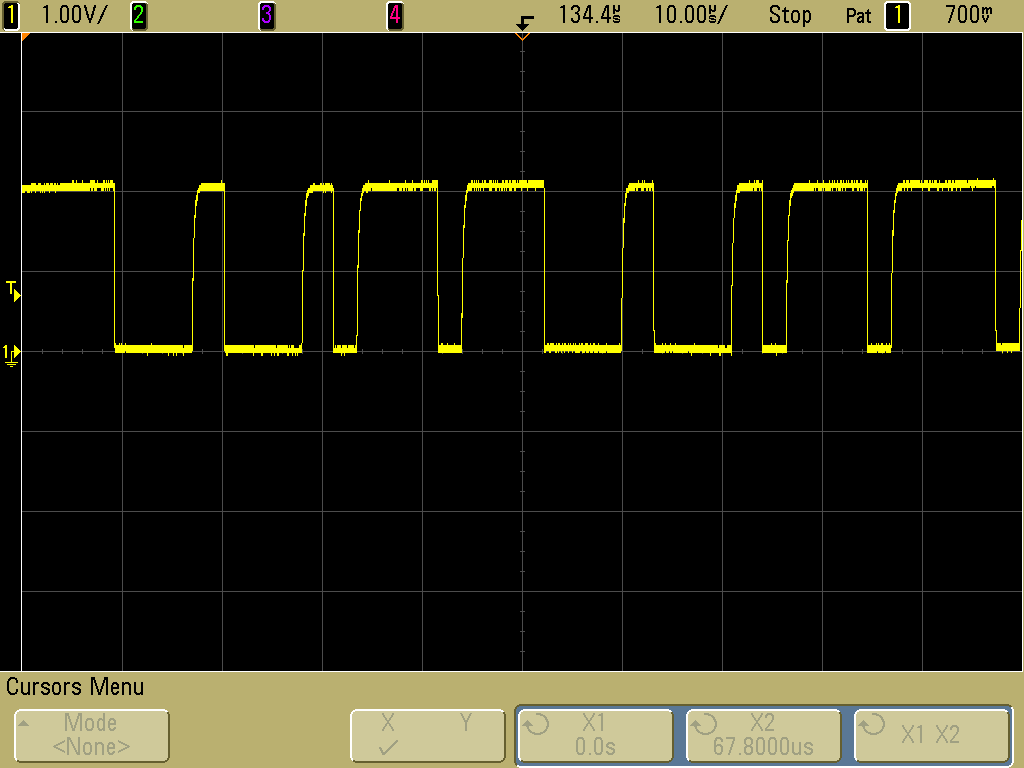

关于读时序手册是这样说明的

当总线主机将1-Wire总线从逻辑高电平拉至逻辑低电平时,开始读时隙。总线主机必须使总线为低电平的时间至少持

续1μs,然后再释放总线,使DS2781输出有效数据。总线主机在读时隙开始后的tRDV时间内采样数据。DS2781在读

时隙结束时释放总线,允许外部上拉电阻将其拉至高电平。所有读时隙必须持续tSLOT,并且在两次读时隙之间需要

1μs的最小恢复时间 (tREC)。详细信息参见图23。

我调试的时候的波形是这样的:

按照实际的波形 tRDV 在小于3us内都是可以读出来的

- 调整时序

如果应答信号收不到,那么仔细调整时序,如果在硬件没有问题的情况下,时序对了就可以正常读数的,因此要仔细调整时序。

[源码](http://download.csdn.net/detail/a912293097/9054963 “csdn下载界面”)

1487

1487

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?