一般来说,我们学习一款新的单片机或者ARM芯片,首先都会研究他的时钟系统。本文基于国嵌的视频教程,总结一下ARM时钟体系架构。

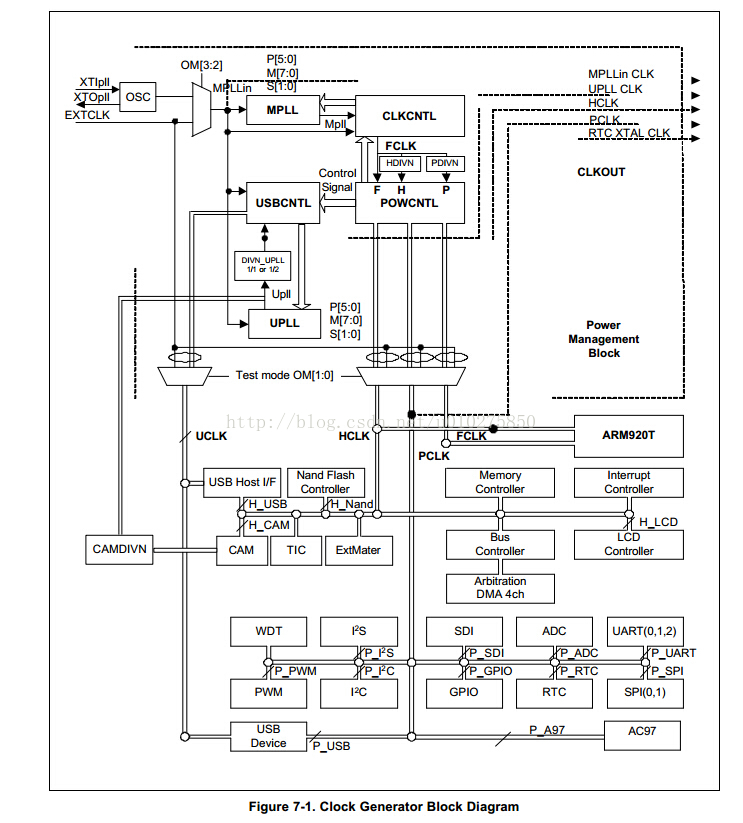

其实学过单片机的同学尤其是基于ARM内核的单片机,对于系统时钟的理解并不困难。S3C2440的系统时钟框图如下图所示:

时钟源则是由外部12MHz或者16.9344MHz的晶振提供,经过PLL倍频电路最大可将主系统时钟即FCLK提高至533MHz,PLL电路又主要分为俩个,一个是UPLL,另一个则是MPLL。UPLL提供的时钟主要是UCLK,用于USB设备。而MPLL提供的时钟经由分频器分成FCLK,HCLK,PCLK。FCLK主要为arm内核提供稳定的时钟,FCLK再次经由分频器分出HCLK(AHB总线时钟)和PCLK(APB外设总线时钟)。

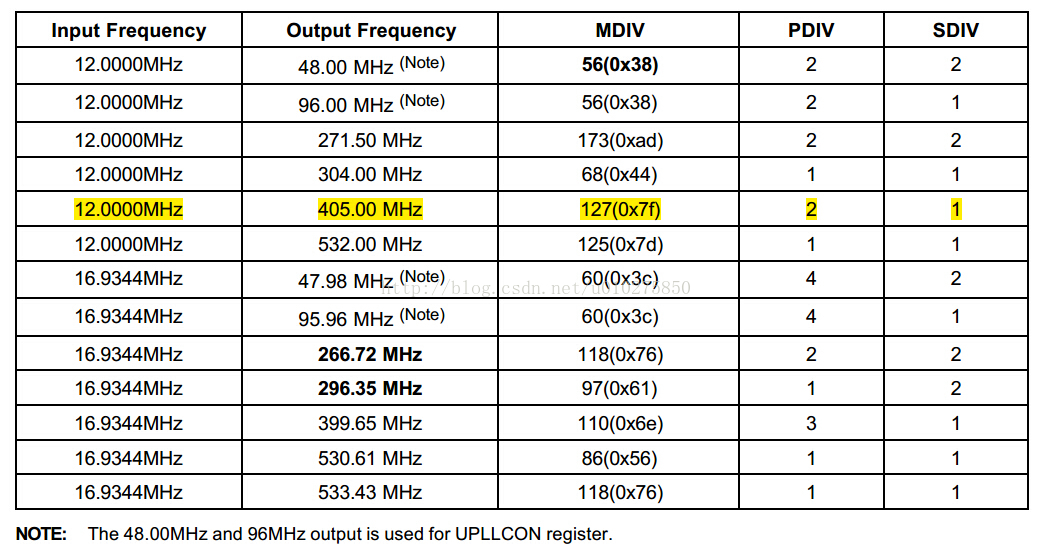

晶振、分频系数和FCLK的关系如下图所示:

至于系统时钟初始化主要分为以下几步:

关于LockTime的设置,可以略去采用默认配置,而分频系数则采用上图中黄色高亮显示的配置,FCLK运行在405MHz。具体代码如下:

#define CLKDIVN 0x4c000014

#define MPLLCON 0x4c000004

#define MPLL_405MHz ((127<<12)|(2<<4)|(1<<0))

clock_init:

@set clock divide factor

ldr r0,=CLKDIVN

mov r1,#0x5 @set HDIVN=2 PDIVN=1

str r1,[r0]

@set asynchronous work mode

mrc p15,0,r0,c1,c0,0 @read control register

orr r0,r0,#0xc0000000

mcr p15,0,r0,c1,c0,0 @write control register

@set FCLK

ldr r0,=MPLLCON

ldr r1,=MPLL_405MHz

str r1,[r0]

mov pc,lr具体可参考ARM相关技术手册以及国嵌培训视频。

2597

2597

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?