时钟相关概念

时钟脉冲信号:按一定的电压幅度,一定的时间间隔连续发出的脉冲信号。时钟脉冲信号是时序逻辑的基础,它用于决定逻辑单元中的状态何时更新。数字芯片中众多的晶体管都工作在开关状态,它们的导通和关断动作无不是按照时钟信号的节奏进行的。

时钟脉冲频率:在单位时间内产生的脉冲个数。

时钟信号的产生有两种方式:①晶振②锁相环PLL

晶振:晶振全称晶体振荡器,是用石英晶体经精密切割磨削并镀上电极焊上引 线做成。这种晶体有一个很重要的特性,如果给他通电,他就会产生机械振荡,他们有一个很重要的特点,其振荡频率与他们的形状,材料,切割方向等密切相关。由于石英晶体化学性能非常稳定,热膨胀系 数非常小,其振荡频率也非常稳定,由于控制几何尺寸可以做到很精密,因此,其谐振频率也很准确。

晶体振荡器时钟的优点包括结构简单和噪声低以及可为客户提供精确的定制频率等方面;但一方面,它的缺点也比较明显, 例如其频率仅晶体决定,通常是特定晶体被制成客户所需的荡器,导致生产成本高、交货周期较长,不利客户加快产品上市时间,而且难以获得非标准频率。

锁相环PLL:PLL(锁相环)合成器是一种更为复杂的系统时钟源。通用PLL合成器需要一个外部晶体并包含一个能够对晶体的特定频率加倍或分频的集成锁相环( PLL)电路。使用锁相环,可以通过一些寄存器的配置来得到不同的频率。

两者对比:

典型的系统时钟振荡器源通常采用石英晶振,而更复杂的系统时钟振荡器源则是由PLL合成器提供。

1. 对于特定的时钟频率,采用PLL合成器可使用较便宜以及较低频率晶振来代替昂贵的高频晶振;

2. 对于需要多个时钟频率的系统,采用PLL合成器通过分频即可实现,而此时采用晶振模块则需要多个不同频率的晶振。

因此相对于晶体振荡器模块,通过PLL合成器提供精确时钟具有成本更低、占板面积更小等一系列优点。

时钟体系

了解一个芯片的时钟体系,主要是去了解以下几方面:

①所用的晶振频率

②有多少个PLL

③这些PLL产生了哪些时钟信号

④产生的时钟信号的用途

下面分别对芯片S3C2440,S3C6410,S5PV210的时钟体系进行探究。

S3C2440

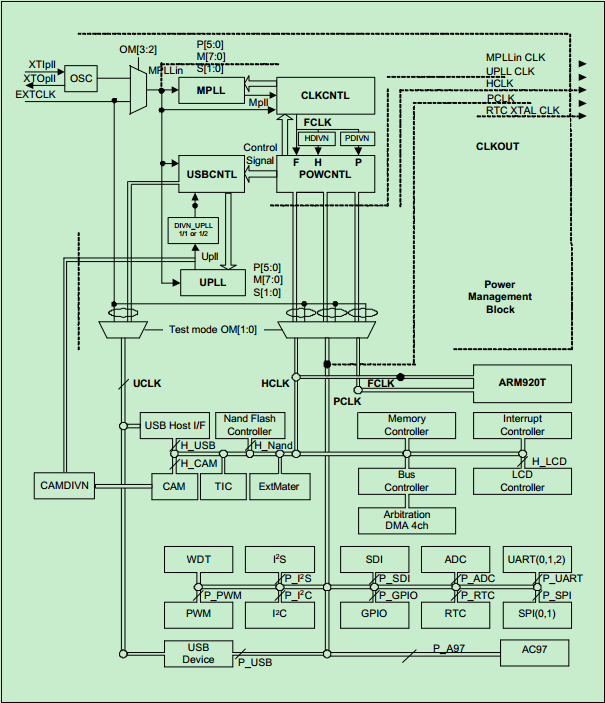

下图是从S3C2440的芯片手册查到的时钟信号发生器的体系结构

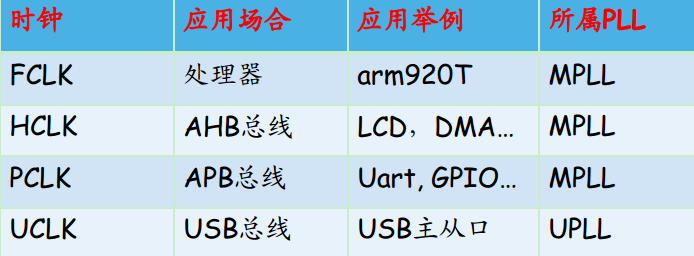

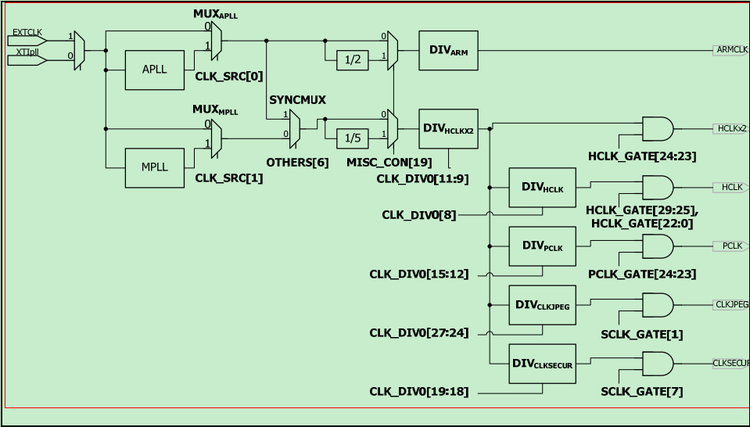

S3C2440可以使用外部晶振(XTIpll)(默认为12MHZ)和外部时钟(EXTCLK)两种方式输入时钟信号。它由跳线OM[3: 2]决定。S3C2440 默认的工作主频为12MHz(晶振频率),S3C2440有两个PLL:MPLL和UPLL。通过MPLL会产生三个部分的时钟频率:FCLK、HCLK、PLCK。UPLL则负责产生USB所需时钟UCLK。这四个时钟信号的应用如下所示:

S3C6410

S3C6410可以使用外部晶振(XXTIpll )(默认为12MHZ)和外部时钟(XEXTCLK )两种方式输入时钟信号。它由跳线OM[0]决定。S3C6410默认的工作主频为12MHz(晶振频率),S3C6410有三个PLL,分别为APLL、MPLL和EPLL。其中 APLL产生ACLK,给arm core使用。MPLL产生HCLK和PCLK。EPLL产生特殊的时钟,比如为USB提供48MHz时钟。时钟信号的应用如下:

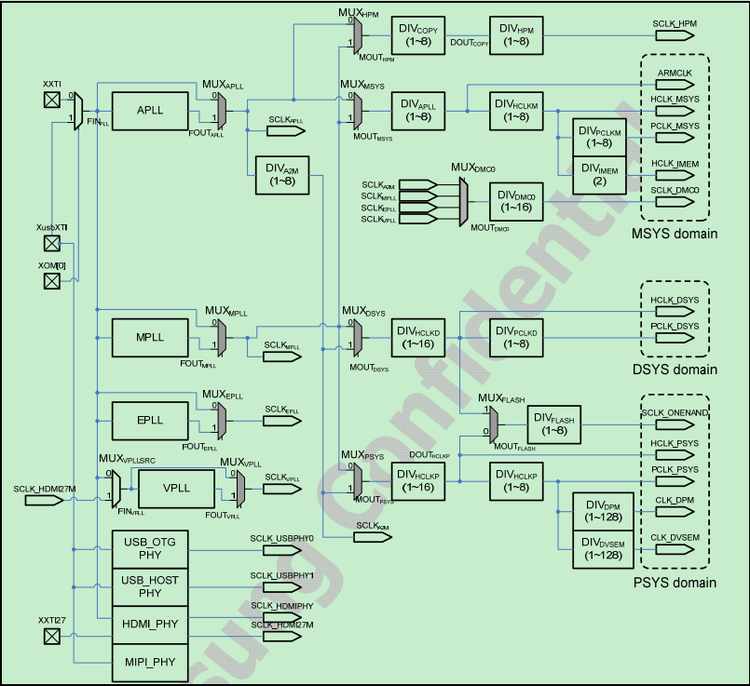

S5PV210

和S3c2440, S3c6410不同 , S5PV210首先推荐使用的是24MHZ的外部晶振。其次S5PV210的时钟被分为了3大体系,分别是:

①主系统时钟体系 (MSYS)

②显示相关的时钟(DSYS)

③外围设备的时钟 (PSYS)

S5PV210有4个PLL,分别为APLL、MPLL、EPLL和VPLL。

时钟初始化流程

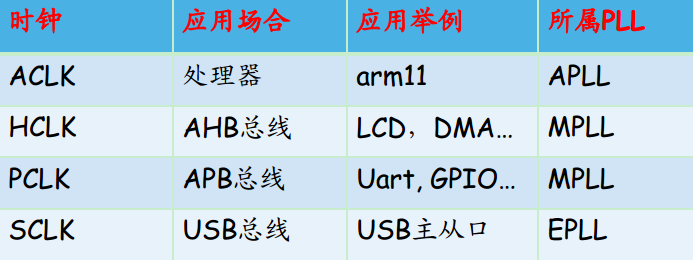

以S3C2440为例,下图是该芯片上电后时钟信号PCLK的变化过程。

1、上电几毫秒后,晶振输出稳定,FCLK=晶振频率,nRESET信号恢复高电平后,CPU开始执行指令。

2、我们的程序开头启动MPLL,设置MPLL的寄存器。

3、在设置MPLL的寄存器后,需要等待一段时间(LockTime),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。

4、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

由上,可以看出我们在初始化时钟时需要做的几点:

①设置Lock Time

②设置FCLK频率,也即设置PLL

但要想设置HCLK、PCLK的频率,还需要设置分频系数。比如设置分频比为:FCLK:HCLK:PCLK=1:2:4,则此时只要FCLK的频率确定,则HCLK、PCLK的频率也相应确定,其中HCLK频率为FCLK的一半,PCLK的频率为FCLK的四分之一。

通过阅读数据手册,还可以发现,如果HDIVN≠0(也即频率FCLK≠HCLK),则需要设置cpu总线模式为异步模式。使用指令(S3C2440)为:

mrc p15,0,r0,c1,c0,0

orr r0,r0,#R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

因此可以得到时钟初始化思维导图:

以芯片S3C2440为例:

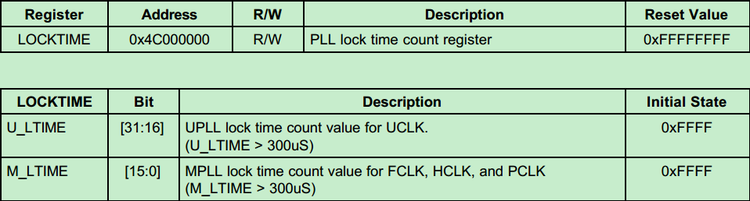

1、设置lock time

从芯片手册可以查到与lock time有关的寄存器为LOCK TIME COUNT REGISTER (LOCKTIME)

该寄存器控制UPLL和MPLL的lock time,默认值为0xFFFFFFFF,我们采用默认值,因此不需要去设置。

2、设置分频系数

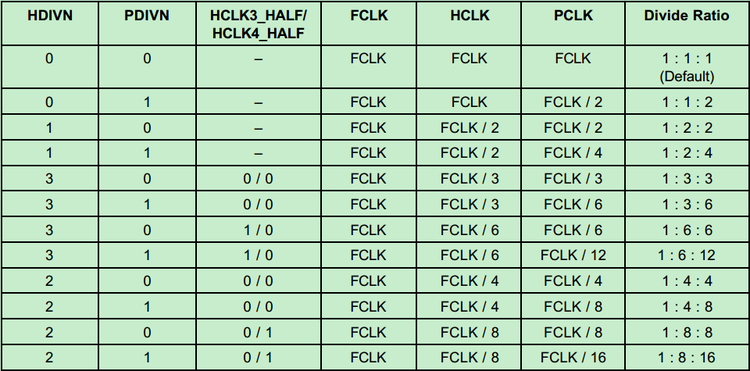

分频系数不是任意的,必须符合下图:

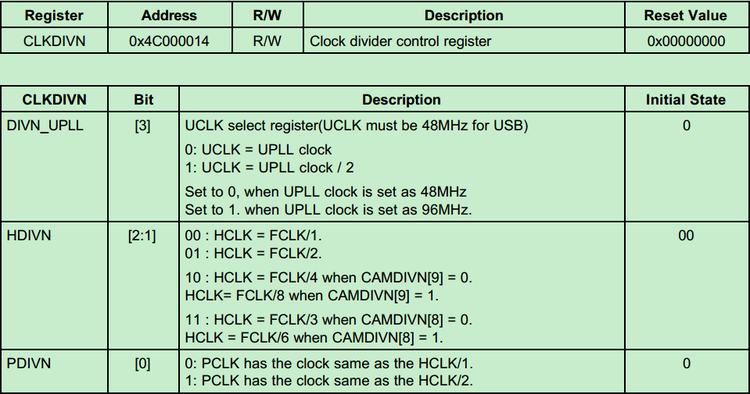

设置HDIVN和PDIVN的值可以达到设置分频系数的目的。模仿uboot中的分频系数,我们采用1:4:8的分频比,因此需要设置HDIVN=2,PDIVN=1。通过查阅芯片手册,可以知道与HDIVN和PDIVN设置有关的寄存器为CLOCK DIVIDER CONTROL (CLKDIVN) REGISTER

3、设置cpu总线模式为异步模式

从数据手册可以知道,设置的代码为:

mrc p15,0,r0,c1,c0,0

orr r0,r0,#R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

其中nF和iA是寄存器的最高两位,因此代码为:

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000

mcr p15,0,r0,c1,c0,0

4、设置FCLK

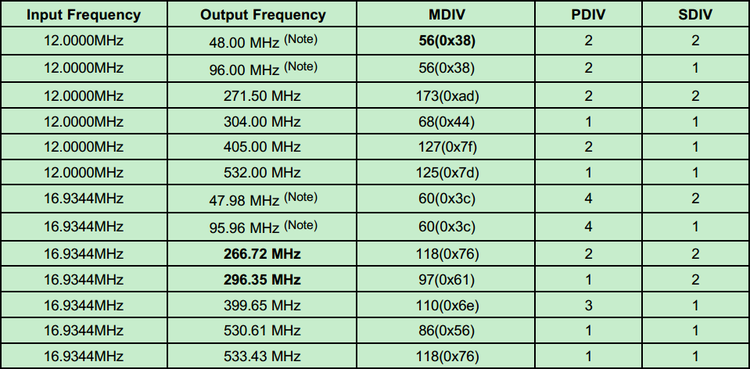

FCLK的频率设置可通过查表获得

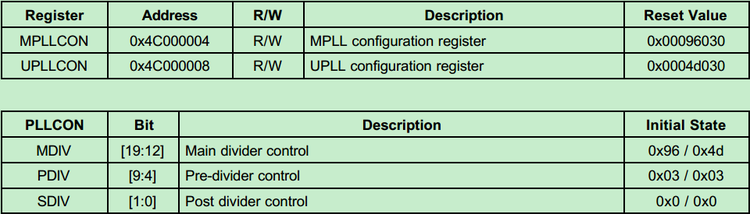

从表中可以得知,若设置FCLK频率为405MHZ,只需设置MDIV为127,PDIV为2,SDIV为1,而这三者的设置与PLL CONTROL REGISTER (MPLLCON & UPLLCON)有关

综合,汇编代码为:

#define CLKDIVN 0x4c000014

#define MPLLCON 0x4c000004

#define MPLL_405MHZ ((127<<12)|(2<<4)|(1<<0))

init_clock:

ldr r0, =CLKDIVN

mov r1, #0x5

str r1, [r0]

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000

mcr p15,0,r0,c1,c0,0

ldr r0, =MPLLCON

ldr r1, =MPLL_405MHZ

str r1, [r0]S3C6410:

S3C6410设置cpu总线模式不再是通过设置CP15来进行设置,而是通过Others control register来设置。并且,从上图可以看出,还需要设置CLK_SRC寄存器,MISC_CON寄存器来选择脉冲通道。

S5PV210:

与分频系数有关寄存器:Clock Divider Control Register

S5PV210不需要设置cpu总线模式为异步模式

与脉冲通道选择有关的寄存器:Clock Source Control Registers

1059

1059

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?