注明:在vhdl语言中,--代表注释,等价于//

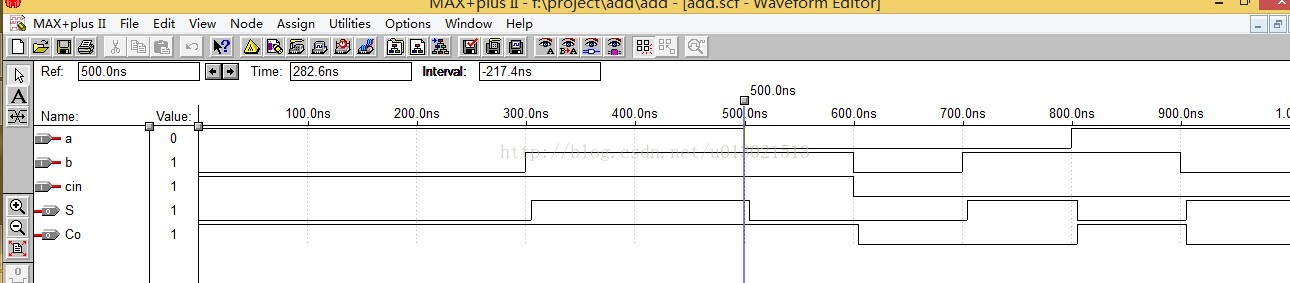

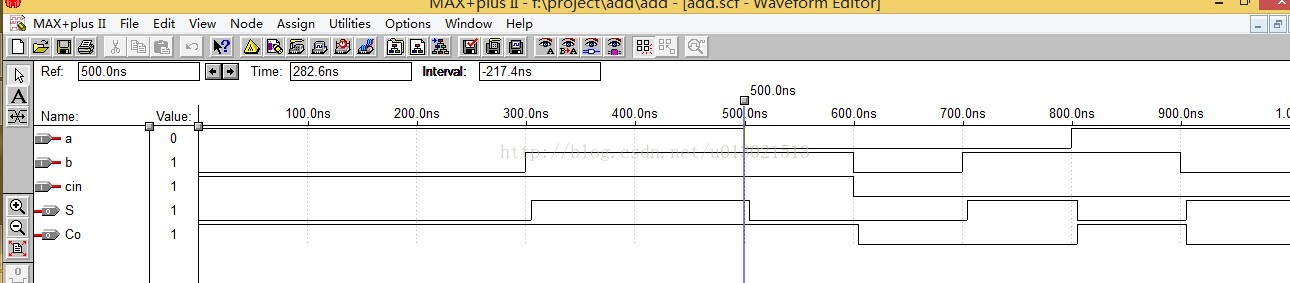

1. 一位全加器设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY add IS

PORT(a,b,cin:IN STD_LOGIC;

Co,S:OUT STD_LOGIC);

END ENTITY add;

ARCHITECTURE fc1 OF add is

BEGIN

S<= a xor b xor cin; --这两个为推得的表达式

Co<= (a and b) or (a and cin) or (b and cin);

END ARCHITECTURE fc1;

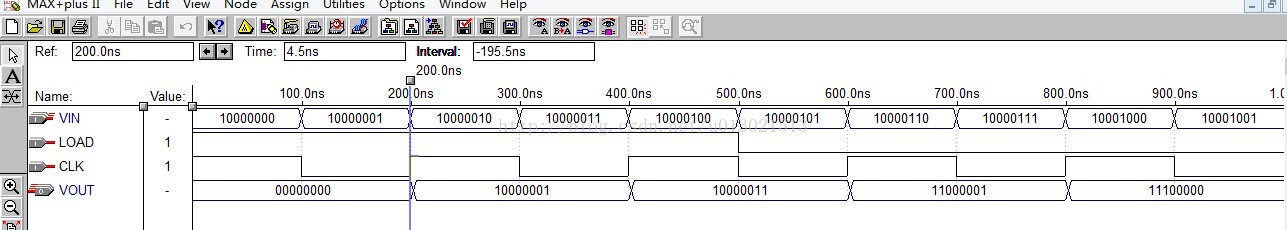

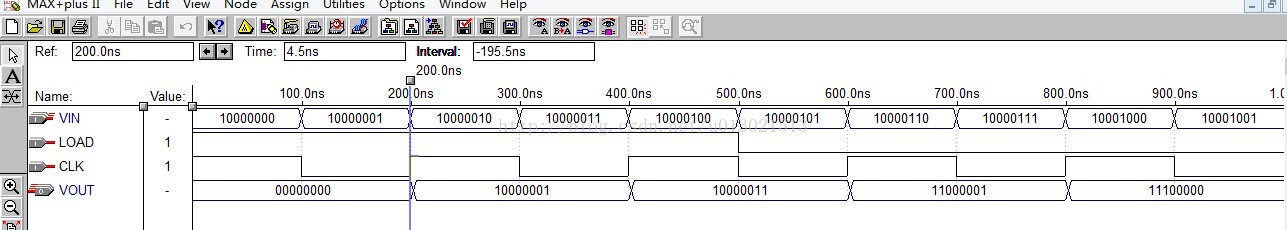

2.并行八位寄存器设计(移位寄存器)

--这是并行八位移位寄存器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY EIGHT IS

PORT(CLK,LOAD:IN STD_LOGIC;

VIN:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

VOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END EIGHT;

ARCHITECTURE happen of EIGHT IS

SIGNAL REG : STD_LOGIC_VECTOR(7 DOWNTO 0); --REG信号,百度了一下作用,信号一般是用于端口和端口之间的通信

BEGIN

PROCESS(CLK,LOAD) --CLK,LOAD变化的时候会执行

BEGIN

IF CLK'EVENT AND CLK = '1' THEN --上升沿的时候

IF LOAD = '1' THEN REG <=VIN; --如果load = 1,不变

ELSE REG(6 DOWNTO 0) <= REG(7 DOWNTO 1); --如果load = 0,高七位赋值给低七位,也就是都往右移动1个单位

END IF;

END IF;

END PROCESS;

VOUT<=REG;

END happen;

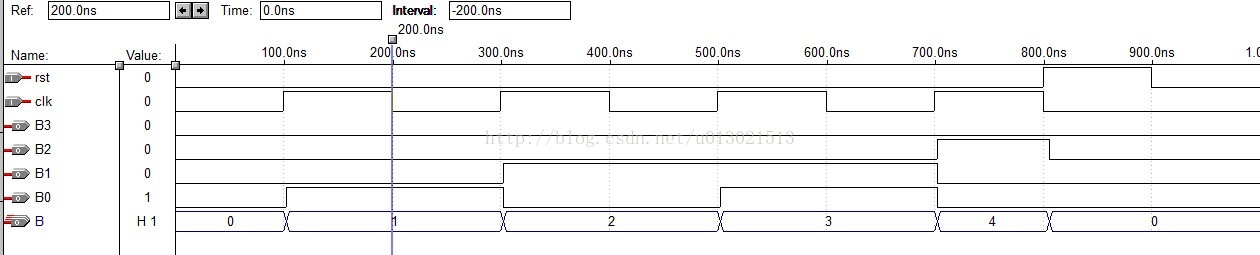

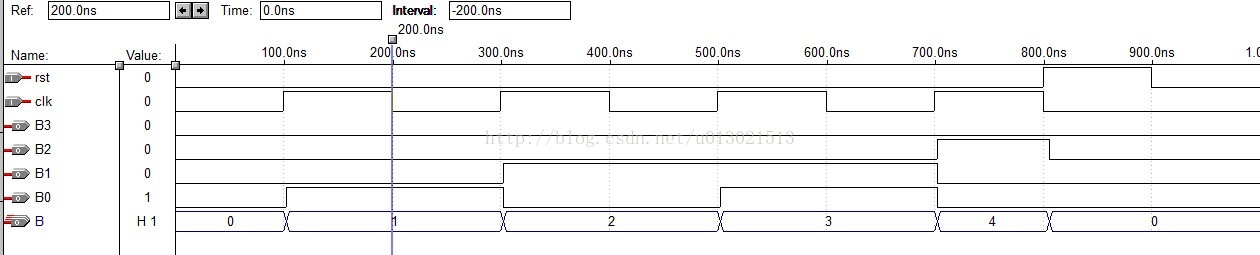

3.同步二进制计数器

LIBRARY IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_ARITH.all;--算术运算

use IEEE.STD_LOGIC_UNSIGNED.all;--无符号

ENTITY counter is

PORT(clk:in STD_LOGIC;

rst:in STD_LOGIC;

B:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)); --4位

end counter;

ARCHITECTURE Behavior of counter is

BEGIN

PROCESS(clk,rst) --只要有发生改变就一直执行,个人感觉类似C语言的while

BEGIN

if rst = '1' then B <= "0000"; --清零

else if(clk'event and clk = '1') then --上升沿执行加1

IF B ="1111" THEN B<="0000"; --防止溢出,置0

ELSE

B<=B+1;

end if;

end if;

end if;

end process;

end Behavior;

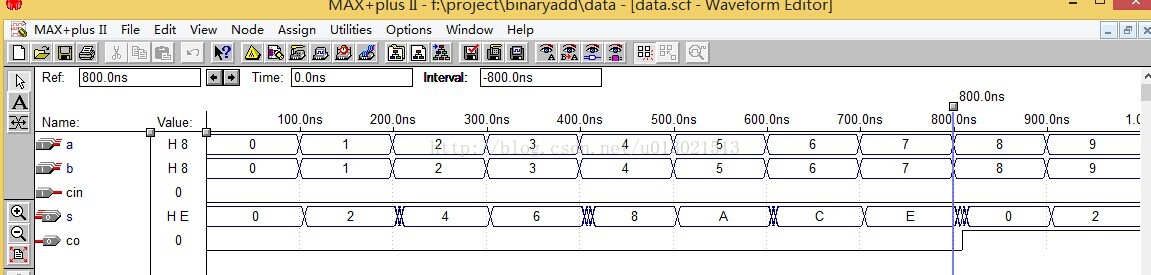

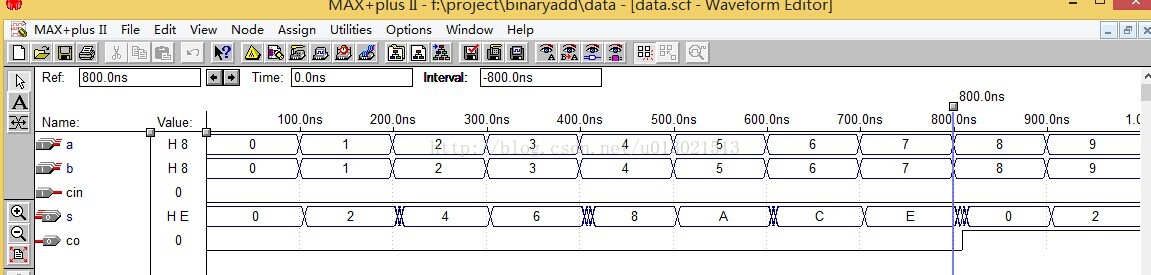

4.多位二进制加法器

library ieee;

use ieee.std_logic_1164.all;

LIBRARY ieee;

use ieee.std_logic_unsigned.all;

entity Data is

port(a:in std_logic_vector(3 downto 0);

b:in std_logic_vector(3 downto 0);

cin:in std_logic; --表示进位

s:out std_logic_vector(3 downto 0); --求和

co:out std_logic); --储存进位

end entity Data;

architecture ADD of Data is

signal c,d:std_logic_vector(4 downto 0);

signal e:std_logic_vector(4 downto 0);

begin

c<='0' & a; -- 0和a合并

d<='0' & b; -- 0和b合并

e<=c+d+cin; --全加器的功能

co<=e(4);

s<=e(3 downto 0);

end architecture ADD;

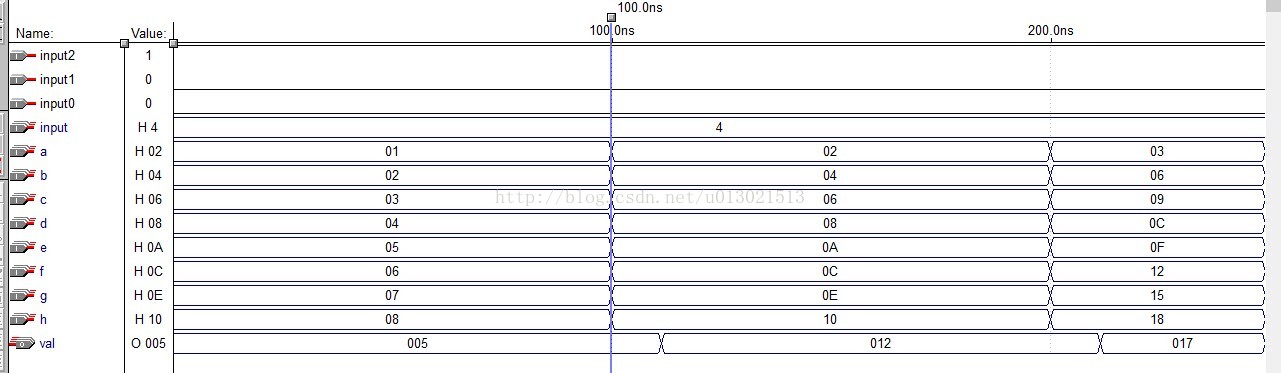

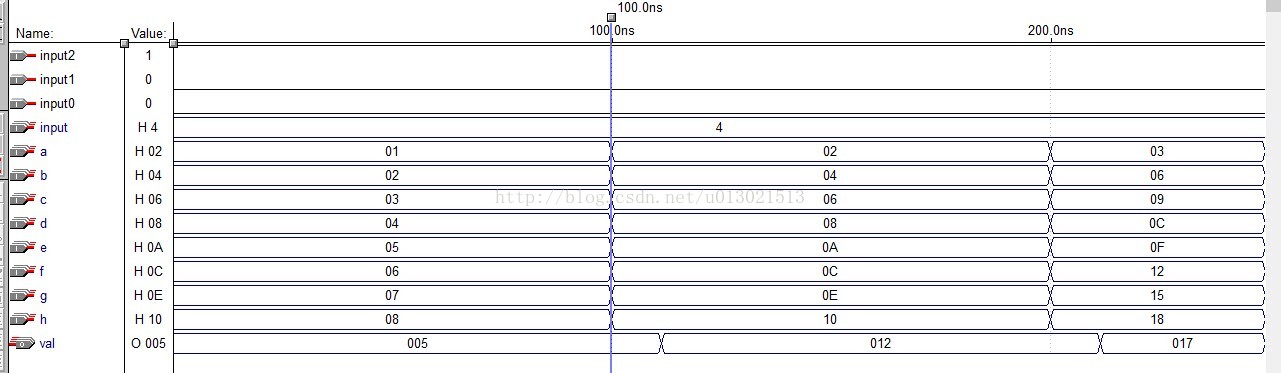

5.多路开关

library IEEE;

use IEEE.std_logic_1164.all;

entity choose is

port(a,b,c,d,e,f,g,h:in std_logic_vector(7 downto 0); --有8个数,所以开0-7

input:in std_logic_vector(2 downto 0); --最多三位,所以开0-2

val:out std_logic_vector(7 downto 0)); --同上上

end choose;

architecture choose1 of choose is

begin

process(input)

begin

case input is

when "000" => val <= a; --选择

when "001" => val <= b;

when "010" => val <= c;

when "011" => val <= d;

when "100" => val <= e;

when "101" => val <= f;

when "110" => val <= g;

when others => val <= h; --第一次写的时候"111"报错,百度了一下,估计是没写全的缘故

--所以还是用others简单暴力

end case;

end process;

end choose1;

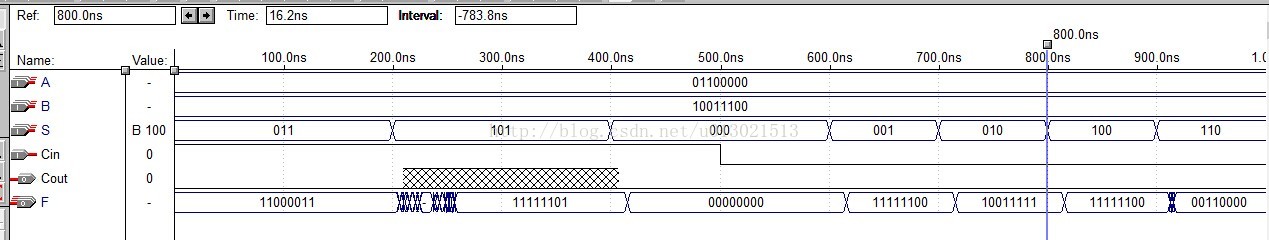

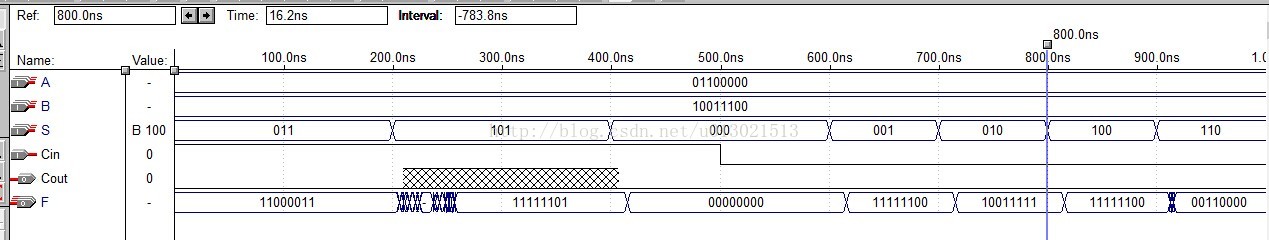

6.运算部件(ALU)的实现

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity ALU is

Port ( A : in std_logic_vector(7 downto 0);

B : in std_logic_vector(7 downto 0);

S : in std_logic_vector(2 downto 0); --选择

Cin : in std_logic; --进位

Cout : out std_logic;

F : out std_logic_vector(7 downto 0));

end ALU;

architecture Behavioral of ALU is

signal A0,B0,F0: STD_LOGIC_VECTOR(8 DOWNTO 0); --防止溢出

begin

process (A,B,S,Cin)

begin

--算术单元

Cout<='0';

if (S = "011") then

F <= A-B-Cin;

elsif (S = "101") then

A0 <= '0'&A(7 DOWNTO 0); --在八位前面补0

B0 <= '0'&B(7 DOWNTO 0);

F0 <= A0+B0+Cin; --相加,因为有cin进位所以可能会有溢出,故F0,A0,B0开九位

F <=F0(7 DOWNTO 0); --抛弃第九位只要后面的低八位,因为溢出没意义

Cout<=F0(8); --第九位

---逻辑单元

elsif (S = "000") then -- A && B

F <=A AND B;

elsif (S = "001") then --A || B

F <= A OR B;

elsif (S = "010") then --非A

F <= NOT A;

elsif (S = "100") then --A异或B

F <= A XOR B;

elsif (S = "110") then

F <= '0' &A(7 downto 1); --最高位为0,高七位各向后移动一个单位

elsif s = "111" then --最低位为Cin,第七位各向前移动一个单位

F <=A(6 downto 0) & Cin;

Cout<=A(7);

end if;

end process;

end Behavioral;

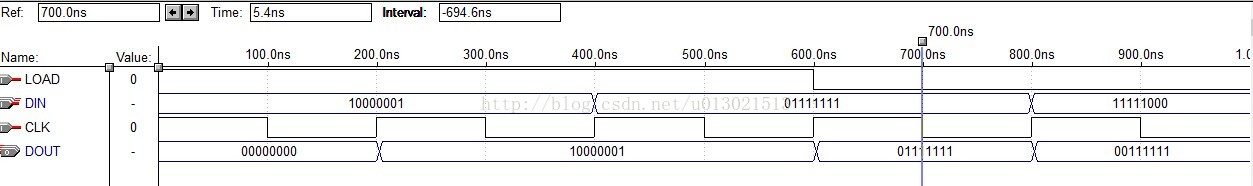

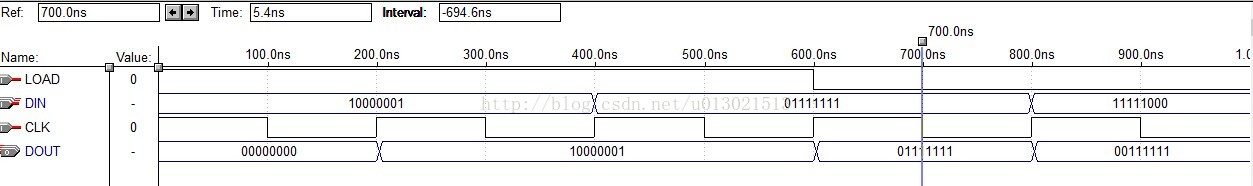

7.移位寄存器

--将一个八位二进制的数据每一位一次右移,若最高位为1,那么剩下的最后也会都为1,最高位0同理

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY move IS

PORT(CLK,LOAD:IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END move;

ARCHITECTURE behavior of move IS

SIGNAL REG:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(CLK,LOAD) --只要CLK,LOAD有变化就一直执行,个人理解应该等价于c的while

BEGIN

IF CLK'EVENT AND CLK = '1' THEN --上升沿有效

IF LOAD = '1' THEN REG<= DIN; --如果上升沿到来时,load为1,那么8位并行置入移位二进制中

ELSE REG(6 DOWNTO 0) <= REG(7 DOWNTO 1); --否则为高七位的值赋值给低七位

END IF;

END IF;

END PROCESS;

DOUT<=REG;

END behavior;

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?