Lattice ddr3教程全攻略之仿真篇

对于这部分,首先建议安装好diamond3.1,modelsim se 10.1a这两个软件,如果想仔细分析DDR3的IP部分,可仔细阅读DDR3 SDRAM Controller IP Core User’s Guide,下面用ug代指。官网上可以download,还有DDR3的基本知识,可以到网上download《高手进阶,终极内存技术指南——完整进阶版》,这个文章值得一读。

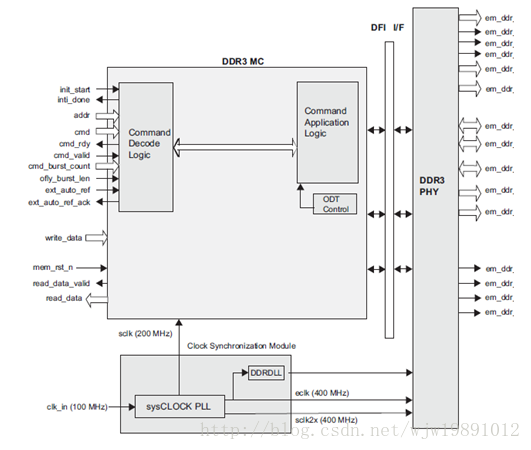

Lattice的ddr3控制器接口逻辑还是相对简单,比较好理解的,下面来看看DDR3 IP 的内部结构:

图:DDR3 IP逻辑框图

Initialization Module:根据JEDEC.的标准,在上电后对DDR3进行初始化配置,配置其相应的寄存器和工作方式等,具体配置的寄存器可以参看ddr3的协议文档,JEDEC规范写的很详细。当初始化配置完成后,该模块会给出一个done信号告诉用户。

sysCLOCK PLL:用于提供IP工作所需要的时钟,并提供给用户端一个时钟:k_clk。

Data Path Logic:用于从DDR3读取的数据转换到用户端,写入的数据不经过该模块,写入的数据从Command Application Logic (CAL)模块输入。

Command Decode Logic (CDL) :该模块用于译码命令,控制core按照设定的命令正确的访问ddr3芯片。

DDR3 PHY:用于转换单端的数据转换为差分给到ddr芯片端,和差分转单端输入。

以上部分有基础了解就行,不需要深究。

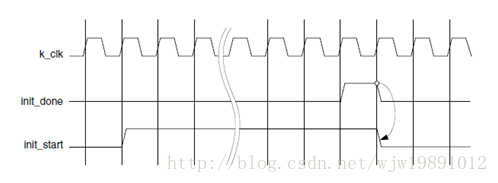

图:DDR初始化时序

当上电后,用户应该将init_start拉高至少200us,直到init_done被拉高一个周期,则将init_start拉低。用户检测到init_done被拉高后就表明芯片初始化完成了,也大概可以确定硬件是OK的。可以进行下一步操作。读和写控制非常简单,ug上说的很清楚,就不一一赘述了。

做DDR3设计之前当然是先仿真,这个毋庸置疑,那么仿真当然首选Modelsim,在仿真之前,先做好准备工作,那就是先编译好仿真所需要的库文件,编译库文件方法和Altera Xilinx类似,见《在Modelsim中建立LATTICE仿真库》一文,已共享。lattice的资料做的确实不如xilinx和altera。也是很多使用lattice fpga的工程师经常抱怨的一点,没有前人带的情况下使用lattice确实是非常恼火的。但是却也没有江湖传言的那么难用,其实很多时候并不是因为难,而是我们不愿意去了解,因为陌生而导致的恐惧,先入为主吧。那,废话不多说,开始进入主题。

现在假定你lattice库文件已经编译成功,那,我们当然要物尽其用,尽可能收集多的资源加快效率。。。此处省略一万字。首先说明,lattice的DDR3是带有Modelsim仿真例程的,只要在IP例化好了之后找到:***\ddr_p_eval\ddr3core\sim。然后在modelsim se中敲do ddr3core_eval.do就可以了,正常情况下是可以运行得到结果的,而且仿真初始化时间短,比altera快,这一点本人非常满意,而且激励写的很好懂,多以任务函数形式调度,这一点秒杀altera,altera还用的system verilog写的,比较坑。

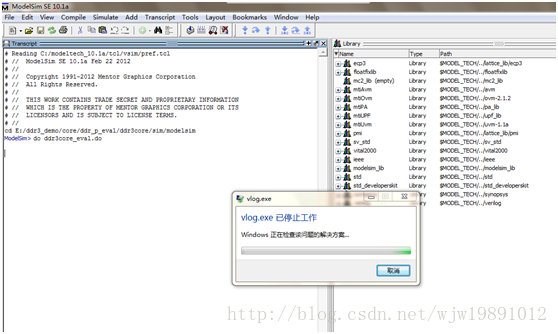

有时候直接用生成的例程一点问题没有,但就在刚刚,我又验证了一下出现了。。。

这就无语了,建议网友可以自己试一试。

当然还有另外个更好的例程,否则这个教程便没有意义,在官网上下载ddr3 demo,这个demo写的都是可综合的仿真代码,方便移植,其控制DDR3 IP的状态机效率高,但,不方便扩展,它带有modelsim仿真工程,这便是我们所需要的,其他的建议用户改成自己的逻辑。

第一步,当然是去官网download了,它也不会凭空掉到你的硬盘里不是么…

Download下来之后打开

这里添加了IP文件和用户逻辑,接下来修改个人所需用的device,然后打开IP配置文件,进行重新配置,其中ddr3_demo.lpf是工程生成的时序约束文件,今后我们的约束都添加到这个文件中,这个要谨记,时序约束部分会在时序篇中介绍。

下面做如下操作:

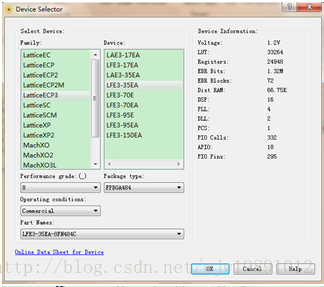

你把它更换为自己所需的器件,这里选的是ECP3-35,各位请随意,但是要确定你的芯片支持DDR3。在此之前你需要先安装好DDR3 IP配置软件,点击ip server进行在线download。然后点击IP,出现如下界面

安装好IP后进行如下操作

进行IP重配置

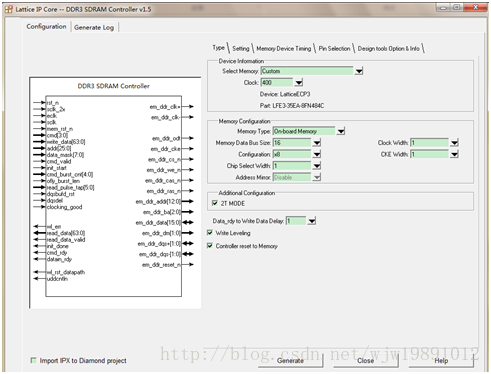

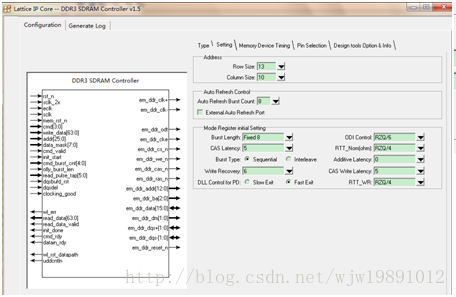

打开原IP文件进行regenrate,module output选verilog,开始进入配置页面

Selcet memory:选择memory型号,lattice所列出来的比较少,一般选custom,其他参数自己设置;

Clock:Memory所工作的时钟频率,有支持两种:400MHZ,即DDR3跑到800MHZ,;300MHZ,即DDR3跑600MHZ。这里注意要确定两点:1.所选器件是不是-8速度等级,因为只有-8的器件才能跑到400MHZ;2.memory最低能不能支持600MHZ,因为有些memory是800MHZ起跳,这个要结合ddr3的datasheet确定。另外,如果选择300MHZ,那么用户还需要在生成的IP文件中去修改ddr3_pll.v这个文件,修改其配置参数,如下:

大家可以在后面打开自动生成的ddr3_pll文件和我这个进行对比就能发现不同点,其实就是配置PLL的参数,这个也是lattice坑爹的地方之一,不人性化。。。

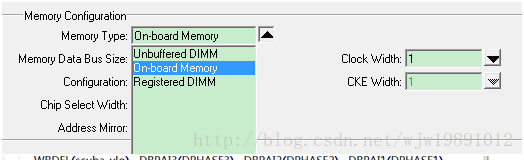

Memory configuration:其他参数都很好理解,提醒一点

这三个参数什么意思呢?

Unbuffered DIMM:无缓冲型模组,这是我们平时所用到的标准DIMM(dubule in-line memory module,双列内存模组,所谓双列是指模组电路板与主板插槽的接口有两列引脚,模组电路板两侧的金手指对应一侧引脚),分为有ECC和无ECC两种,简称unb-dimm。

On-board memory:其实就是颗粒了,这里例程中选的这个。

Registred dimm:寄存器型模组,这是高端服务器所使用的DIMM,分有ECC何无ECC两种,但是市场上几乎都是有ECC的,简称reg-dimm。

其他配置见《DoubleDataRateDDR3SDRAMControllerIPCoreUsersGuide.pdf》

第二页:Row size和colmn size和datasheet一致,其他保持默认即可

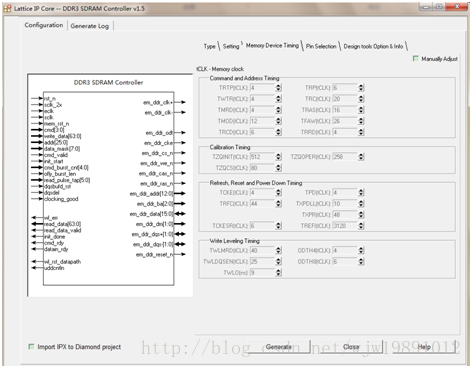

第三页:memory device timing,如果你是初学,建议默认,这个要结合自己所选择的chip参考datasheet填入相应的参数。

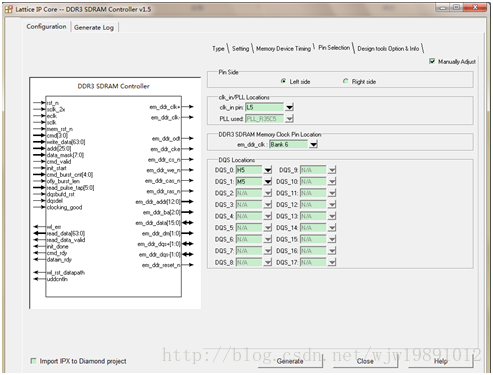

第四页:需要注意以下几点

LATTICE DDR3 IP支持放在芯片左边和右边两种情况,这个和它的器件特性有关,因为他的DQ的缘故,pin side选择好了之后,clk_in pin随之确定,这个即外部时钟输入管脚,一般都为100MHZ,差分输入,这个是不能随便连的,这里用的L5,到时这里都要添加到时序约束里面去。

PLL_used:是使用哪一个PLL,一般采用就近原则,PLL_R35C5是这个PLL所处的硬件模块名称,包含有位置信息,参考ecp3 handbook也要添加到时序约束中。

em_ddr_clk:FPGA输出给DDR3颗粒的时钟所处的BANK位置

DQS_0,DQS_1:J3,P5,这个是和选择的器件有关,可以结合器件资源修改,但是需要准从一定的DDR3管脚放置原则,DQS,DQ应该都放置在同一个BANK中,不应该跨BANK放置,否则fit不能过,SSN也不好。最终还是以时序约束通过为准。

第五页默认设置

因为DDR3颗粒跑400MHZ,16位宽,IP给出的用户端数据位宽为64位,所以用户时钟应该是200MHZ。

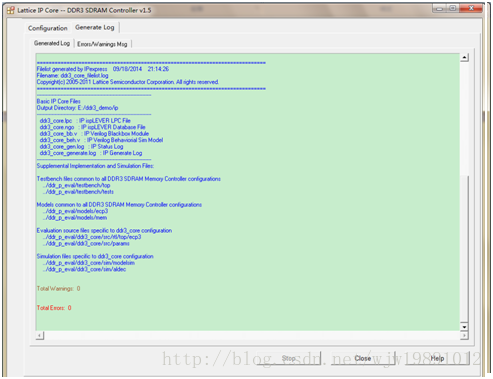

最后点击generate…

喝杯茶…等待一会儿….

直到看到…

说明IP例化成功,然后close 掉。

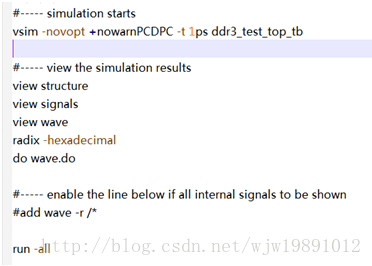

现在开始仿真,仿真这里极力推荐用脚本文件形式写,虽然第一次较为麻烦,而且大多可以在已有的基础上修改脚本,掌握后其实很简单,绝对是属于一劳永逸的事情,下面看好了:

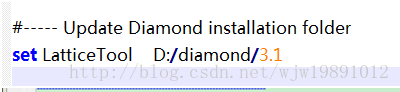

打开do ddr3_ecp3_demo.do,更改为自己的diamond地址

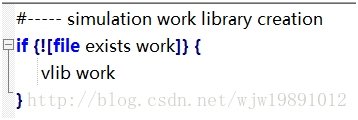

建立work工作区

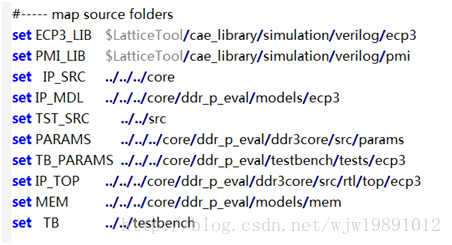

映射所需加载的文件夹,这里包含了Lattice库文件(ecp3,pmi),仿真所需的源文件,仿真激励,IP文件,memory模型。这里tcl命令书写方式需要好好体会。以后用户自己的源文件放在src文件夹就OK。

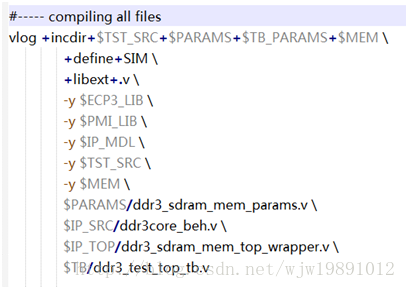

编译所有文件

运行

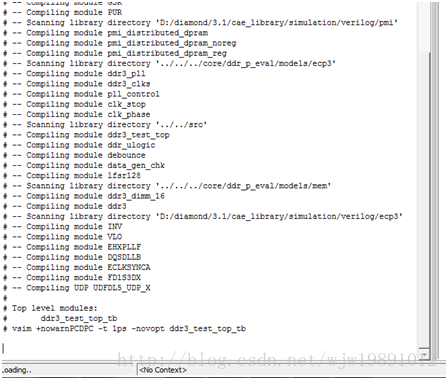

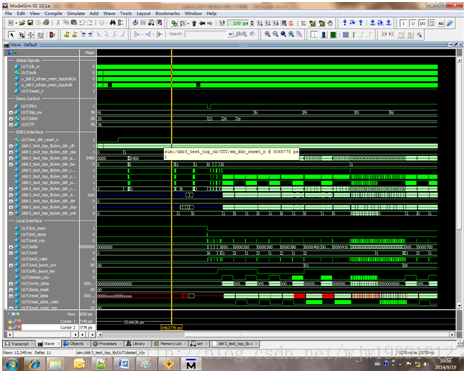

修改好了.do文件后,然后打开modelsim 10.1a,敲:cd E:/ddr3_demo/user_logic/sim/modelsim 进行更换工程位置。然后敲do ddr3_ecp3_demo.do,然后你可以看到编译,加载过程…

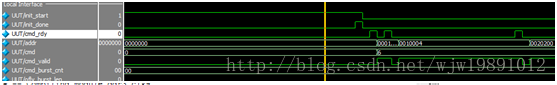

然后波形打开,然后出现漂亮的波形,大功告成…

Init_done拉高了。。。。

看到了波形后,很容易很出其实就是一个不断读写校验的过程,在这基础之上修改自己的代码。

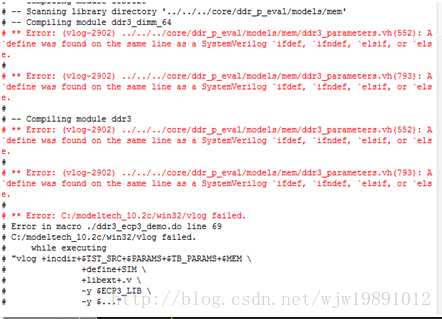

我这里用的modelsim se 10.1a版本,另外用了modelsim se 10.2c仿真,却出现了下面的错误

貌似是对system verilog的支持问题,这究竟是什么原因本人也没搞明白,期待网友提点。

testbench文件中的ddr3_test_top_tb文件为激励文件,它提供了仿真所需要的时钟和复位等。其中仿真文件中下面两句话必不可少,这个是用lattice器件所特有的:

GSR GSR_INST(.GSR(VCCI_sig));PUR PUR_INST(.PUR(VCCI_sig));

其中VCCI_sig为1。也可以这样写:

GSR GSR_INST(.GSR(rest_n));PUR PUR_INST(.PUR(rest_n));

rest_n 为复位信号,低电平复位,激励文件其他部分没有需要特别注意的。

如果想要更改代码,可以在源代码中更改后这样操作modelsim,在transcript界面敲入quit –sim命令,退出当前仿真工程,然后重新敲:do ddr3_ecp3_demo.do

这样就可以看到更改之后的波形。

关于DDR仿真的题外篇:

在需要用到ddr时,首先需要考虑的就是带宽的计算,这个直接决定你选用

的型号,比你1920*1080@30HZ的带宽为:1920*1080*30*16=0.9269GBIT(这里数据位宽为16的yuv)如果一个简单的进行ddr帧缓存,需要用到一读一写操作,那么对ddr的带宽要求最少就是2*0.9269BGIT,接下来考虑到ddr的效率问题,lattice的ddr ip控制器官方说效率到90%没有问题,一般建议以80%为限,也就是ddr带宽最低最好大于:(2*0.9269)/0.8=2.31725GBIT。对于一般DDR2/DDR3来说,在视频应用中容量需求肯定绰绰有余,主要考虑的是带宽,跑400MHZ的DDR2,数据位宽16位,1GBIT容量,带宽为:200*16*2/1024=6.25GBIT,效率:2.31725/6.25=37.076%;跑800MHZ的DDR3,数据位宽16位,1GBIT容量,带宽为:400*16*2/1024=12.5GBIT,2.31725/12.5=18.538%。现在DDR2使用的越来越少,价格也自然上涨,所以一般产品中会考虑到这个问题,能用DDR3最好,lattice的ecp3器件是都支持ddr2 ,ddr3的,但是在Altera的cyclone 系列中只有cyclone v以上才支持ddr3,xilinx只有sprtan 6以上才支持ddr3,所以这是个综合考虑的问题。

控制器的控制策略直接影响到DDR3的吞吐量即带宽。根据DDR3的自身特点,通常用的方法有同bank同行操作策略:只有当换行时才进行必要的precharge操作,这样可以节省大量的开销,提高有效带宽。多bank乒乓操作策略:可以先后激活不同bank的行。由于同bank同时只能有一行进行操作,读到读,读到写,写到写,写到读,操作前后都要进行激活、去激活操作,每一次操作都要浪费大量的带宽。而DDR3允许读写同时去激活、去激活其他bank的任意行,即激活多bank策略,这样就可以在结束某一个bank的读写操作后比较短的时间内进行其他bank的读写操作。这样大大提高了DDR3的吞吐量。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?