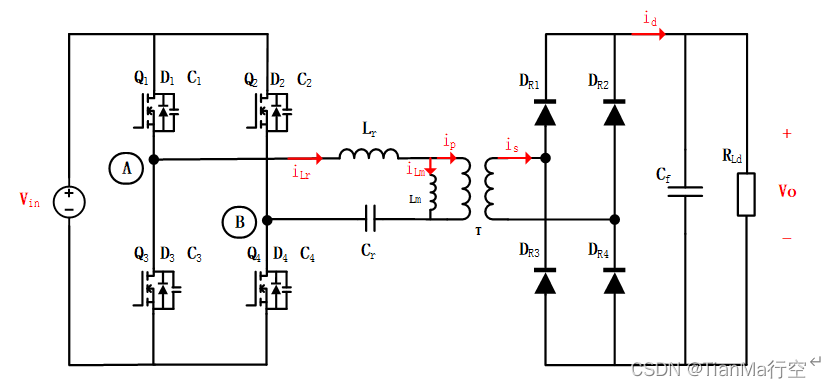

这是FB_LLC。HB_LLC只是少了两个Ceq,但是N* Vo=0.5* Vin。两者最后推出的公式是一样的,下面就以FB_LLC说明。

首先必须要满足感性条件,其次再计算死区时间是否满足ZVS。

LLC需要足够的死区时间,在死区时间内,谐振电感Lr中存储的能量必须大于存储在MOS的Ceq中的能量,只有这样才能将Ceq中的能量释放完毕,完成ZVS。Ceq与Vds有很大关系。

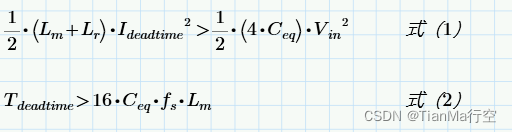

实现ZVS,可以推出两个必要条件,如下所示:

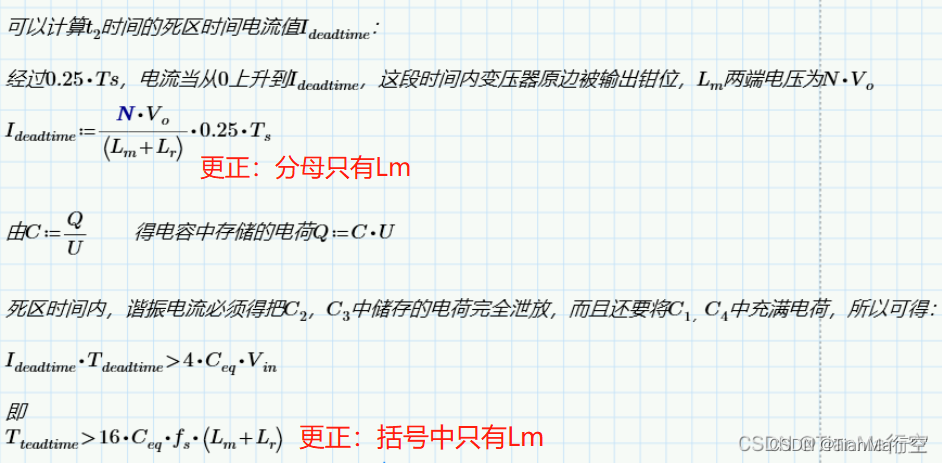

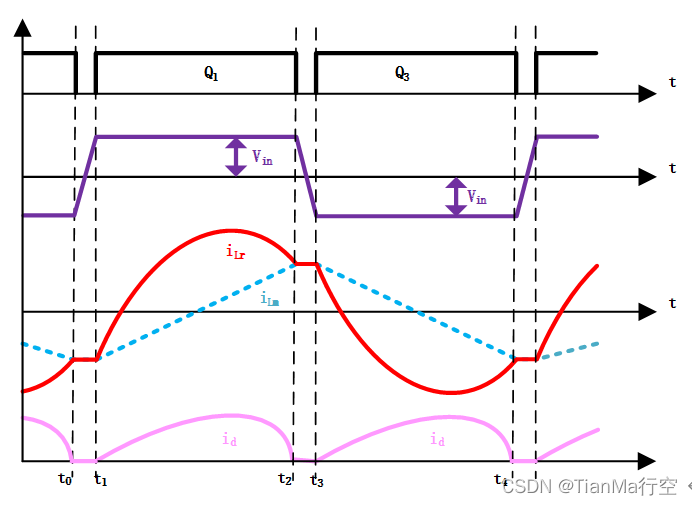

根据文章后面的拓扑和波形分析。以前半个周期为例,推导式(1)和式(2)。

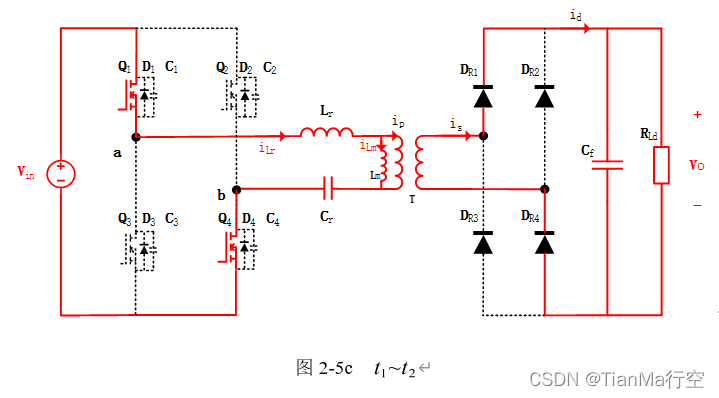

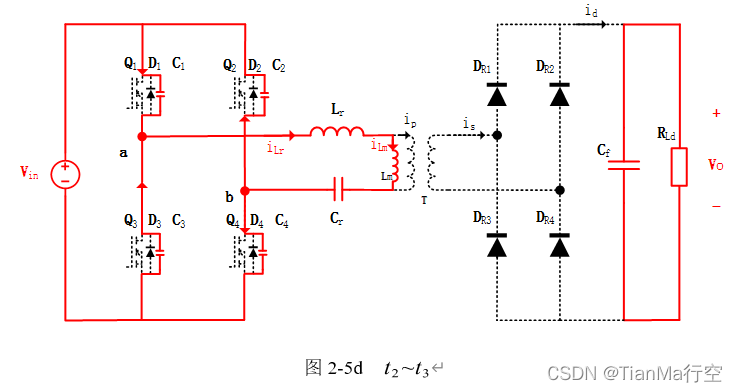

式(1)很好推导,在图2-5d中,死区时间的电流 为C2、C3放电,同时为C1、C4充电,所以可以得到式(1)。

为C2、C3放电,同时为C1、C4充电,所以可以得到式(1)。

式(2)中,由于Lm远远大于Lr,所以在死区时间内,可以认为谐振电流几乎保持不变,是个定值。

Figure1是拓扑,Figure2是工作波形图,图2-5c是t1-t2时间段的工作电路,图2-5d是t2-t3时间段的工作电路。

Figure1:FB_LLC拓扑

Figure2:LLC工作波形图

文献:

上升时间和下降时间及上升和下降延迟的定义:

1032

1032

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?