首先,需要说明电路中常用的两个概念–组合逻辑电路和时序逻辑电路;

组合逻辑电路的输出仅与输入有关,当输入发生变化时,输出几乎立刻发生变化;

时序逻辑电路的输出不仅与当前输入有关,还与电路过去的状态有关,具有一定的记忆能力,通常由一个时钟驱动;

加法器是一个简单的运算部件;

加法器的结构由简单到复杂分别为:半加器→全加器→8位加法器→32位加法器;

现在,通过LabView按从简单到复杂来构造一个32位的加法器;

本篇主要构造半加器与全加器;

半加器

半加器的真值表如下图所示,其中iA、iB为输入;oS为和,oCarry为进位输出;

| iA | iB | oS | oCarry |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

逻辑表达式为:

oS=iA⊕iB;其中⊕为异或运算符;

oCarry=iA·iB;

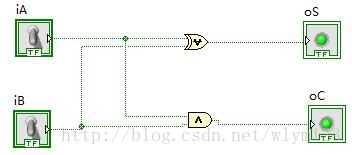

Labview的程序框图为:

注:上图两个运算符为:

前面板的运算结果有:

表示iA为0,iB为1,则oS为1,oC为0;

将该半加器做成一个子函数,记为HalfAdd,输入为iA、iB,输出为oS、oC;

全加器

全加器与半加器的主要区别是全加器多了一个输入iCarry,代表低位进位;

全加器的真值表如下图所示,其中iA、iB为输入,iCarry为进位;oS为和,oCarry为本级进位;

| iA | iB | iCarry | oS | oCarry |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

用逻辑表达式表示为:

oS=(iA⊕iB)⊕iCarry;该表达式称为和表达式;

oCarry=iA·iB+(iA⊕iB)·iCarry;

其中可将iA·iB记为G,称为本地进位函数,将iA⊕iB记为P,称为进位传递函数;

iA⊕iB为半加器的oS,iA·iB为半加器的oCarry;

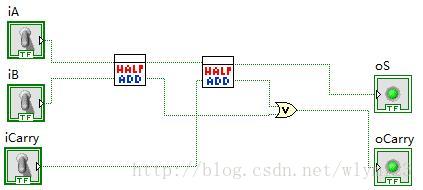

Labview的程序框图为:

图中的两个自定义函数即为半加器函数;

其前面板的结果有:

表示当iA、iCarry为1,iB为0时,oS=0、oCarry=1;

也可将该全加器做成一个子函数,即为FullAdd,输入为iA、iB和iCarry,输出为oS、oCarry;

现在,通过Labview的逻辑运算符完成了半加器与全加器的构建,后续的8位加法器,16位加法器等都是以全加器为基础构建而成;

另外说明,Labview是一种G语言,是一种积木式的很好玩的语言,适合直观的构建计算机系统部件,与HDL中的网表类似,但比那个好玩,故选择用Labview来进行计算机组成实验;

后续的内容有组成一个最简单的计算机,在其上覆盖一个多道操作系统;并完成一个类C编译器;如果能坚持完成上述几个“小目标”,完成部分TCP/IP协议栈;

由于能力有限,该系列文章是主要是用于对自己学习的总结以及以后的复习,其中有许多的观点可能有错,望大牛指正,不胜感激!!!

也希望有共同爱好的同学一起学习;

7685

7685

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?