出自《基于Cadence的信号完整性仿真步骤.pdf》

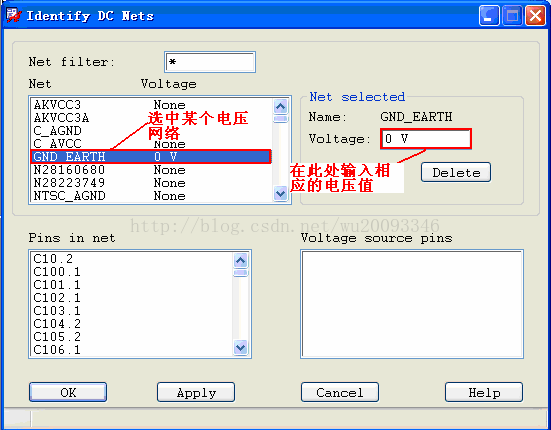

(2)单击“Identify DC Nets”,弹出“Identify DC Nets”窗口,如图2-6 所示:

图 2-6 Identify DC Nets 窗口

(3)在“Net”列表中选择网络如“GND_EARTH”,在“Voltage”栏双击“NONE”输入相应的电压值如0,并按下“Tab”键。如选“VCC285”,在“Voltage”栏双击“NONE”输入相应的电压值如2.85,并按下“Tab”键。

(4)单击“OK”,关闭“Identify DC Nets”窗口。“Database Setup Advisor” 窗口将再次显示。注意:如果有的网络与提取的网络无关,则可以不分配电压属性。

2.5 器件设置(Device Setup)

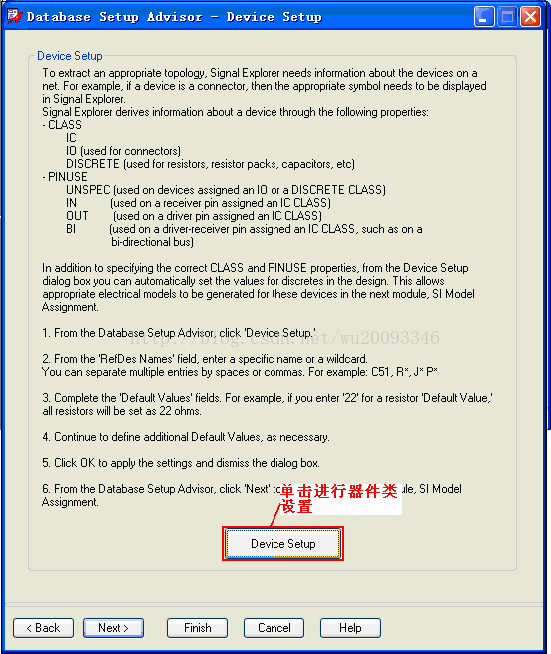

(1)单击“Next”,弹出“Data Setup Advisor –Device Setup”窗口,如图2-7 所示:

图 2-7 Data Setup Advisor –Device Setup 窗口

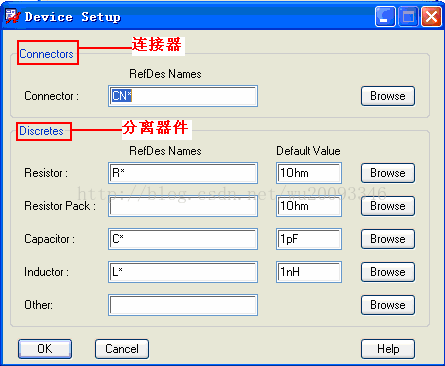

(2)单击“Device Setup”,弹出“Device Setup”窗口,如图2-8 所示:确定哪一个元件是连接器(Connectors),哪一个元件是分立元件(Discretes),并相应地确定器件的“Class”和“Pinuse”。器件类(Device Class)IC 是能分配IBIS 模型的有源器件每个管脚的PINUSE 必须是IN、OUT、BI、NC、GROUND、POWER、OCA、OCL、DISCRETE 是无源器件(电阻、电容、电导)每个管脚的PINUSE 必须是UNSPECIO=INPUT/OUTPUT每个管脚的PINUSE 必须是UNSPEC PINUSE PCB SI 使用PINUSE 来确定Sigxplorer/Signoise 仿真的缓冲器类型Input、Output、Bidirectional、UNSPEC、Power、Ground 对于 IO 和DISCRETE 器件的PINUSE 必须是UNSPEC都是无源器件

图 2-8 器件类设置窗口

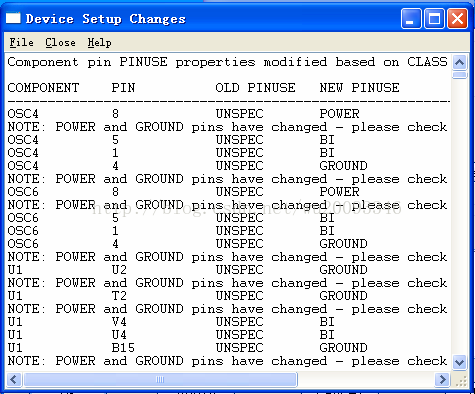

图 2-9 元件变化的状态报告

2.6 SI 模型分配

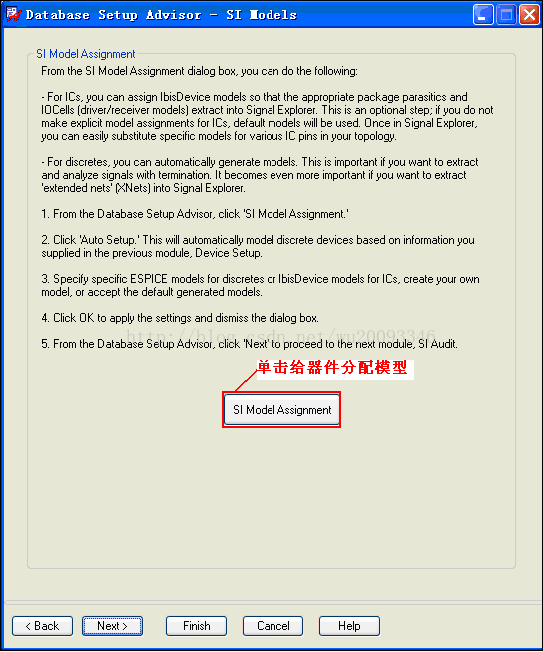

(1)单击“Next”,弹出“Data Setup Advisor –SI Models”窗口,如图2-10 所示:

图 2-10 Data Setup Advisor –SI Models 窗口

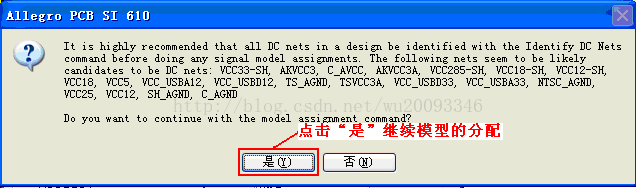

(2)单击“Signal Model Assignment”→弹出提示信息(有的DC 网络没有分配电压值),如图2-11 所示:

图 2-11

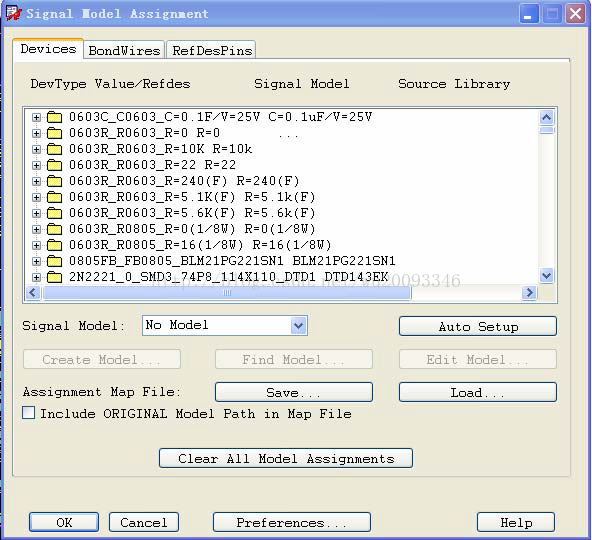

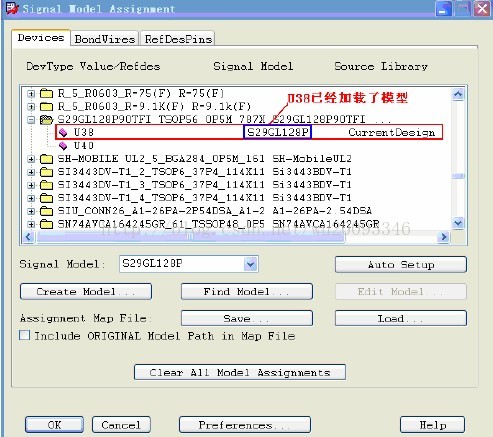

(3)单击“是”,弹出“Signal Model Assignment”窗口,如图2-12 所示:Device 可以手动或自动为器件分配模型。Bond Wires 定位并为Bondwire 连接分配Trace 模型。RefDesPins 为指定管脚分配IOCell 模型。

图 2-12 Signal Model Assignment 窗口

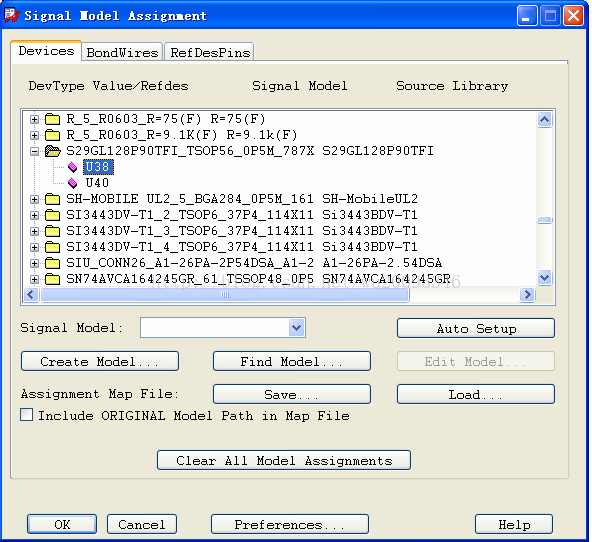

(4)手动分配元件模型这里只对地址线A15 进行仿真,该网络连接了五个器件分别是U8、U32、U38、U40、U45。下面以U38 为例,为其分配IBIS 模型。在“Device”列表中找到U38,如图2-13 所示:

图 2-13 Signal Model Assignment 窗口

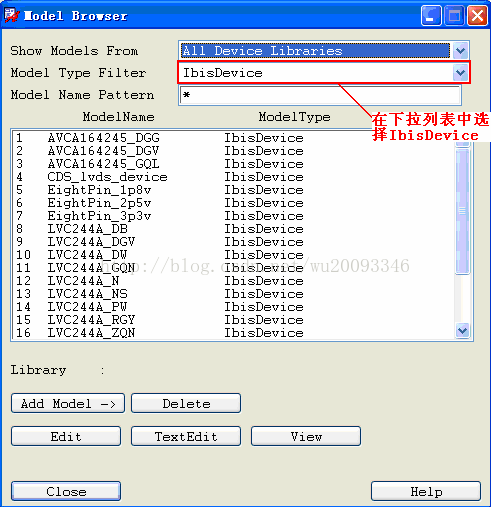

然后单击“Find Model”,出现“Model Browser”窗口,如图2-14 所示:

图 2-14 Model Browser 窗口

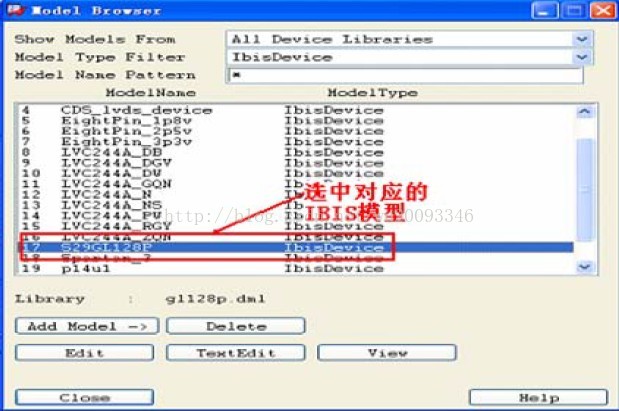

在Model Type Filter 栏中选择IbisDevice,在Model Name Pattern 栏中输入*,如果知道对应的IBIS 模型直接输入模型名称即可找到模型。然后在模型列表中找到对应的IBIS 模型(U38 对应的IBIS 模型为S29GL128P)单击,如图2-15 所示:

图 2-15 在“Model Browser”窗口选中对应的模型

然后点击“Close”,回到“Signal Model Assignment”窗口,如图2-16 所示:

图 2-16 Signal Model Assignment 窗口

由图知,U38 已经分配了IBIS 模型,同理给其余的器件分配对应的IBIS 模型。

(5)模型分配完成后,单击“OK”,保存修改返回“Database Setup Advisor-SI Models”窗口。

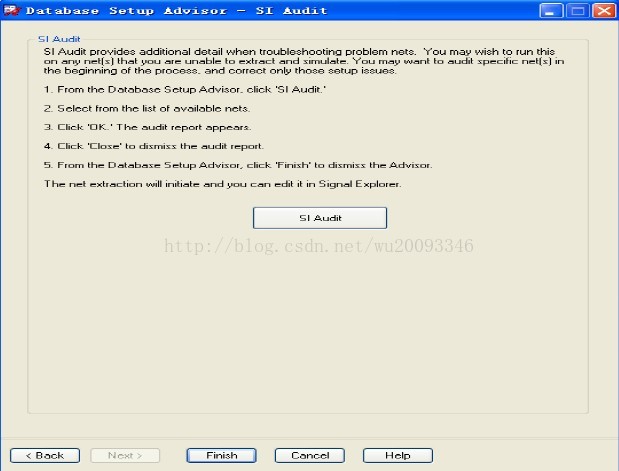

2.7 SI 检查(SI Audit)

点击“Next”进入“Database Setup Advisor-SI Audit”窗口,如图2-17 所示:

图 2-17 Database Setup Advisor-SI Audit 窗口

未完。

458

458

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?