1、Altium Designer 10 入门知识

1.1.1 什么是 Altium Designer

Altium Designer 提供了统一的应用方案,是 Protel(经典版本为 Protel 99se)的升级版本,其综合电子产品一体化开发所需的所有必须技术和功能。Altium Designer 在单一设计环境中集成板级和 FPGA 系统设计、基于 FPGA 和分立处理器的嵌入式软件开发以及 PCB版图设计、编辑和制造。并集成了现代设计数据管理功能 , 使得 Altium Designer 成为电子产品开发的完整解决方案-一个既满足当前,也满足未来开发需求的解决方案。

1.1.2.Altium Designer 10 的特点

与过去以季节性主题(如 Winter09,Summer09)来命名的方案不同,而是采用新型的平实的编号形式来为新的发布版本进行命名。最新发布的 Altium Designer - Release 10 将继续保持不断插入新的功能和技术的过程,使得您可以更方便轻松地创建您的下一代电子产品设计。 Altium的统一的设计架构以将硬件,软件和可编程硬件等等集成到一个单一的应 用程序中而闻名。它可让您在一个项目内,甚或是整个团队里自由地探索和开发新的设计创意和设计思想,团队中的每个人都拥有对于整个设计过程的统一的设计视图。

显著亮点如下:

提供了将设计数据管理置于设计流程核心地位的全新桌面平台。

提供了新的维度,以供器件数据的搜寻和管理,确保输出到制造厂的设计数据具有准确性和可重复性。

为设计环境提供供应链信息的智能链接,确保对元器件的使用有更好的选择 。

提供了涵盖整个设计与生产生命周期的器件数据管理方案,而结构性的输出流程更是确保了输出信息的完整性。

R10 系列的增强功能包括:输出 Output Job 编辑器、内电层分割加速改善、弹出式的多 边形铺铜管理器、Atmel QTouch 支持、自定制的笛卡尔直角和极坐标栅格、Aldec HDL 仿 真功能、实现比使用指针更多的 GUI 增强,以及随着 Altium Designer10 临近发布日前,我 们将构建其中的更多酷炫功能。而且,其平台稳定性也得到了增强。

1.3 整体流程

1.3.1、方案分析

对于所面临的具体项目,工程师首先做的是不同方案整体原理设计,然后是方案比较与 确定,元件选择。

1.3.2、电路仿真

对方案中确定的整体电路或局部电路要做电路仿真,以此做电路参数估算 ,并借鉴仿真 结果修改设计方案中的缺陷。

1.3.3 设计原理图

原理图设计部分同时需要做的原理图库的设计,虽然 Altium Designer 10 软件自带一部 分库,但不是包含市面上所有的元件,尤其是最新推出元件。在原理图绘制过程中,有整体 原理图的复杂程度决定采用何种结构的设计方式。通常所说的层次原理图设计,就为工程师 做复杂电路板提供了便捷。原理图设计后期,用 ERC(Electrical Rules Check) 工作查错,找出错误原因并修改原理图。

1.3.4 设计组建的封装

对器件的封装设计,主要是查看器件手册。也可以直接用测量工具测量器件的实际工具, 然后再做封装。

1.3.5 PCB 板设计

工程师在确定 PCB 机械尺寸后,就将通过 ERC 测试的原路图导入 PCB 板中,根据项目的 实际要求设置 PCB 的规则,板的层数等。布局在 PCB 设计中占大部分时间,一个优秀的硬件 工程师对布局的要求是很苛刻,尤其是电磁兼容性问题。布局完成后接下来布线、泪滴、铺 铜,DRC(Designer Rule Check )测试。

1.3.6 校对审核

工程师完成 PCB 设计后,需要对自己设计的电路进行校对,确定方案中设计的硬件电路 在设计中没有因特殊原因被误修改。对于复杂的电路板,多人分工合作,最终由 PCB 工程师 布线完成,更需要多人对各自设计的电路图与 PCB 部分进行校对,最终由项目工程师做整体 审核。

1.3.7 文档整理

这部分主要分三部分人的工作:导出制板所需的 GERBER 文档,料单 (BOM) 生产,导出 原理图文件,打印输出。

2、Altium Designer 10 建立项目

Altium Designer 10 的所有电路设计工作都必须在 Design Explorer(设计管理器) 中进行,同时设计管理器也是 Altium Designer 10 启动后的主工作接口。设计管理器具 有友好的人机接口,而且设计功能强大,使用方便,易于上手。因此本章将对设计管理器中 关于电路板设计的使用进行的介绍。

2.1 打开 Altium Designer 10 软件

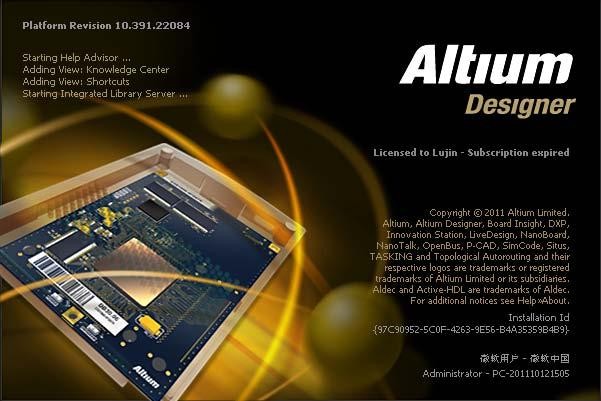

在桌面双击 Altium Designer 10 快捷键,启动画面如图 2-1。

图 2-1 Altium Designer 10 启动画面

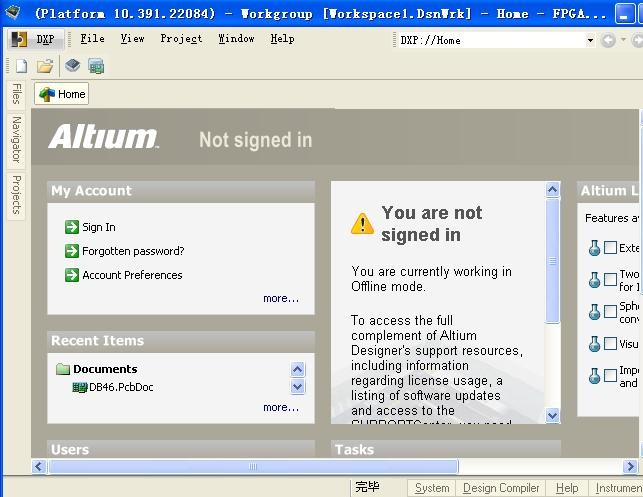

2.2 主菜单和主工具栏

主菜单和主工具栏如图 2-2 所示。 Altium Designer 10 的主菜单栏包括 File(文件)、 View (视图)、 project (项目)、 Window (窗口)和 Help (帮助)等。

左边为 Files Panels (文件工作面板),Navigator(向导),Projects(项目),右 边对应的是主工作面板,最下面的是状态条。其中项目栏是我们经常进行操作使用的地方, 需要说明的是左边的菜单栏目位置是灵活的,可以随自己的习惯进行移动。

图 2-2 Altium Designer 10 主工具栏

2.3 项目工程建立

2.3.1 在你工作区,新建一个文件包(例如在桌面建立个文件包,接下来的项目文件都 将存于该文件包内)。

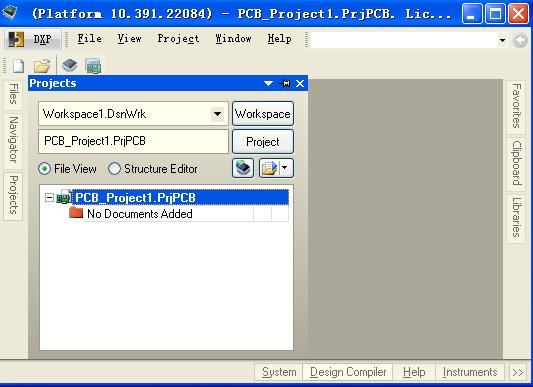

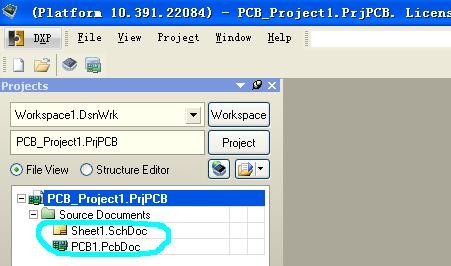

2.3.2 单击菜单【File】→ 【New】→ 【Project】→ 【PCB Project】, 默认为 PCB Project1. PrjPCB,完成后如下图 2.3 所示。

图 2-3 Altium Designer 10 新项目

2.3.4 保存这个项目

鼠标右击该项目图 →【Save Project】→指定文件包 , 或者通过鼠标点击【File】→ 【Save Project】。

2.3.5 建立原理图文件和 PCB 文件

单击菜单【File】→ 【New】→ 【Schematic】建立原理图文件(在你没有修改软件模板 的情况下,默认为 Altium 公司的模板) ,直接保存在指定的项目文件夹内。

单击菜单【File】→ 【New】→ 【PCB】建立原理图文件,保存在指定的项目文件夹内。

保存的方法与项目保存类似。

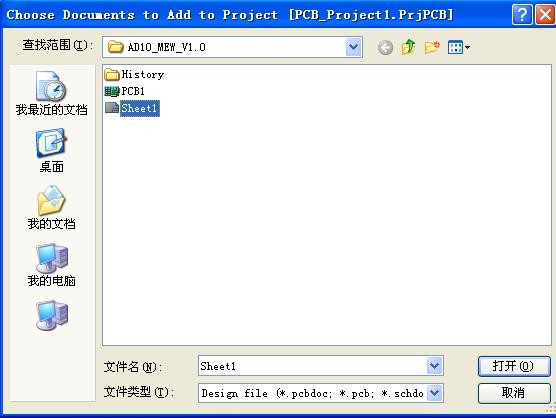

2.3.6 添加文件

添加已经建立的原理图文件和 PCB 文件到指定的项目中, 单击菜单【Project】→ 【Add Existing to Project 】, 弹出如图 2.4。

鼠标双击点击原理图后,便添加到指定的项目中,同样的方法,我们可将所创建的 PCB 文 件添加到指定的项目中。

同时我们还可以将项目需要的原理图添加到指定的项目中。

图 2.4 Add Existing to Project

图 2.5 Remove from Project

2.3.7 删除添加的文件

鼠标右击图 2.5 中的文件,在弹出的菜单类点击【Remove from Project】,即可将建 立的文件删除。

3、 Altium Designer 10 原理图设计

3.1 原理图模板设计

对于工程师来说,如果一直用 Altium Designer 自带的各种模板也是可以的,在这里我 将介绍一种建立模板的方法。当然,我们提倡反思,那就是我们是否该建模板,该怎么建模 板,建模板有什么有利之处,怎么用模板。

建原理图模板是使用方便规范,因为每个公司有每个公司自己的 LOGO,也有审核、校对、 项目名称、编号之类的。很多公司采取自己建立模板。对与模板的建立和使用在接下来会做 详细介绍。

3.1.1 建立并保存模板

对于保存的路径,建议保存在比较明朗的位置,待最后模板建立后再放入 Altium Designer 指定的位置。

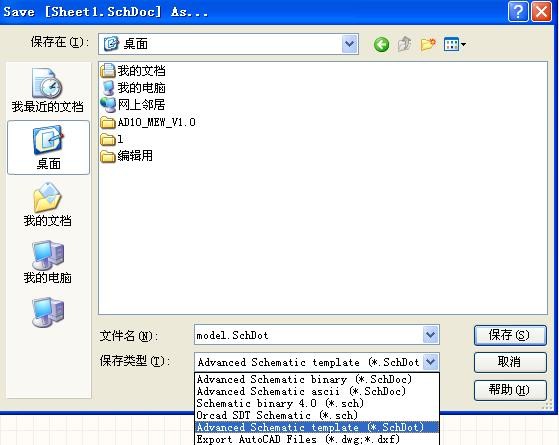

单击菜单【File】→ 【New】→ 【Schematic】建立原理图文件(在你没有修改软件模 板的情况下,默认为 Altium 公司的模板) ,在保存时注意保存格式,如果直接保存则为 “.SchDoc”格式,而模板格式为“.SchDot”格式。

选择保存类型“Advanced Schematic template(*.SchDot)”并将此命名为 model,如图 3.1。

图 3.1 建立并保存模板

3.2 对模板进行编辑

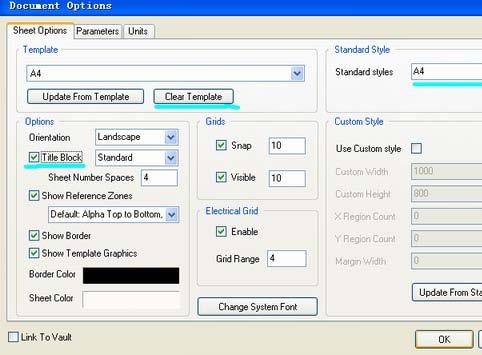

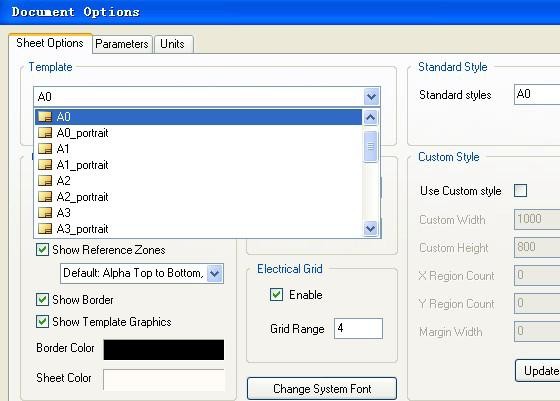

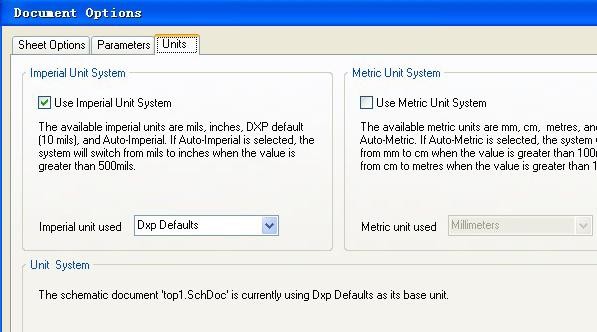

3.2.1 打开新建立的原理图模板 model.SchDot,点击【Design】→【Document Option 】。 或者与用快捷键 D+O 完成。如图 3.2 所示

在【Sheet Options】中对【template】中的原理图进行更新,选择你需要的大小,默 认为 A4, 但多说情况下,公司为选择 A3 的做模板。

对纸张做个简单的介绍

● 美制: A0 、 A1 、 A2 、 A3 、 A4 ,其中 A4 最小。

● 英制: A 、 B 、 C 、 D 、 E ,其中 A 型最小。

● 其它: Protel 还支持其它类型的图纸,如 Orcad A 、 Letter 、 Legal 等。

选择完成后,点击【Clear Template】,弹出对话框,点击【Yes】, 原有模板已被清空。

图 3.2 原理图模板设置框

3.2.2 设置你需要的格式

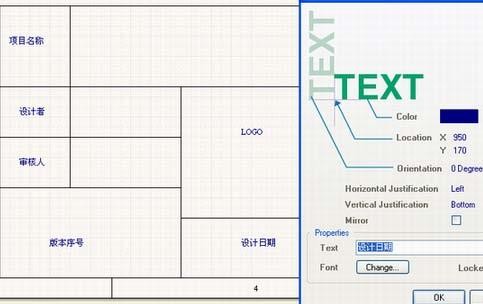

在一张空的原理图纸张上,首先确定你所用的表格以及 logo 的大小,规划好区域。在分 区时所用的划线:点击【Place】→【Drewing Tools 】→【Line】,快捷键 P+D+L。

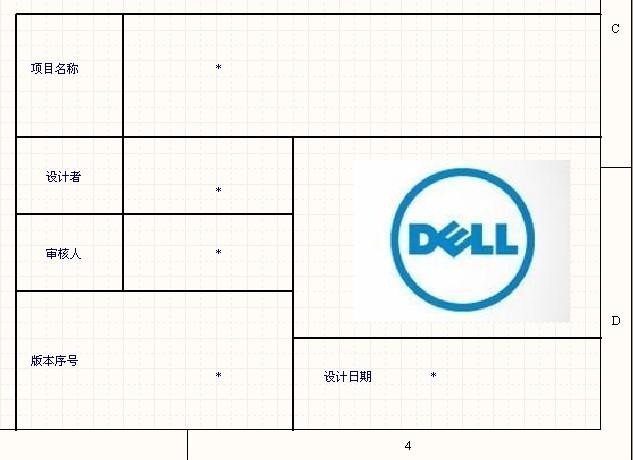

在区域规划完毕后,放置每个分割区的内容:【Place】→【Text String 】,在键盘中 按下【tab】键,输入你需要的内容,点击确定即可。如图 3.3

图 3.3 原理图模板内容编辑 1

3.2.3 将设计用用到的“项目名称、设计人、审核人、logo”等信息添加到参数中

【Place】→【Text String 】+【tab】,选择对应的选项

项目名称:=Title

设计者:=Engineer

审核人:=Address1

版本序号:=Address2

设计日期:=Date

对于 logo 的添加则用到【Place】→【Drewing Tools 】→【Graphic】,例如我们放 入一个 JPG 格式的“Dell”。

完成效果如图 3.4

图 3.4 完成后的原理图模板内容编辑

3.2.4 将模板放置到指定的路径

复制该模板, 找到该路径 C:\Documents and Settings\All Users\Documents\Altium\AD 10\Templates,粘贴模板。

3.2.5 将该模板添加到 AD10 原理图里面

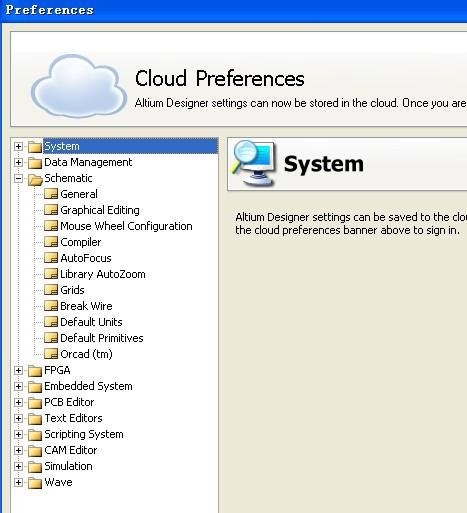

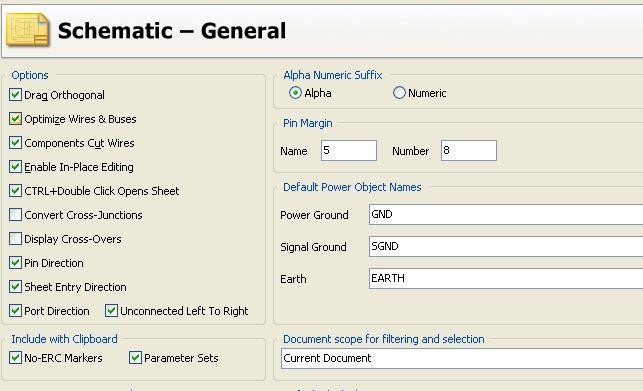

只 要 在 软 件 的 参 数 设 置 ( 菜 单 DXP->>Preferences->>Schematic->>General) 中 模 板(Template) 选项下把创建好的模板文件添加进来,选项下把创建好的模板文件添加进来,每次新建原理图都会把该模板添加到设计中。

3.3 元件原理图库设计和 PCB 封装的设计

3.3.1 建立库

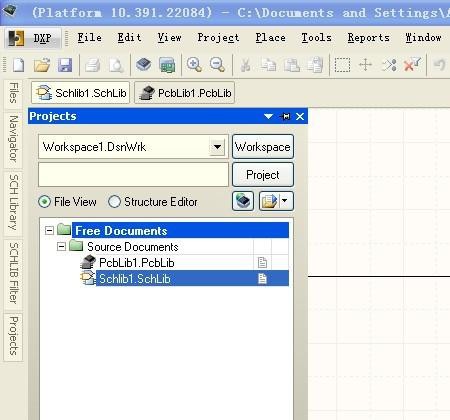

【File】→ 【New】→ 【Library】→ 【Sch Library】原理图库建立,

【File】→ 【New】→ 【Library】→ 【PCB Library】封装库建立,

图 3.5 元件库和封装的建立

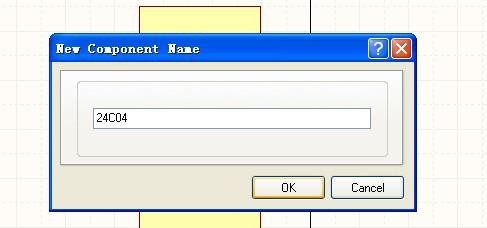

建立新元件【Tools】→ 【New compoment】,这里以 24C02 为例。

图 3.6 元件命名

查看电气特性。

图 3.7 查看 24C02datasheet

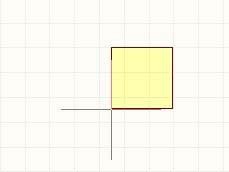

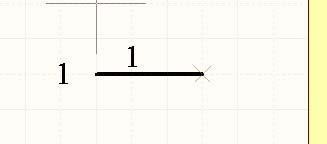

放置外形和管脚快捷键 P+R, 调整合适的小。放置管脚 P+P, 然后单击键盘的 Tab 键弹出管脚属性对话框,修改相应的属性。

图 3.8,放置外框 图 3.9 放置管脚

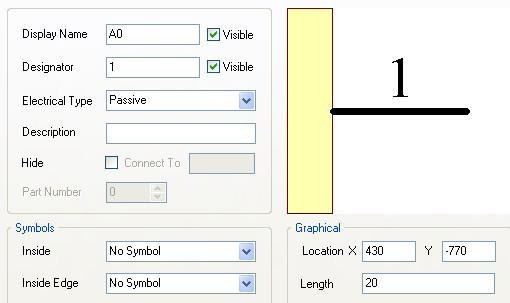

在 Pin Propertis 中,Display Name管脚定义,Designator 是管脚序列号,其后 有Visable,是否可见,在原理图中有些元件有衬底,我们通常将带衬底的管脚隐藏,管脚的长度 Length 可以根据需要设定。对有负信号,例如负电压,负电平复位脚等,需要添加"\" 符号 , 如“V\C\C\”表示负的 VCC 电平,类似数字电路中的非格式。

图 3.10 管脚属性

图 3.11 24C02 原理图

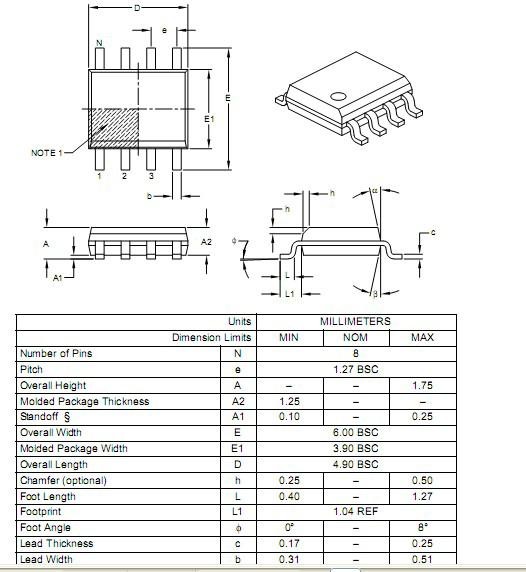

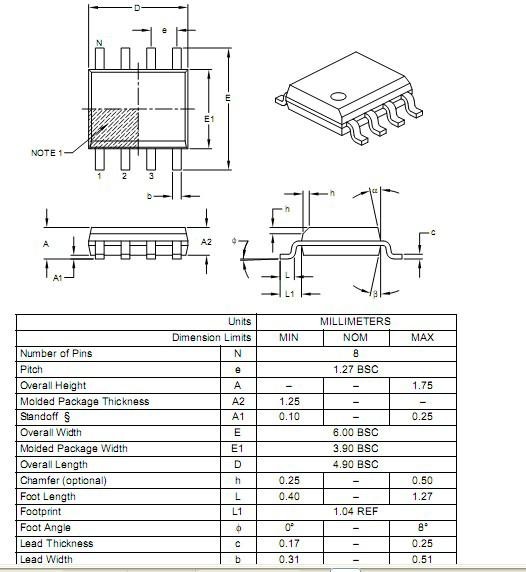

查看 24C02 的 footprint,资料如下。

图 3.12 24C02 footprint 资料

在 pcblib 环境下用向导制作元件封装。

【Tools】→ 【 Compoment Wizard 】弹出下图,

图 3.13 Compoment Wizard

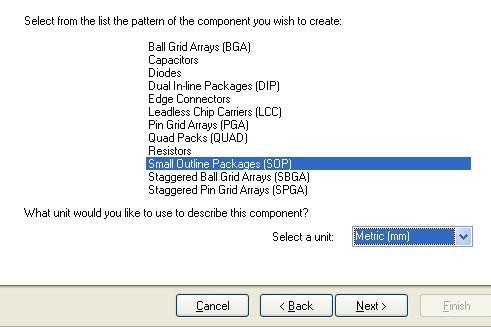

图 3.14 footprints 类型

在 pcblib 环境下用向导制作元件封装。

【Tools】→ 【 Compoment Wizard 】弹出下图,

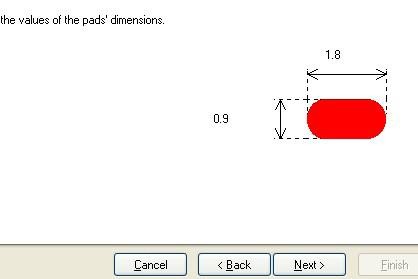

一般贴片的的引脚焊盘大于管脚 8mil 到 20mil,也可以大于这个数,根据具体的情况。对有有些 BGA 封装的,有时候焊盘还可能略小于管脚。

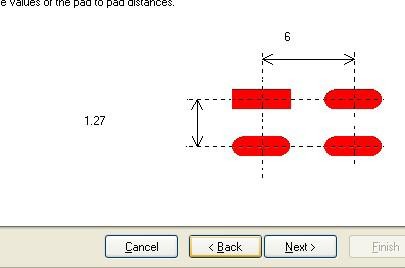

图 3.14 管脚焊盘大小设置

图 3.15 管脚间距大小设置

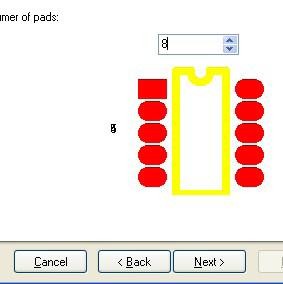

图 3.16 管脚数目大小设置

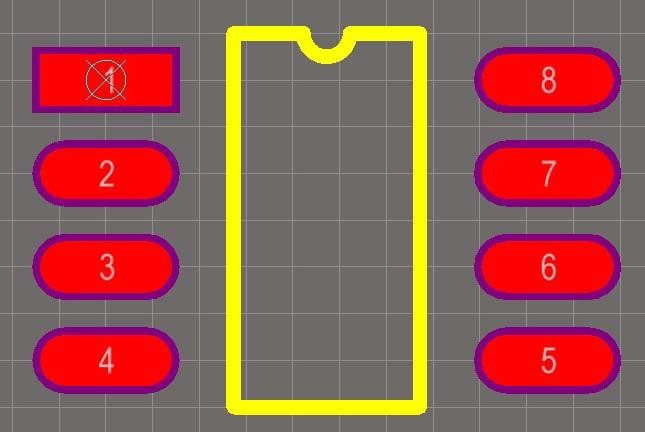

图 3.17 完成封装设计

3.4 整体库制作

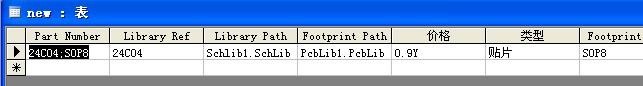

下面介绍中用 ACCESS 把数据表文件,原理图封装制作在一个整体库中,这样的优点是,能 将各个元件的信心综合在一个表格里,并在原理图中找到这些信息,在到处 BOM 的时候可以 将这些信息导出,便于采购确定元件,成本核算。

图 3.18 整体库中的文件

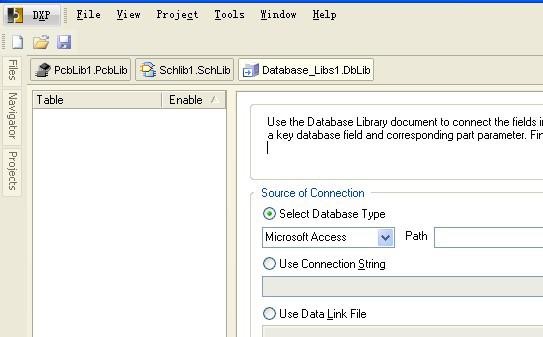

【File】→ 【New】→ 【Library】→ 【Database Library】建立, 在 access 中建立 .mdb 文件,注意命名与 Database Library 文件的一致性。

图 3.19 【Database Library】设置

在 Source database type 中 pass 中添加该文件,注意添加路径。

图 3.20 access 文件设置

在 access 文件中,对元件的相关信息进行设置,完了添加到库中

图 3.21 集成库添加

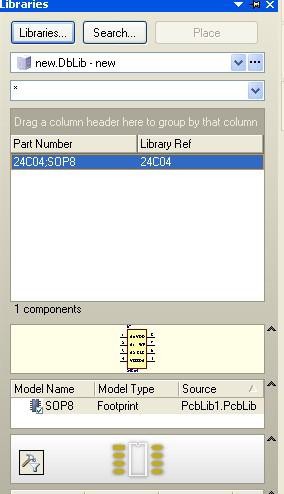

在库的栏目中调用该库,可以看到已经添加的元件

图 3.22 集成库中所显示的元件

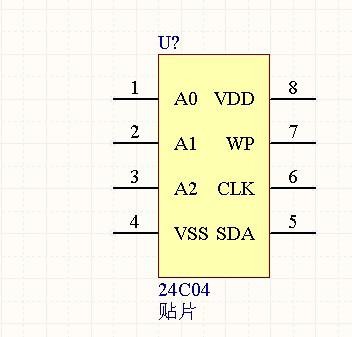

图 3.23 原理图放置元件

在库中双击该元件,在原理图中鼠标位置出现该元件,右击停止放置该元件。

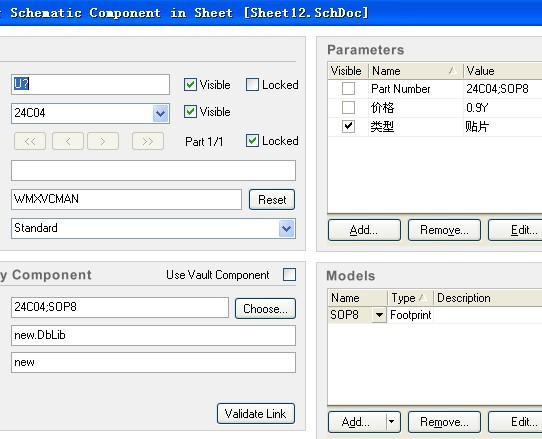

图 3.24 元件信息

双击元件可以显示上面的信息。

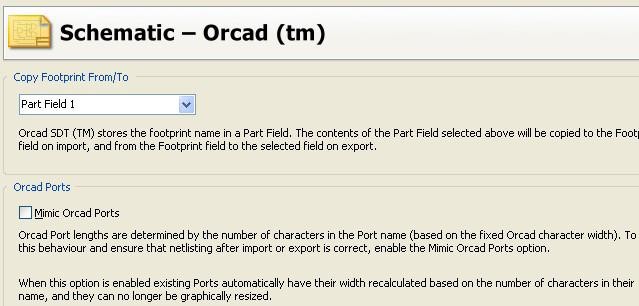

3.5 原理图编辑设置

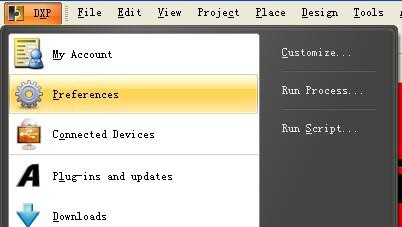

关于原理图中的设置,这里只介绍常用的【DXP】→ 【Preferences】

图 3 .25 原理图放置

图 3 .26 Schematic/p>

在 Defaults 的 Template 中添加自己的模板,注意将自己的模板保存在 AD10 指定的路径。

图 3 .27 原理图模板添加

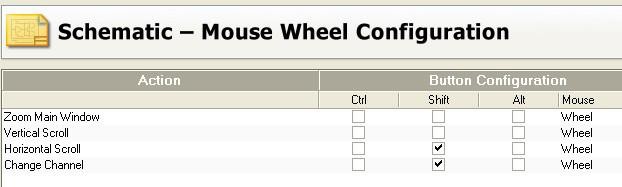

设置鼠标用滚轮控制原理图的缩放,在 PCB 环境中也是这样设置的

图 3 .28 鼠标设置,去掉 Ctrl 你面的勾

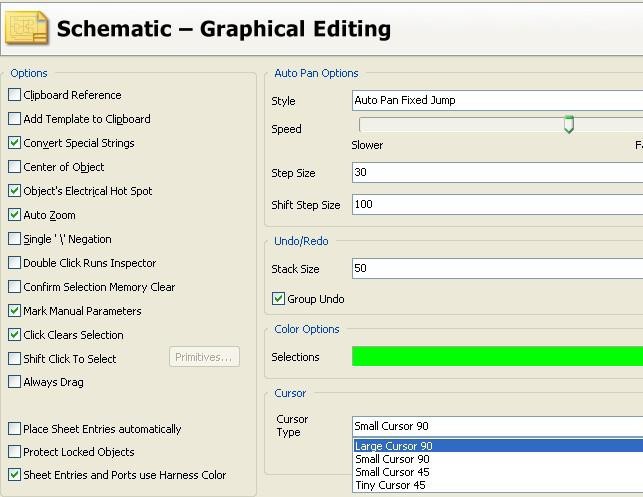

对鼠标显示的设置,Cursor Type 推荐使用 Large Cursor 90,在放置元件时,元件保证在一条直线上。

图 3 .29 Cursor Type 放置

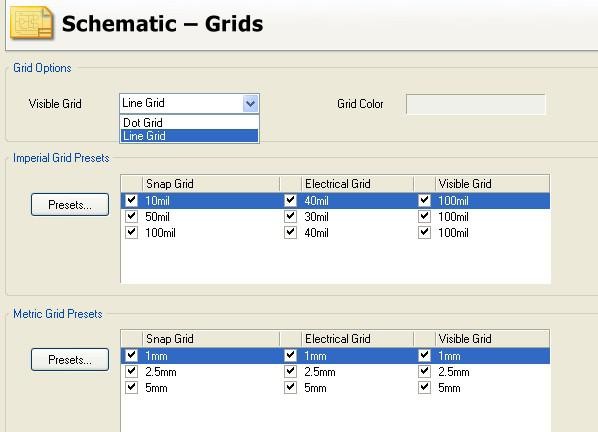

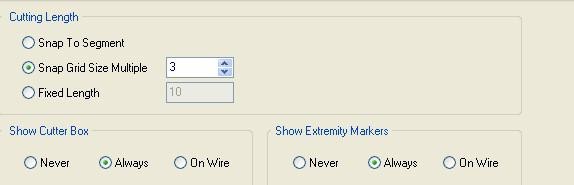

Grid Options 设置是在原理中的显示方式,在打印时选用 Dot格式的,平时选用Line格式,同时在放置元件的时候,要保障你所放置的元件电气管脚在点栅格的点上,NET 放置也是如此,否则会出现原理图中的线在 PCB 环境中并没有连接。

图 3 .30 Grid Options 设置

图 3 .31 原理图放置

图 3 .32 原理图放置

3.6 原理图文件设置

对原理图的编辑文件的设置,打开原理图右击找打 Docment Options 显示如下

图 3 .33 原理图放置

在 template 中添加模板,在右侧选择纸张,在 Girds 中填写栅格,在下发选择 enable

图 3 .34 原理图模板放置

图 3 .35 原理图内容填写放置

图 3 .36 原理图放置

3.7 元件的排序

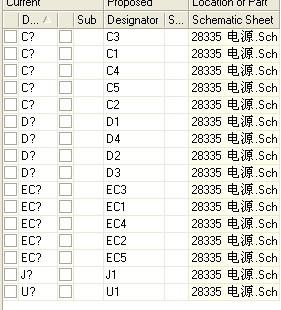

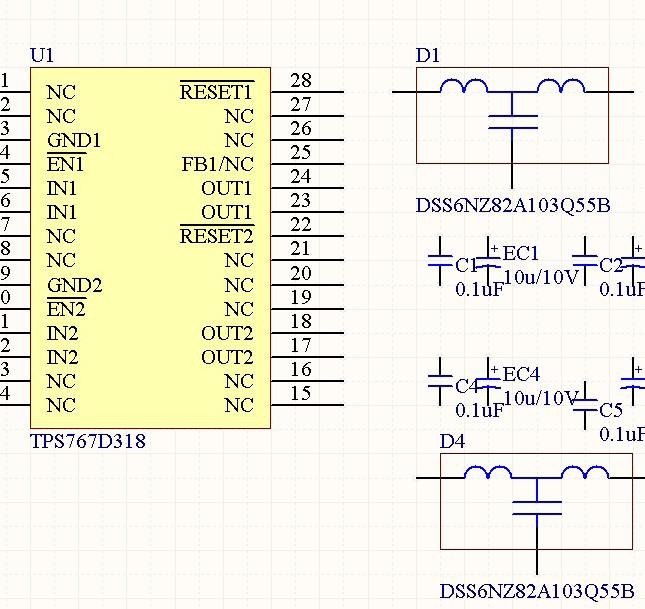

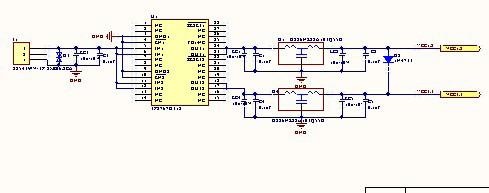

1. 关于元件自动排序的问题

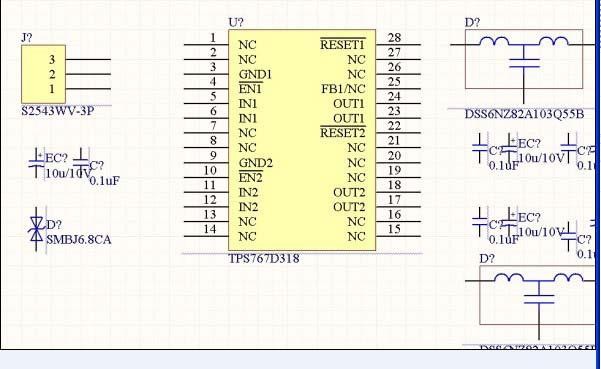

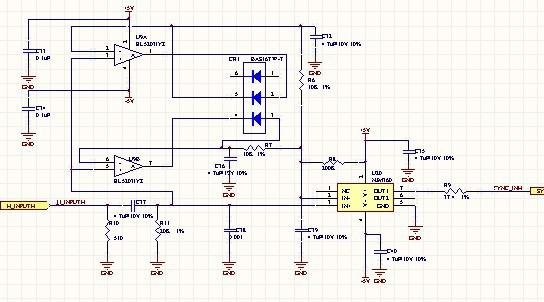

接着对于放置后的元件进行排序,在上一步我们设置完原理图的工作环境后,从库中选取需要的元件,设计电路,但这些元件默认没有标号,整体以问号的格式显示在原理图中。如下为一个电压转换电路,是一种常用的 5V 转 3.3 和 1.8 的电路。

图 3 .37 原理图元件放置

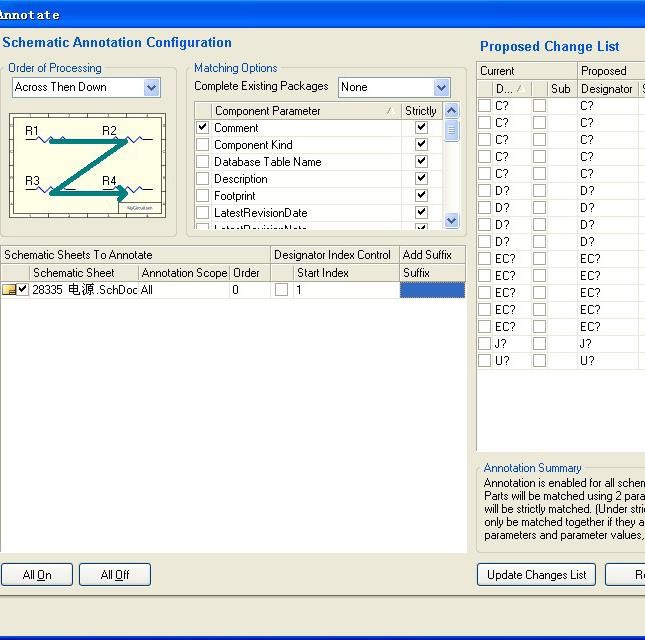

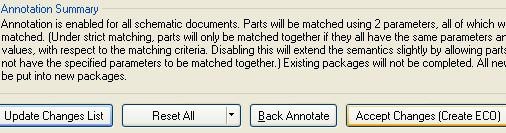

回到排序,【Tools】→ 【Annotate】(快捷键 T+A)

在下图中,order of Processing 元件的顺序,在 Schematic Sheets to Annotate选择对应的原理图,在截图中有一张原理图,实际中可以是好多张,同时可以设置每个原理图序列号的起始数和后缀,分别对应 Satart index 和 suffix。

点击 update changes List,更新排序,如果出现重复,有时候会用到 reset Duplicate,或者 reset all,如果用到 Back Annotate,注意原理图与 PCB 元件的 ID 号是否对应,必要时在 PCB 环境下,进行 CompontLink 操作。

图 3 .38 元件排序

图 3 .39 元件排序

图 3 .40 元件排序

排序完成点击 EXecute Changes,执行排序。

图 3 .41 元件排序

回到原理图看到元件顺序已经排列完成。

图 3 .42 元件排序

3.8 连线和元件位置转化

在这里介绍下放置元件的一些技巧,元件方向的调整,通过空格键进行切换。对于一些特殊的,如三极管,集成芯片,还可以对其做对称处理,以方便连线,鼠标左击元件不放,按下键盘 X,Y,其中 X 是左右,Y 是上下。对于连线,快捷键是 P+W 连线,P+B 总线,放置 net, P+N放置注释 P+t,总之点击 P 后仔细看下,就可区分你需要用的工具。

图 3 .43 完成布线的图

3.9 层次原理图的设计

两类,一类是自定向下的设计,此时,我们已经知道所有已经定义好的接口,尤其像合作搞原理图设计,在顶层把所有的端口分配好,直接生成不同的原理图,在原理图中会显示所用到得接口。另一类,自下向上的设计,这是我们可以先专注于局部电路的设计,并在设计过程中放置端口,最后通过顶层原理图将用到的局部原理图整合在一起。

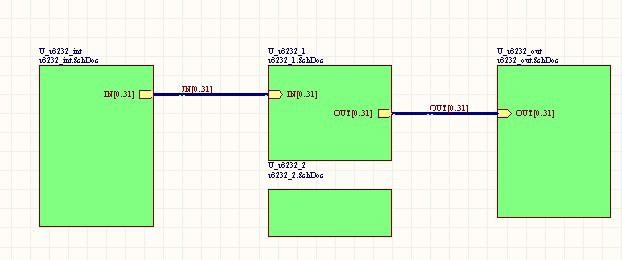

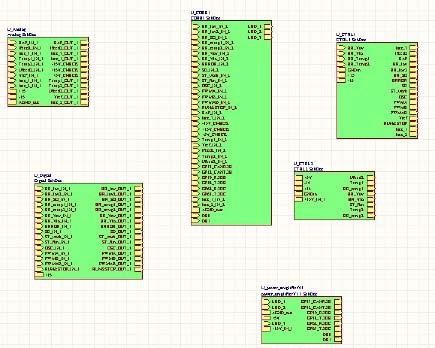

第一类的步骤:以 3232 同步信号为例,简要介绍如何从顶层向下生产原理图。

建立 top 层的原理图,

放置 sheet symbol

【Place】+【sheet symbol】

放置 port

【Place】+【add sheet entry】

将图纸端口连接起来

图 3 .44 连接不同模块

【Design】+【Creat Sheet From Sheet Symbol】( 快捷键是 D+r 然后鼠标单节所对应的模块 )

图 3 .45 生产原理图

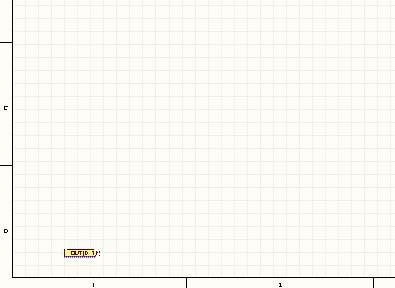

按照上面的操作,我们可以生产所需的原理图纸,不过所有的原理图纸只有对应的 port端口

图 3 .46 整体原理图处于打开状态

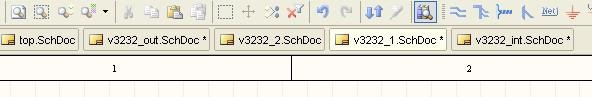

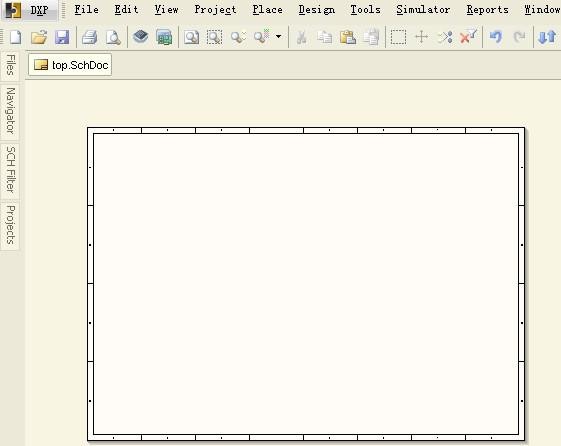

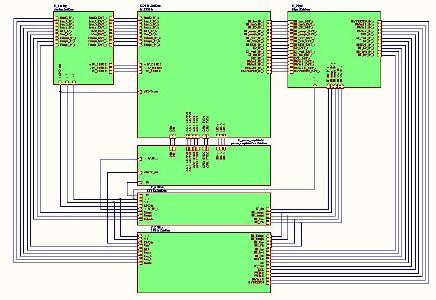

层次原理图中的自底层向顶层设计

首先,我们要建立工程中的所需要的各个原理图模块,放置在一个文件架立,然后在建立顶层原理图,此时为空白的原理图,在空白的原理图中直接生产 sheet 块,用导线或者总线将这部分模块连接起来。具体操作如下

图 3 .47 打开顶层原理图

放置模块的方法,快捷键 D+Y。

图 3 .48 添加模块,调整端口

图 3 .49 完成连线的图

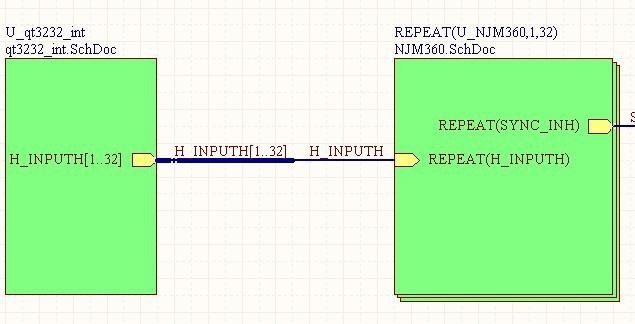

3.10 关于多通道的层次原理图的设计知识的补充

在多通道设计之前工程师必须分析清一下 port 与 net label 的作用范围。

“Poet”及“Net Label”的作用范围

两种网络标识的作用范围是可以变化和更改的。方法是:打开 Project \ Project Option \ Option 标 签, 在 Net Identifier Scope 一 栏 的 四 个 选 项 (Automatic、Hierarchical、Flat、Global) 中挑一项。

“Hierarchical”代表层次式结构,这种情况下,Net Label,Port 的作用范围是单张图纸以内。当然,Port 可以与上层的 Sheet Entry 连接,以纵向方式在图纸之间传递信号。

“Flat”代表扁平式图纸结构,这种情况下,Net Label 的作用范围仍是单张图纸以内。而 Port 的作用范围扩大到所有图纸,各图纸只要有相同的 Port 名,就可以发生信号传递。

“Global”是最开放的连接方式,这种情况下,Net Label、Port 的作用范围都扩大到所有图纸。各图纸只要有相同的 Port 或相同的 Net Label,就可以发生信号传递。

“Automatic”是缺省选项,表示系统会检测项目图纸内容,从而自动调整网络标识的范围。检测及自动调整的过程如下:如果原理图里有 Sheet Entry标识,则网络标识的范围调整为Hierarchical。如果原理图里没有 Sheet Entry 标识。但是有 Port 标识,则网络标识的范围调整为 Flat。如果原理图里既没有 Sheet Entry 标识,又没有 Port标识,则 Net Label的范围调整为 Global.

3.11 关于 room 在多通道设计中的应用

图 3 .50 同步信号均衡电路

图 3 .51 使用 repat 实现重复功能

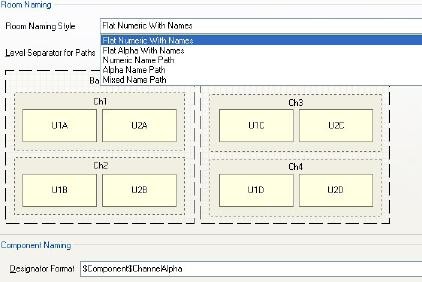

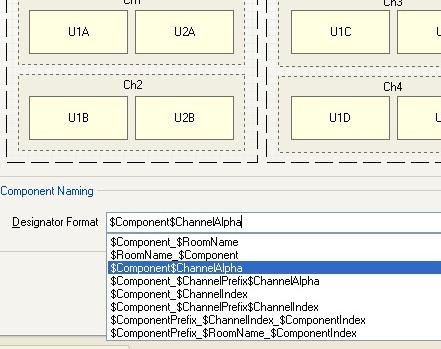

图 3 .52 room 名称的设置

图 3 .53 元件后缀的重复名字

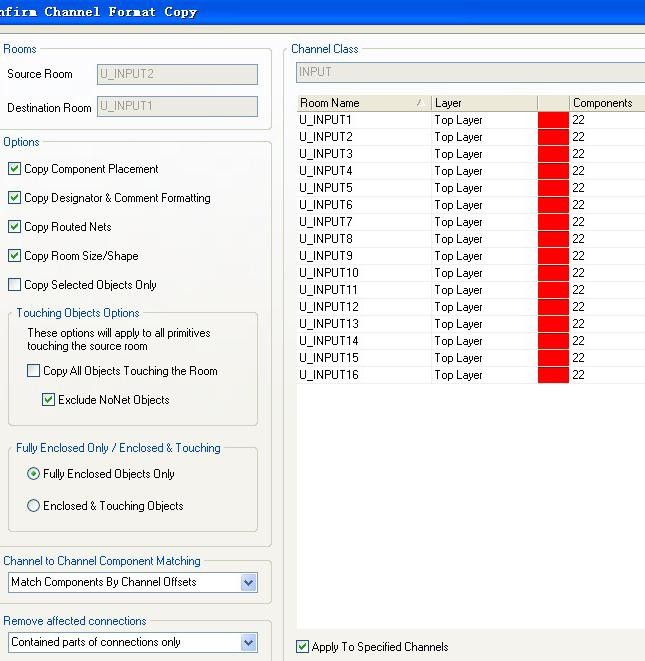

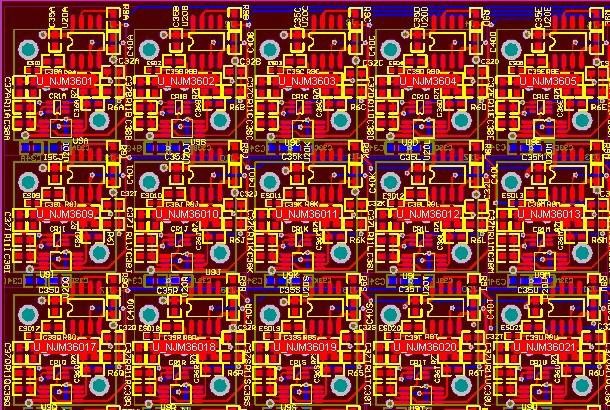

在完成上述设置后,到 PCB 环境中对其中一个进行布线,单个布线完成,用格式刷,将其余的通道,操作如下。

在【Design】→ 【Rooms】→ 【Copy room formats】,鼠标点击布线完成的 room,再点击需要刷的 room,弹出下图。

在下图中,主要元素是你所复制的内容,通过 Options 项确定,对于需要修改的其他 room,有 Apply to Specilied Channels 决定。

图 3 .54 格式刷设置

图 3 .55 单个 room

图 3 .56 格式刷后 room,调整位置

3.12 原理图初步编译

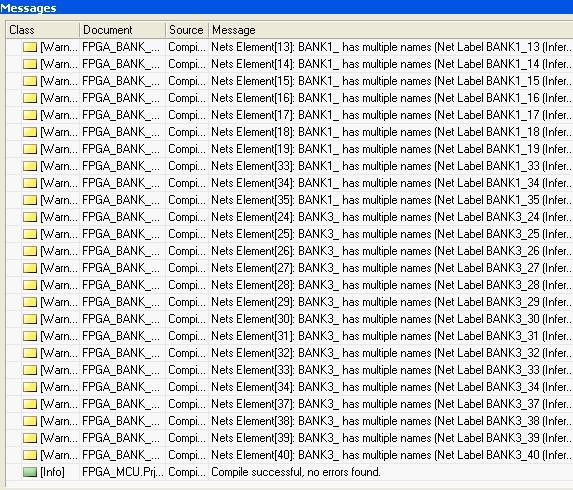

在以上设置完成后就是对原理图的编译,接下来我们以一个实例来展示下编译的过程

在 Project 中compile PCB projects .prjPCB, 快捷键为 C+C,即可完成

图 3 .57 编译

弹出如上图的对话框,如果没有弹出,在右下方有 Syetem 选项打开,里面有 Message 选项,打开便可看到,至于图中提示的,网络命名重复,这个是不会影响导入 PCB 时候的连线。

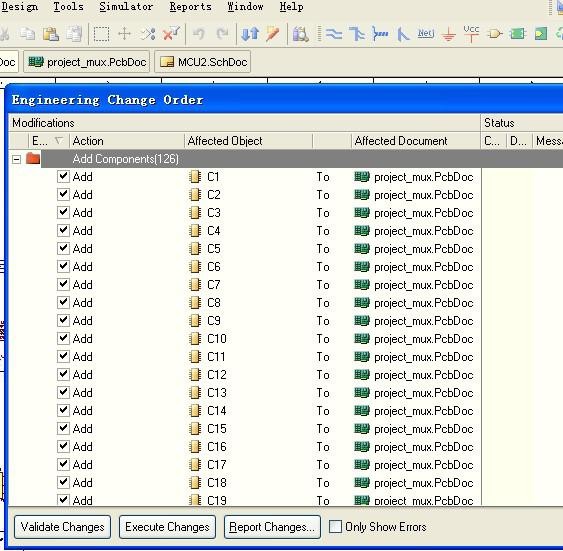

在新建的 PCB 中导入编译的网络,具体的操作时,在原理图的环境下,单击 Design 中的Updata from sch to PCB 中,弹出下图,点击 Execute Changes

图 3 .58 导入网络

3.13 差分对的有关操作

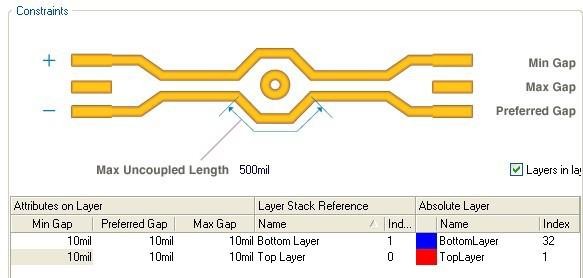

对于差分对设计,尤其是高速电路时,差分要求等长处理,这是就会出现所谓的蛇形走线。

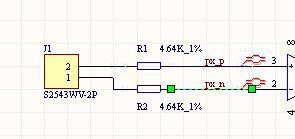

在下面的两幅图中体现了独立的差分对和多对差分对的处理方法。 在差分对中主要是放置 Net 和差分对符号。Net 放置时注意放置 Net 的后缀,“_ P”,"_N", 大小写都可以;另一个是放置差分对标号:【Place】【Driectives】 【Differential Pair】

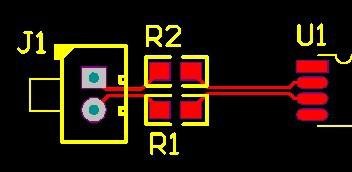

图 3 .59 差分对原理图

图 3 .60 差分对设置

差分对布线 P+I,

图 3 .61 差分对原理图

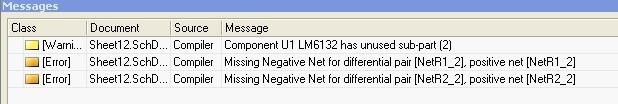

原理图中缺少 net,或者 net 格式不正确,会出现 ERC 测试错误

图 3 .62 差分对报错

没有放置差分对标号,在布线时,使用差分走线,会报错。

图 3 .63 差分对报错

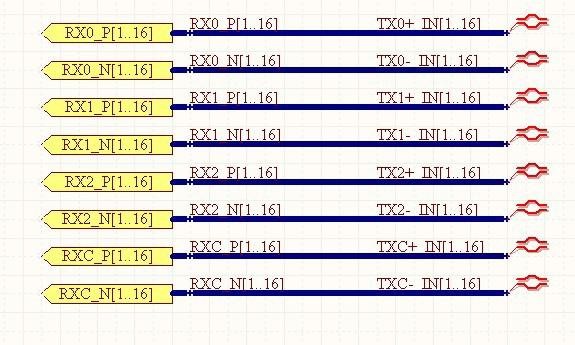

图 3 .64 差分对在总线格式下

图 3 .65 差分对总线格式下 PCB 布

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?