一、软硬件环境

硬件 | ZedBoard |

|

软件 | 操作系统 | Window 7 SP1 x64 |

Ubuntu 12.04 LTS | ||

Vivado | 2013.4 for windows | |

交叉编译工具链 | https://zedboard-book-source.googlecode.com/files/xilinx-2011.09-50-arm-xilinx-linux-gnueabi.bin | |

嵌入式Linux(Digilet官方发布的Linux内核) | ||

uBoot | ||

Device-tree | ||

其他 | 串口调试 | Tera Term |

说明:有地方使用的linux版本是https://github.com/Xilinx/linux-xlnx,

Uboot是https://github.com/Xilinx/u-boot-xlnx,没有测试过。

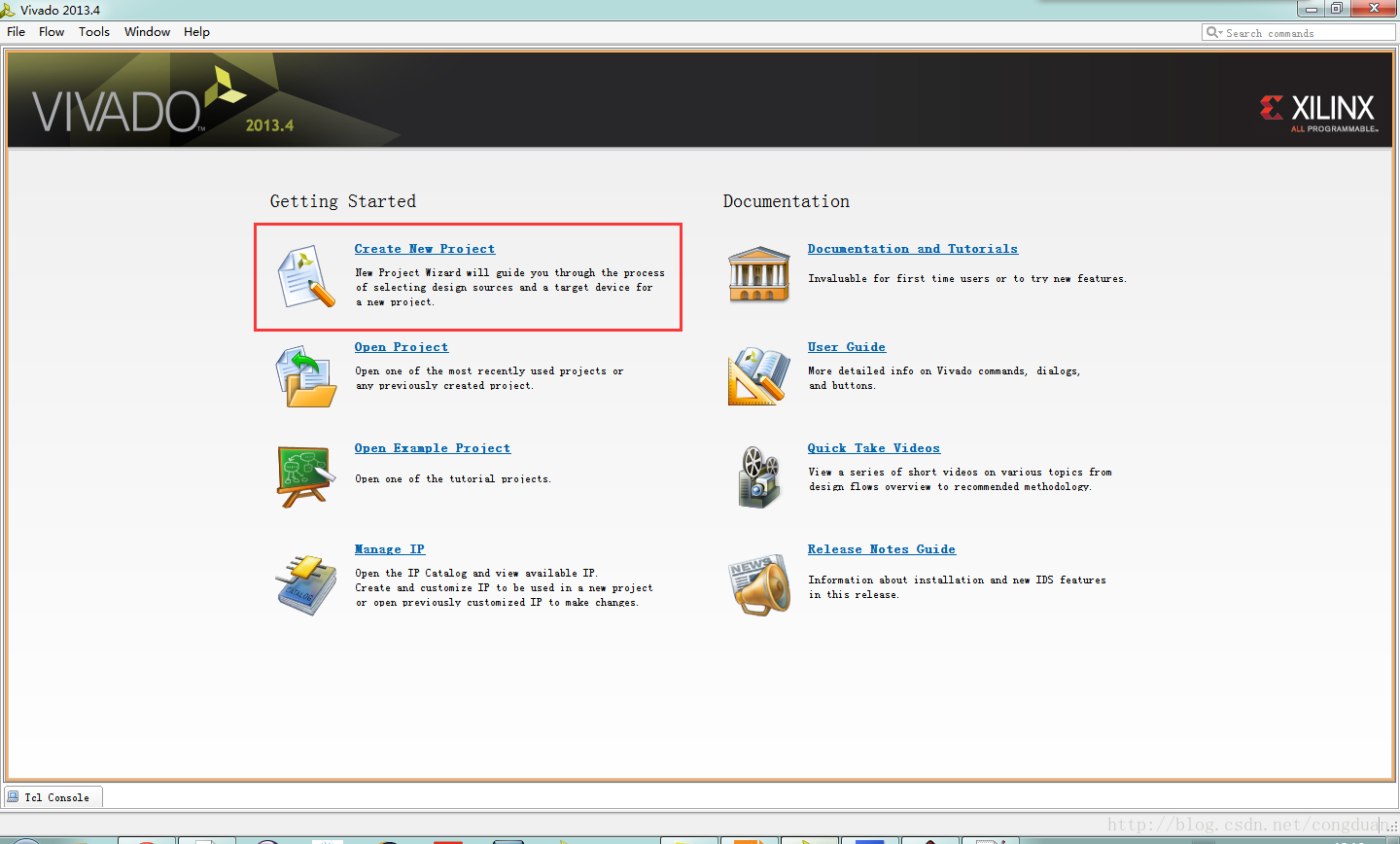

二、搭建硬件工程

创建一个最简单的Zynq项目,如下:

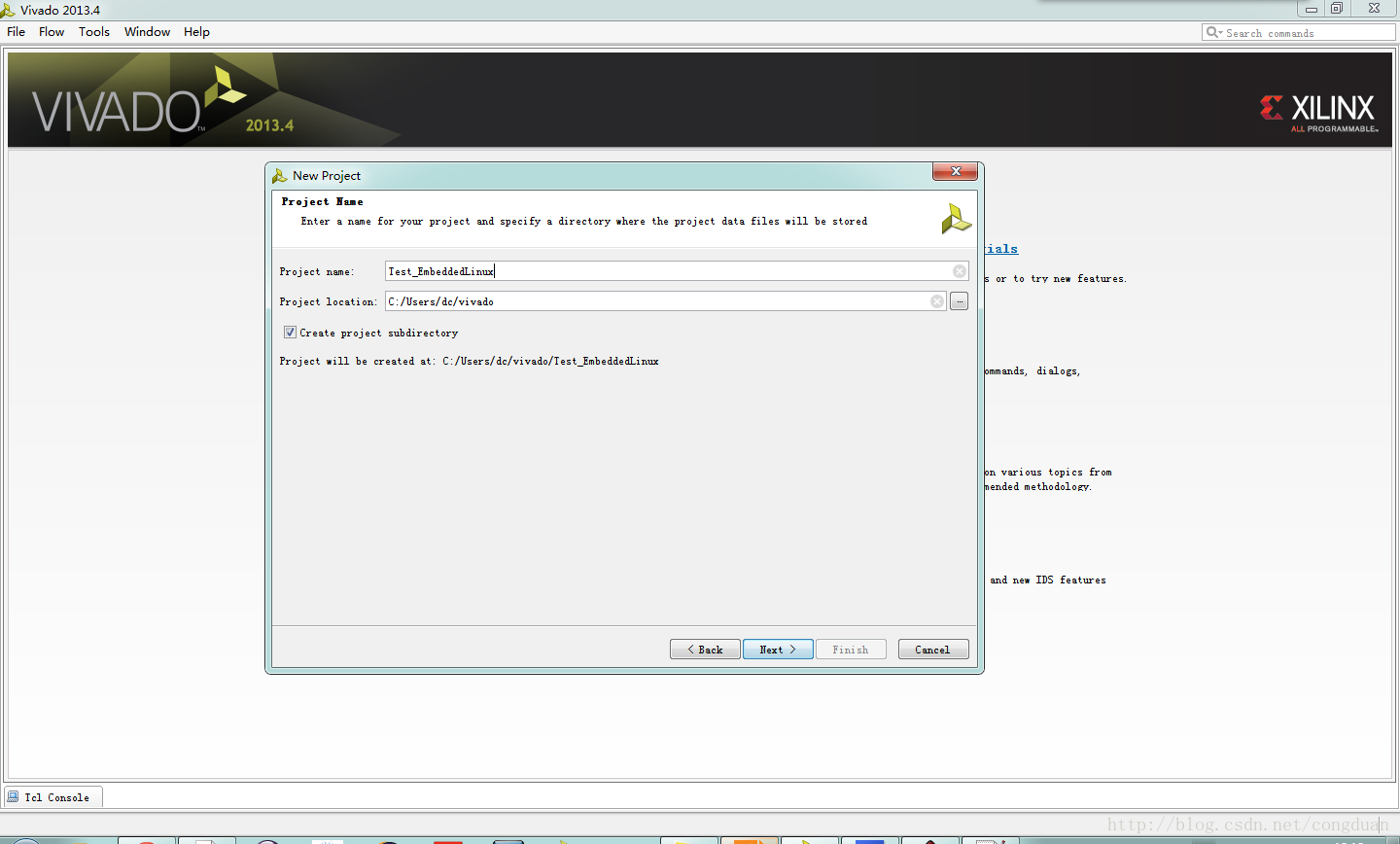

选择Next

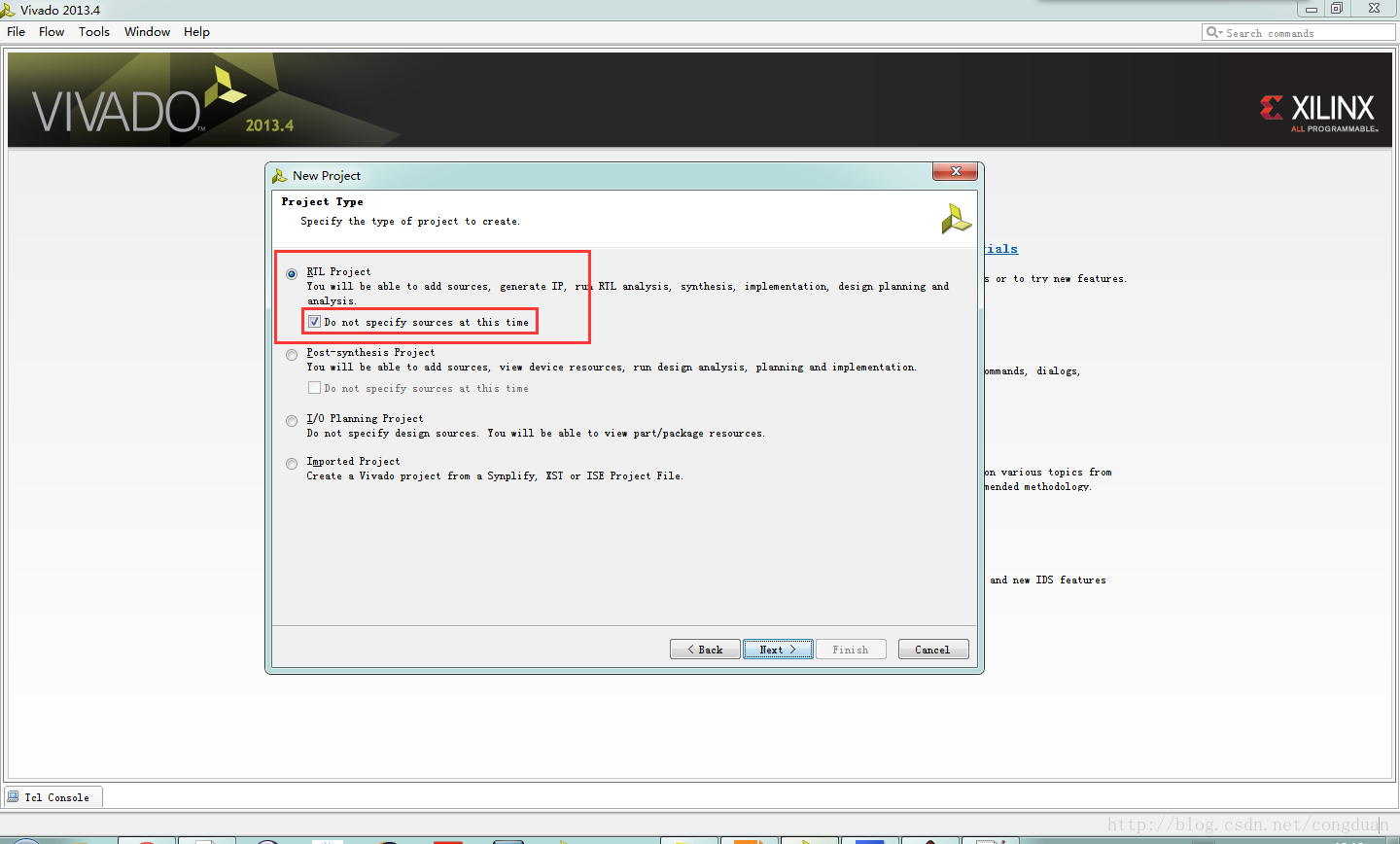

点击Next,我们不需要添加Verilog/VHDL源文件或者约束文件,勾选Do not specify sources at this time

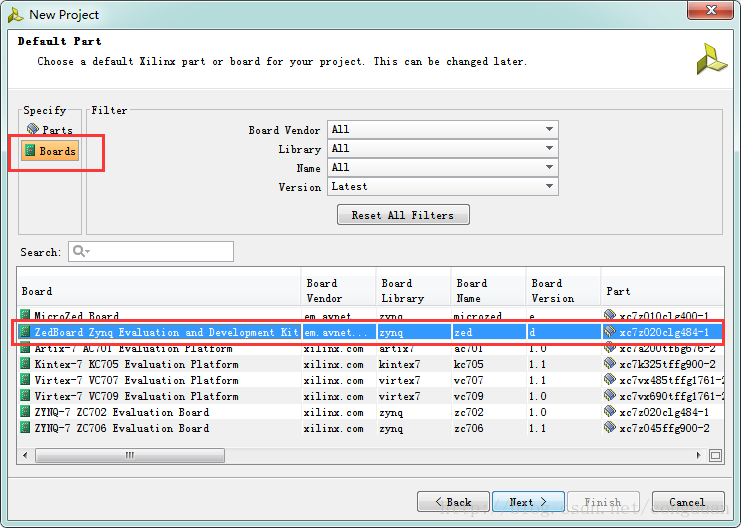

点击Next,选择Boards,并选择ZedBoard Zynq Evaluation and Development Kit

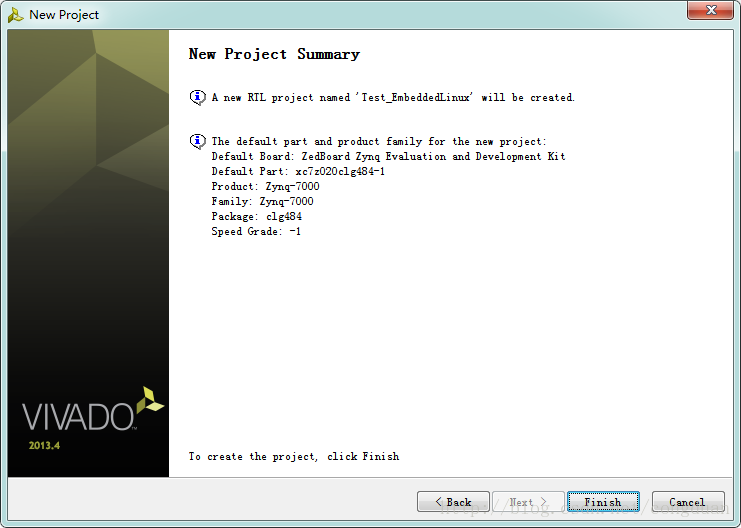

点击Next

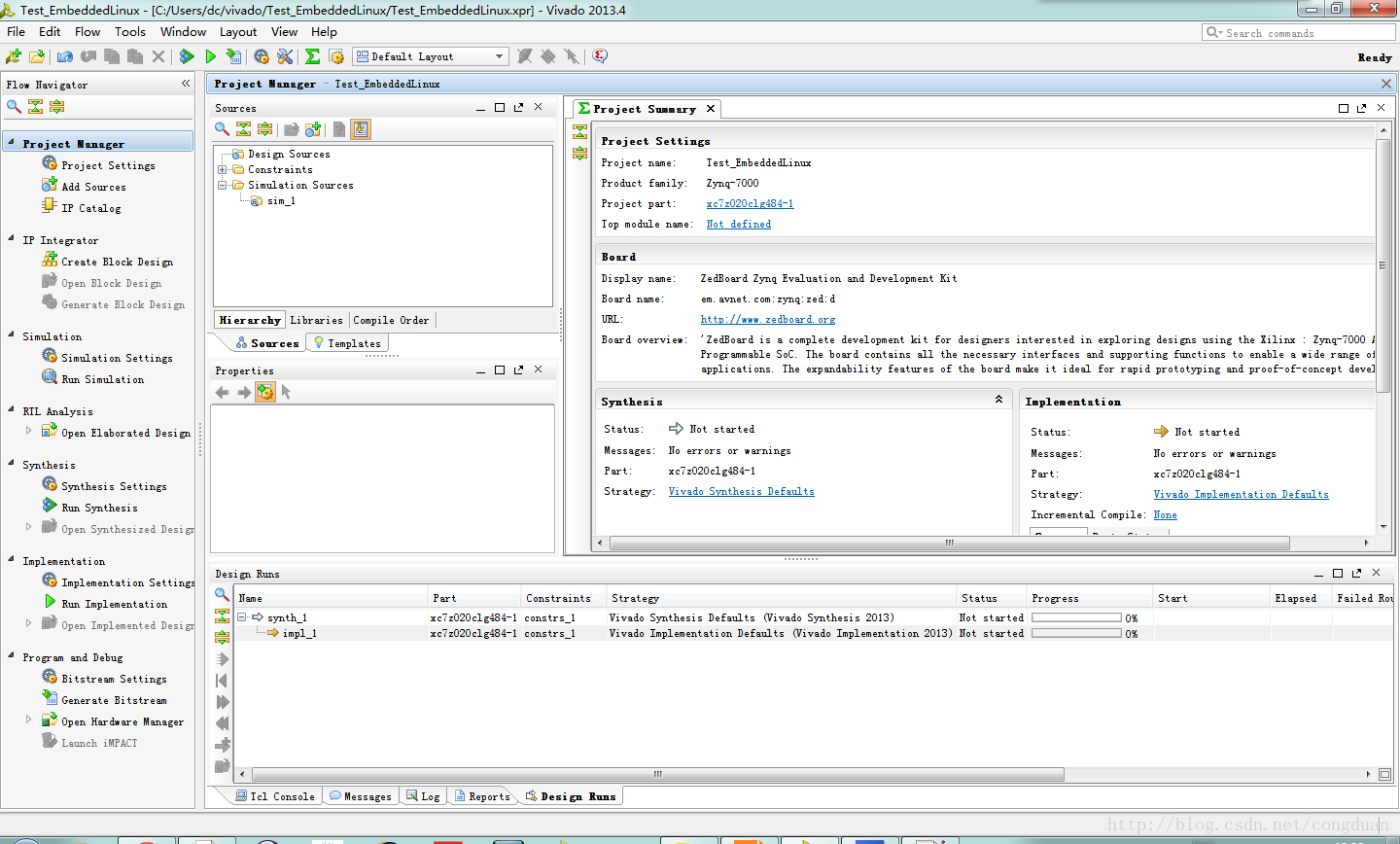

点击Finish完成创建向导,出现如下界面

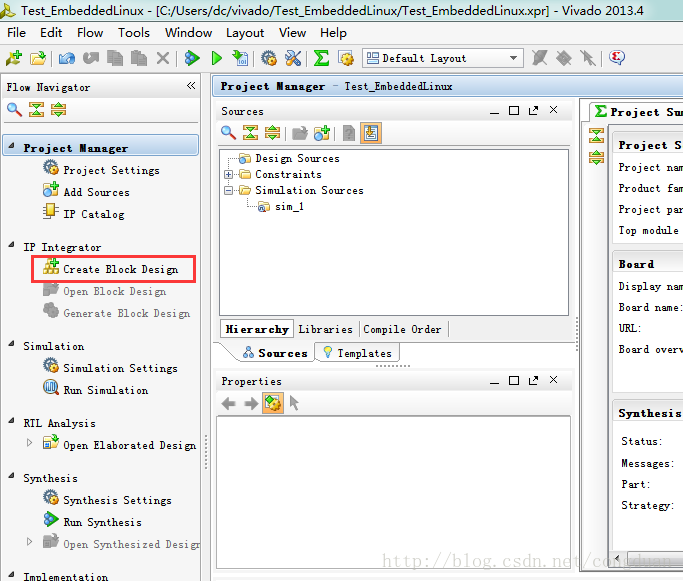

先创建一个Block Design,点击如下地方

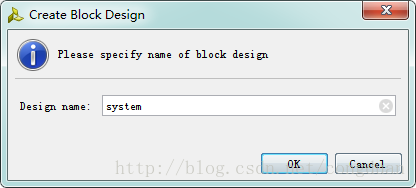

输入名称

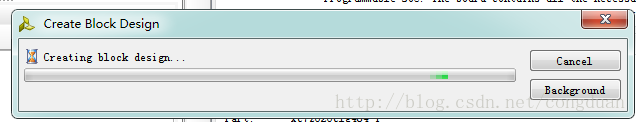

等待创建完成

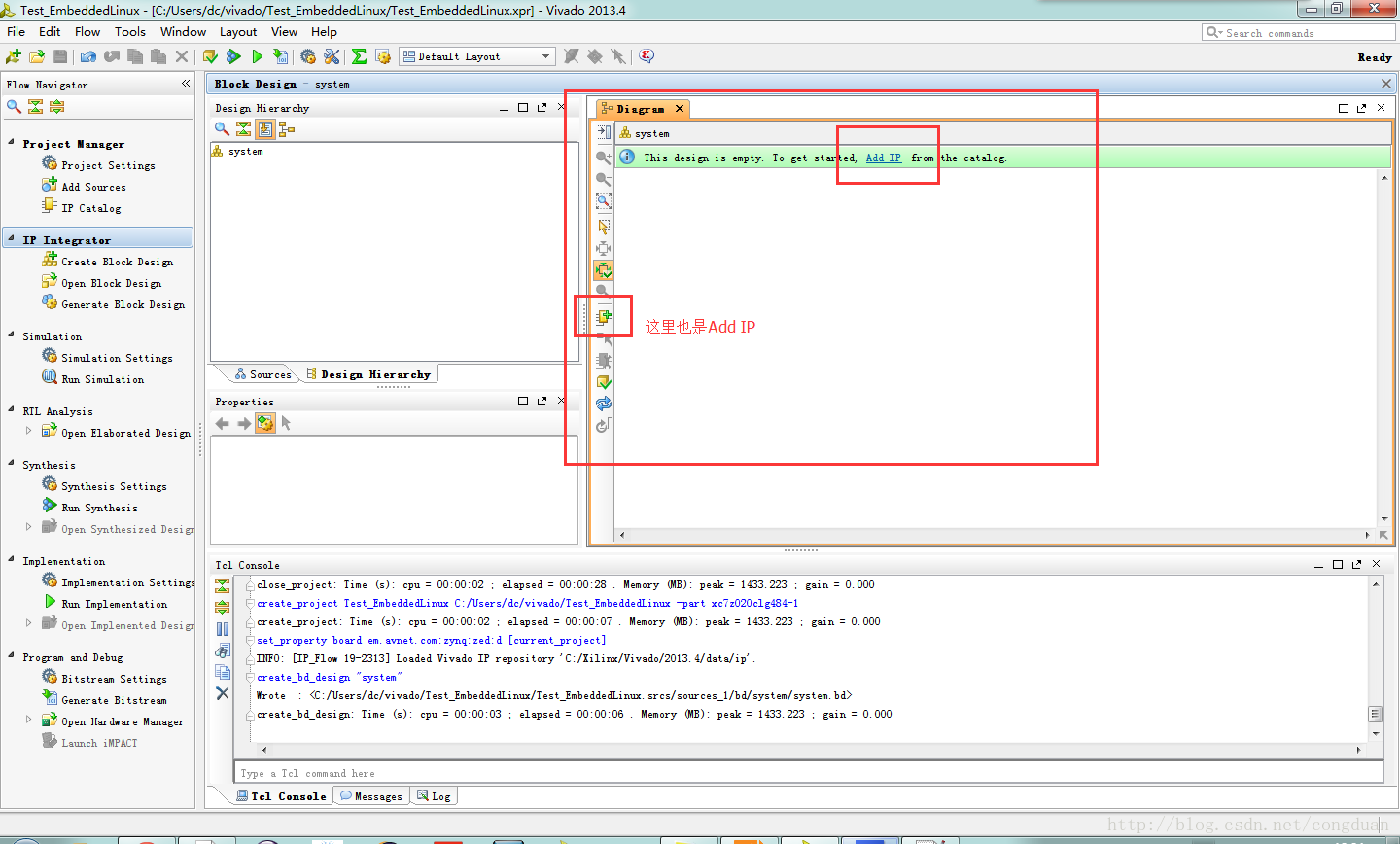

在Diagram视图中点击Add IP

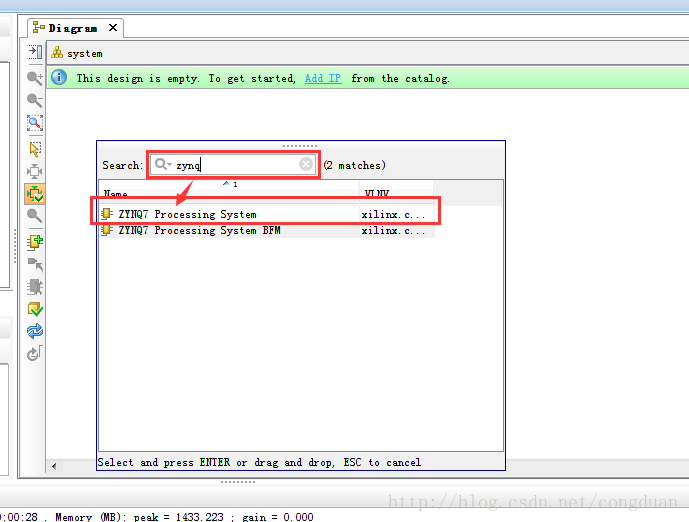

在弹出的窗口中输入Zynq进行搜索,在结果中选择第一个

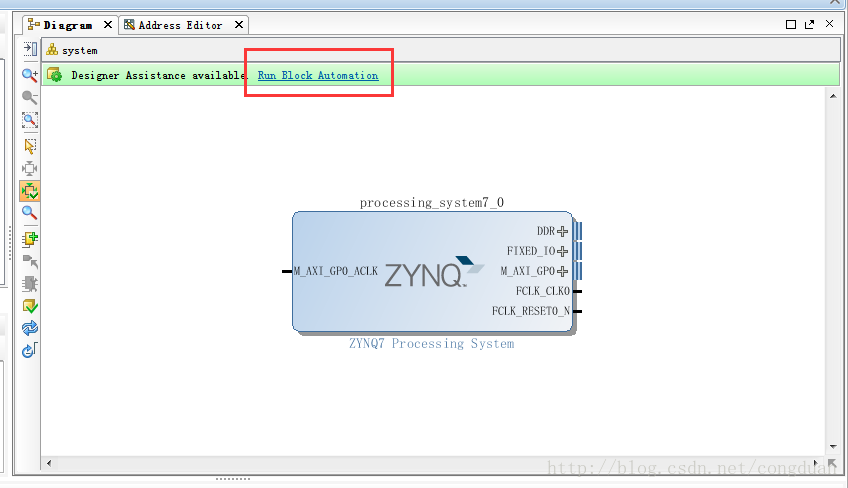

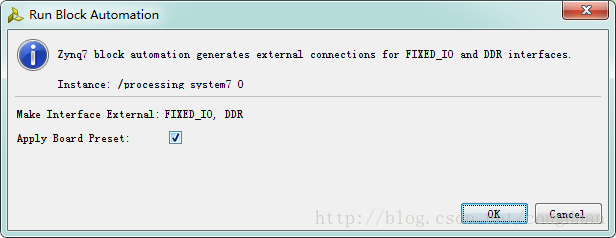

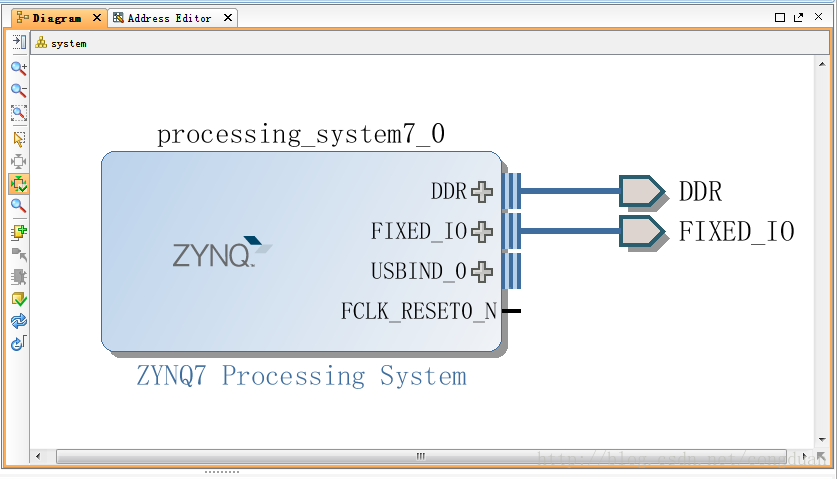

点击Run Block Automation,并选择/processing_system7_0完成自动连线

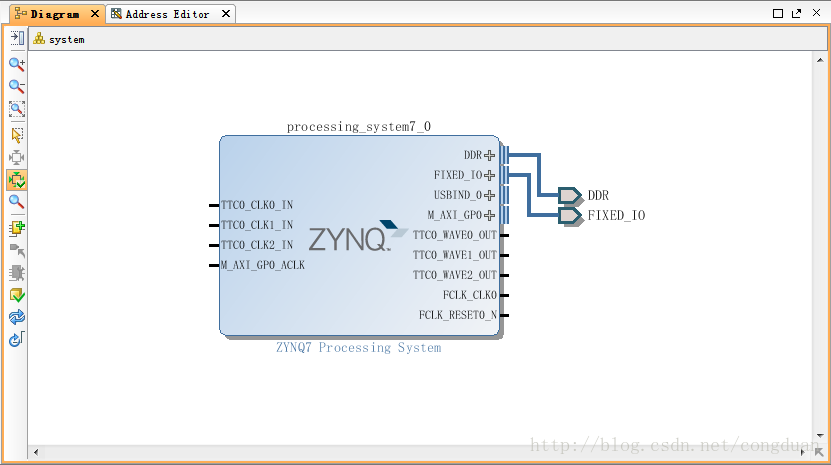

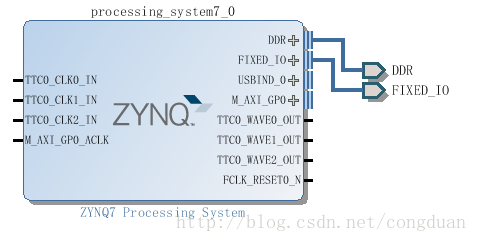

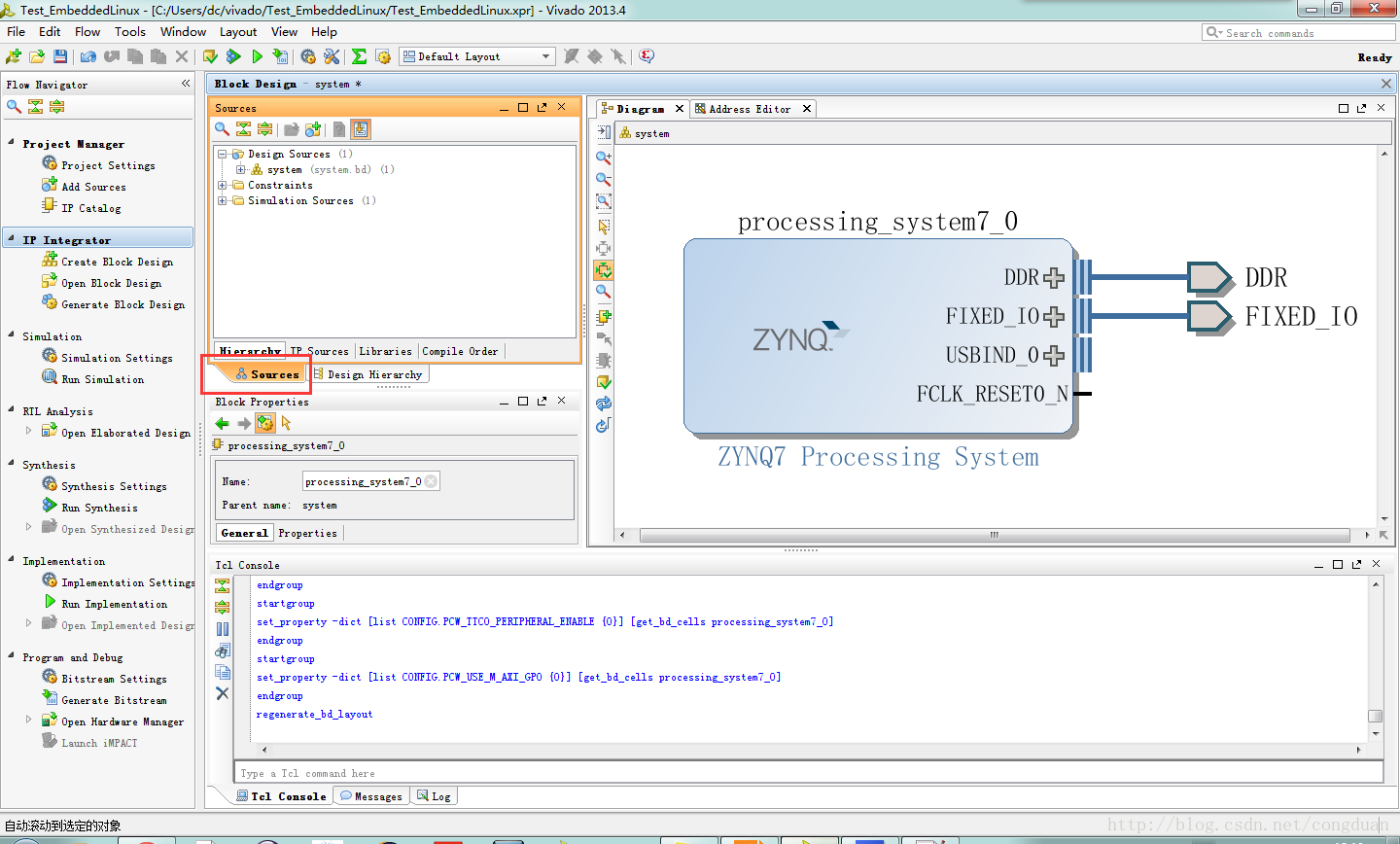

完成之后

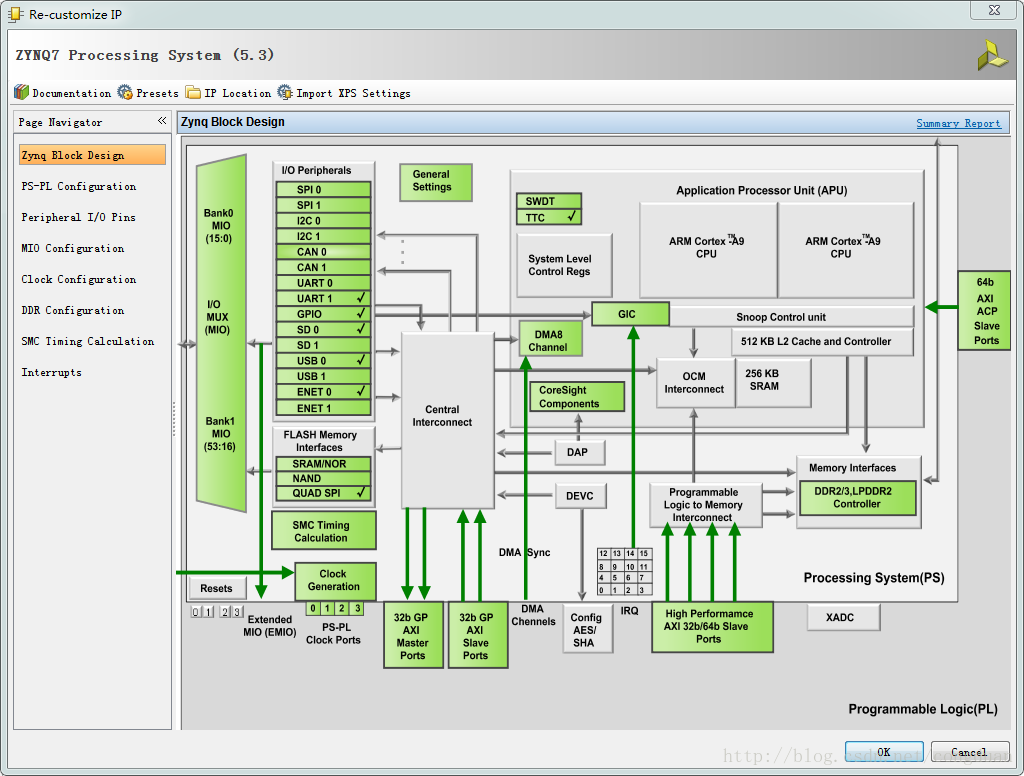

双击ZYNQ进行自定义配置

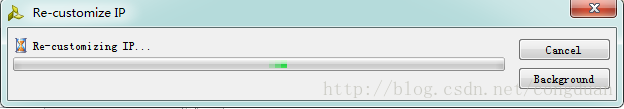

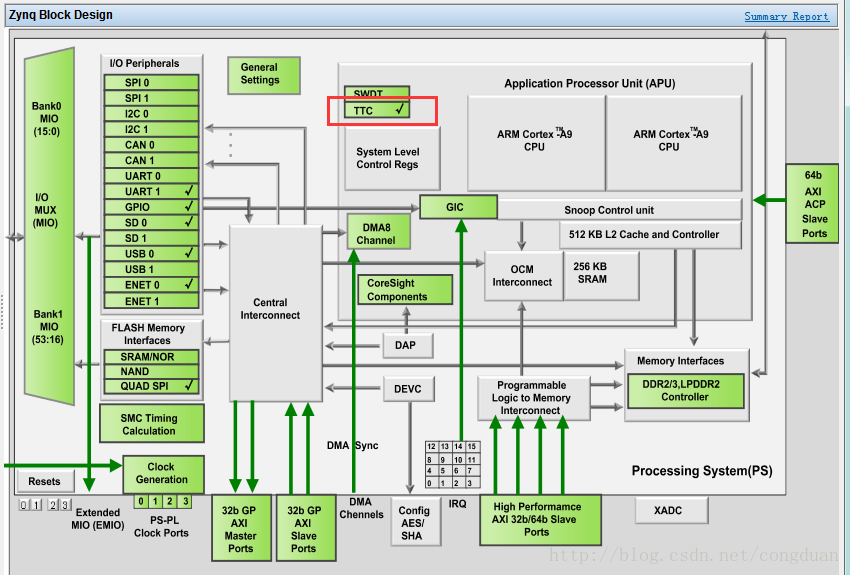

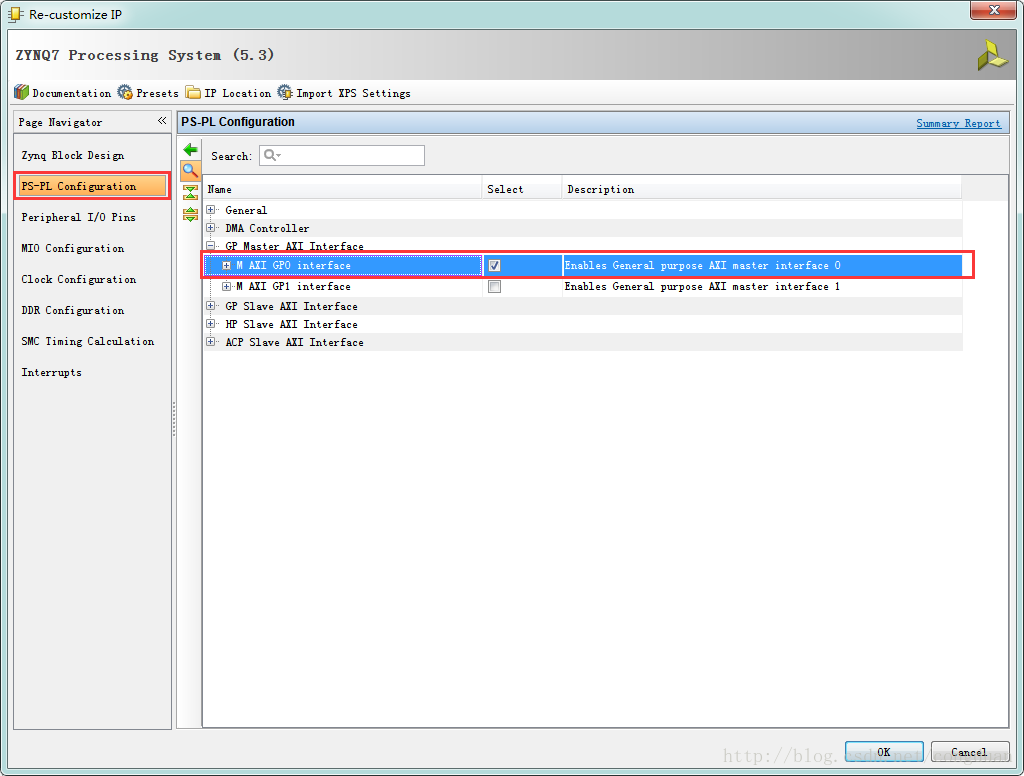

出现

取消不需要的部分

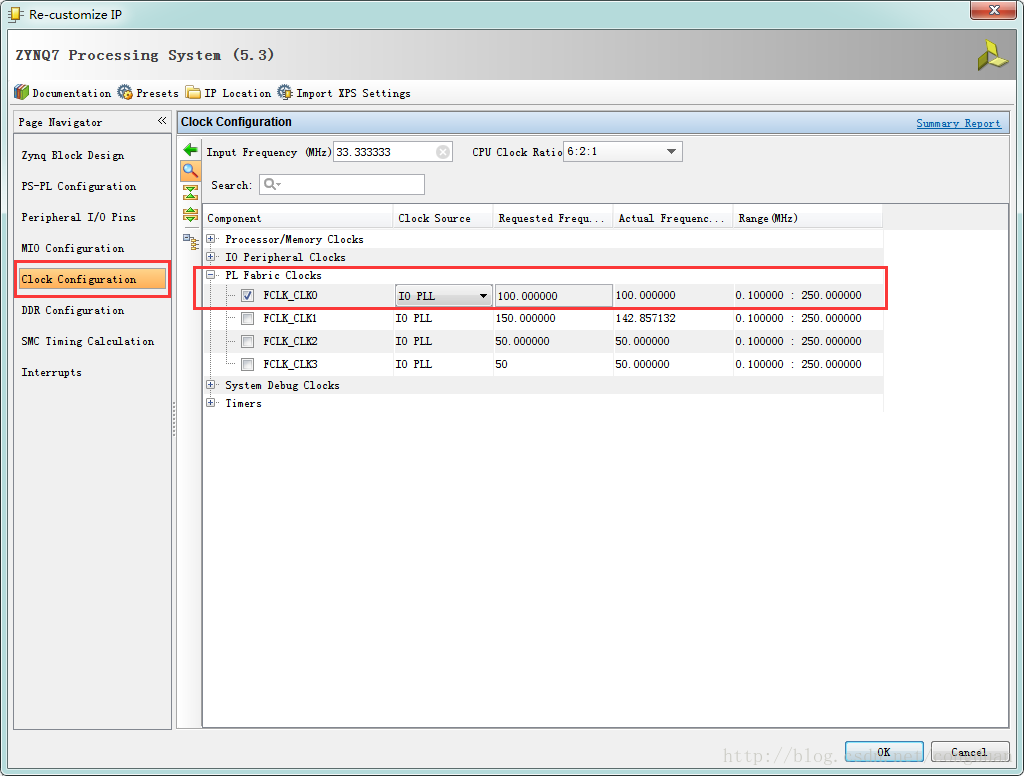

首先点击Clock Configuration,展开PL Fabric Clocks,取消FCLK_CLK0

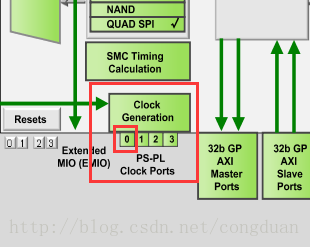

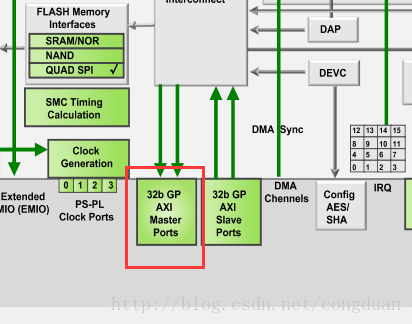

该时钟是PS提供给PL的时钟,在结构图中的如下部分

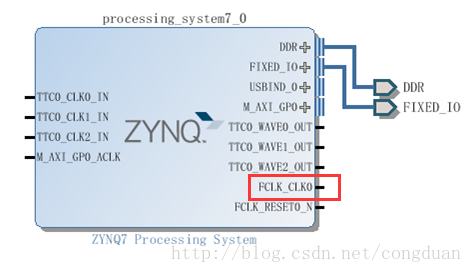

取消之后Diagram中的FCLK_CLK0会消失

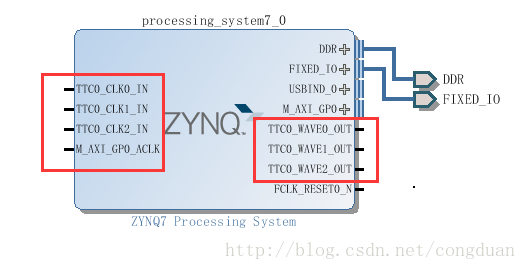

另外,我们要取消掉如下引脚

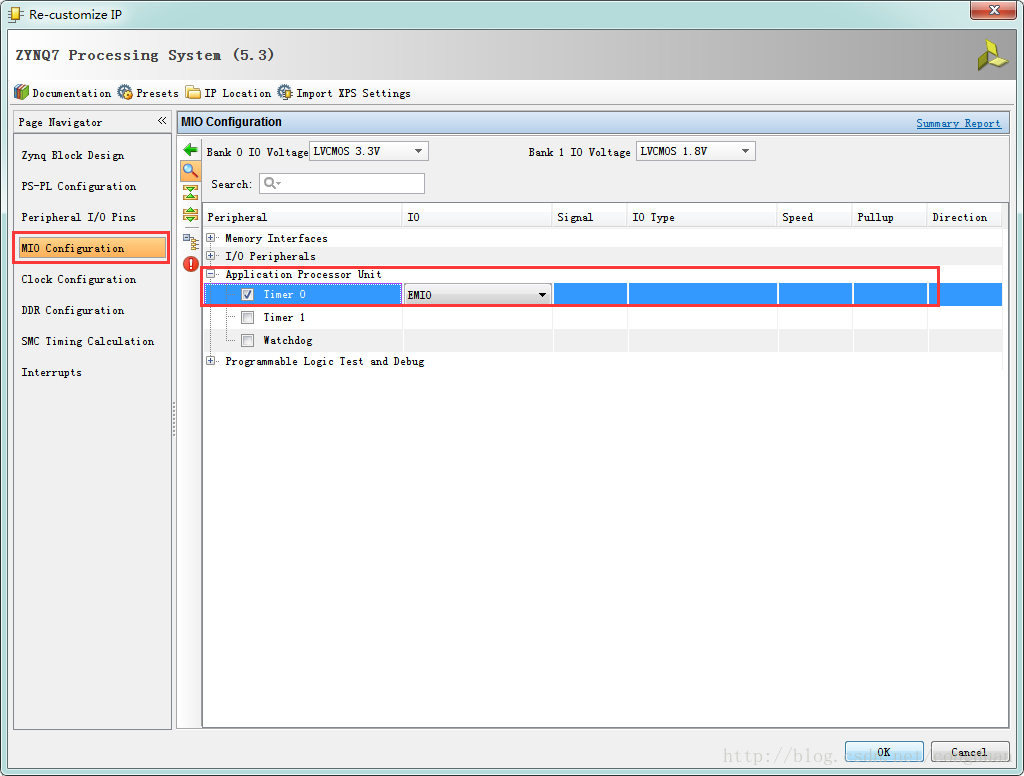

对于TTC,我们点击如下部分,取消掉TTC

再点击

取消掉AXI GP0 interface

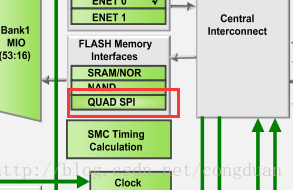

最后取消掉QSPI

点击OK完成

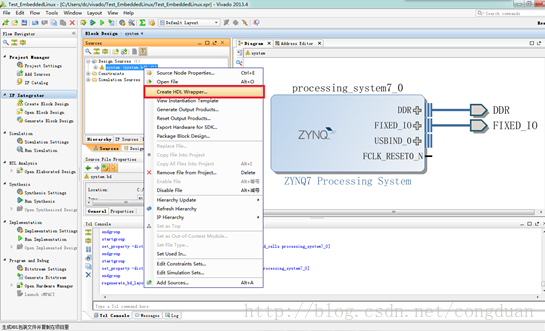

回到Block Design的sources视图

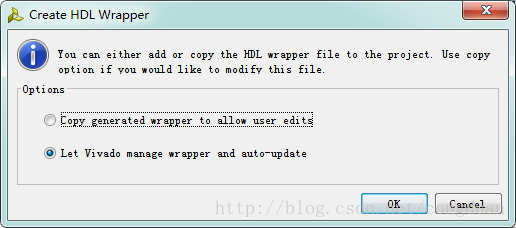

在System上右键选择Create HDL Wrapper

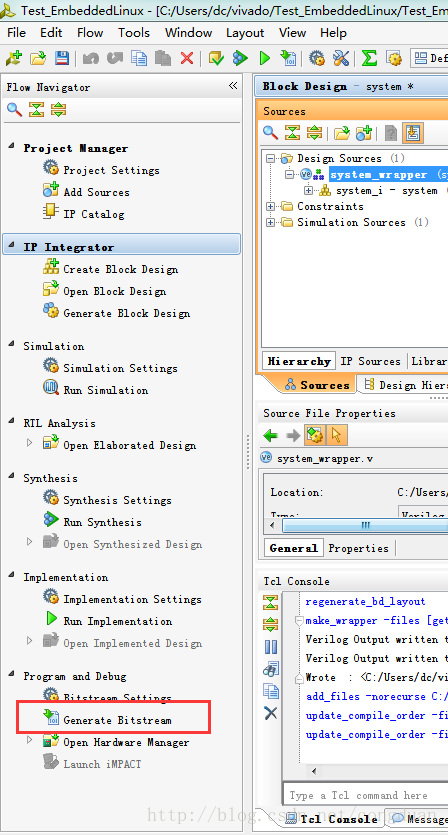

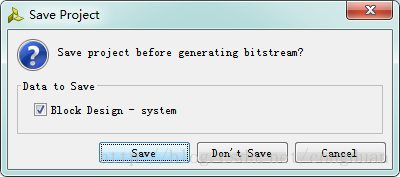

完成后点击左边Flow Navigator中的Generate BitStream

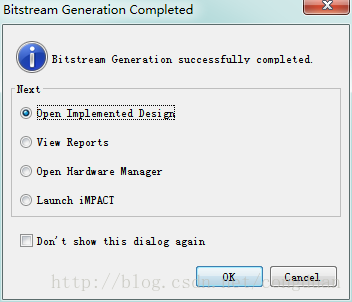

等待Vivado完成综合、实现、生成bitstream之后,出现如下

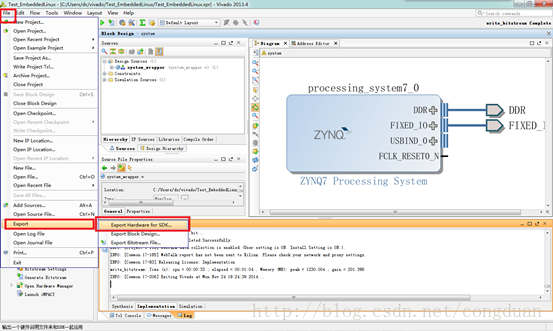

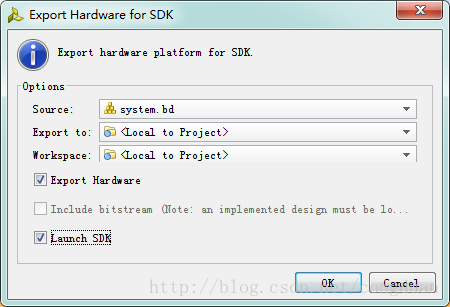

点击Cancel取消。点击File->Export->Export Hardware for SDK

勾选Launch SDK并点击OK。

到此,我们已经完成了所有的硬件配置。

1251

1251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?