今天在将SRIO的数据存入FIFO后,然后把FIFO中的数据不断送入FFT进行运算时,对于几个控制信号总产生问题。所以单独对FIFO进行了仿真。原来感觉FIFO的几个参数端口一目了然啊,还需要什么深入了解吗,在实验发生问题才知道当时的想法多么幼稚啊。

下面对xilixn FIFO核进行下简单说明,配上仿真时序图和源代码,描述的还是比较清晰的。希望对和我一样刚接触FPGA不久的同学能有一点点帮助^_^

这个仿真的功能是要实现向FIFO256存入1到256个数,再将1-256读出。注意这里选的是FULL FLAGS RESET VALUE OF 1

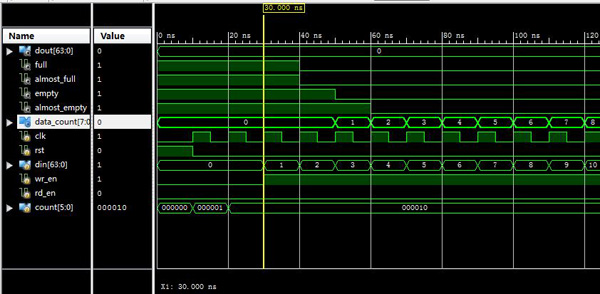

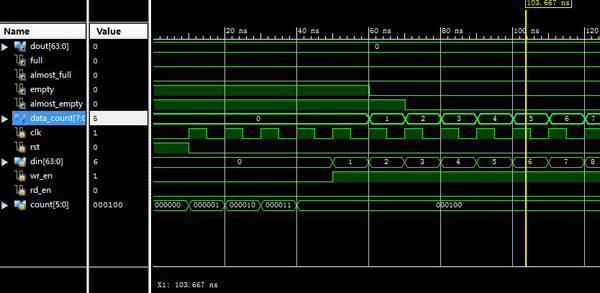

这是我想当然的仿真结果:这里可以看到数据1丢失了,第一个读出的数据是2。再看图1的data_count,这里先说下data_count的含义,当前时钟进行写操作,则下一时钟data_count加1,当前时钟进行读操作,则下一时钟data_count减1。因此由图隐约可以知道为什么数据1丢失了。

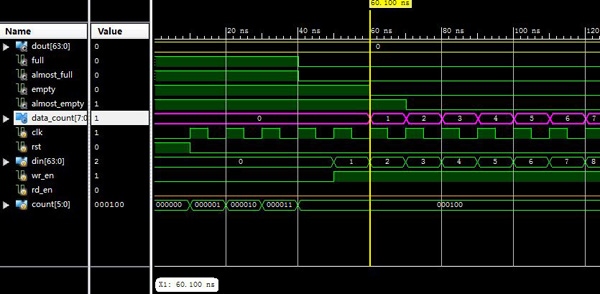

查看了下XILIXN FIFO的官方文档,说在进行写复位后,要延迟3个时钟周期才能进行写操作。因此我在写复位以后,通过count引入了3个时钟的延迟,如下图,发现数据没有发生的丢失的情况了。

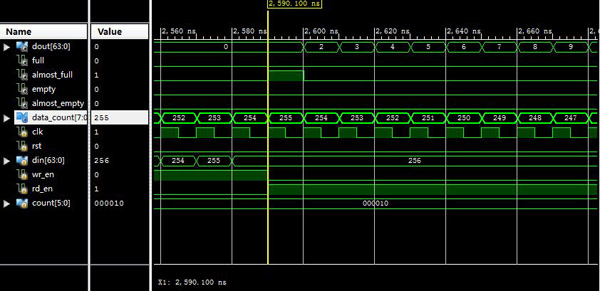

FIFO核非常好用,在读操作的时候,我们可以通过data_count来知道还有多少个数据将要读出,这对于后面的FFT参数控制很关键。当我加上FFT模块时,又出问题了,上面写复位的FULL高电平对信号的控制产生了的影响,即数据并没有传入FIFO,FULL就已经拉高了。重新回到FIFO文档,看到了答案FULL FLAGS RESET VALUE OF 0,在选了这个选项后,异步写复位将用最少的时间来完成。话不多说看仿真图一目了然。

来源:兔美酱的博客

696

696

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?