建模方式,三种

一、结构化建模

即对电路的结构描述来建模,故先要得到电路。在代码中实际就是对一些基本器件的调用,并用线网来连接各器件的描述方式。

二、数据流描述

对数据流在设计的具体行为的描述来建模,用assign语句把一个值赋给线网变量。

三、行为描述建模

对行为级的描述来建模,类似数据流建模,initial块语句和always块语句归为行为建模。

只有寄存器类型的变量才能在initial和always模块中进行赋值;

initial只能用于仿真,而always模块可以用于仿真和综合;

always模块是一上电反复运行,由敏感事件列表来触发;

在verilog中关键词都是小写,而且软件区分大小写

_(下划线)可以随意用在实数、整数中。它本身没有意义只是提高代码的易读性

寄存器类型的值可取负数,但若该变量用于表达式中,则按无符号数处理地。

如:reg A; A = -1; 则A二进制为111,运算中,A总按无符号数15来看待。

缺省状态的数据类型是线网型,输入输出端口可以被重新声明为reg类型。

无论是线网类型声明还是寄存器类型声,在声明中都必须与端口定义的长度相同。

例化就是在一个模块中引用另一下模块。

悬空端口处理 .null() //该管脚悬空

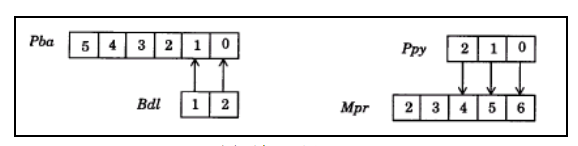

不同端口长度的处理(右对齐)

module Child (Pba, Ppy) ;

input [5:0] Pba;

output [2:0] Ppy;

. . .

endmodule

module Top;

wire [1:2] Bdl;

wire [2:6] Mpr;

Child C1 (Bdl, Mpr) ;

endmodule

verilog中有一点很重要:哪些是并发执行的,哪些是顺序执行的

always模块内是顺序执行的,如里面的语句,case,for......;always模块之间是并发执行的。

assign赋值语句、实例引用语和过程块(always模块、initial模块)之间都是并行执行

所以, 只有assign赋值语句和实例引用语句可以独立于过程块

if后记得加一个else,case中加上default以免生成锁存器

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?