- 拓扑结构约束

在设计安卓平板PCB时对地址线和控制线使用地址线拓扑约束进行设置,可以很好提高设计效率。

方法简要描述:

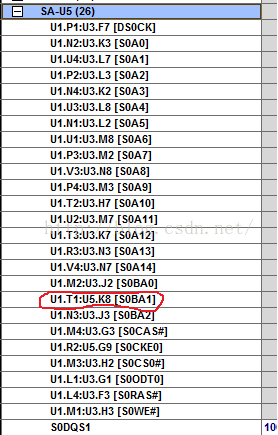

1.实用任意一根地址线,创建多个pin pairs对象;

2.将此地址线所有对象使用sigxplore进行提取,并且使用此模块中的CM对所有pin pairs对象进行相对延时约束。

在设置约束时可以将对象设置为globle或者net group,这个没有硬性要求。

3.将此约束更新到allegro中的CM即可;

4.将所有地址线和控制线设置为同一net group,然后使用以上提取出的ECset即可。

该方法使用的好可以明显提高设计效率,但是在使用过程中发线容易出现错误,如下图所示:

如上图红色圈中所示器件与其他都不同,这就说明在使用地址约束时出现了错误。

解决办法:在检查之后发现是提取的拓扑结构存在问题,在sigxplore中修改为实际布线所需要的拓扑结构后再使用可以很好的解决问题。

补充:一般地址线和控制线需要与时钟线进行长度约束,使用拓扑结构约束的match group需要把对应的时钟分叉pin pair对象加入作为target。

- physical和spaing针对特殊对象的组合使用

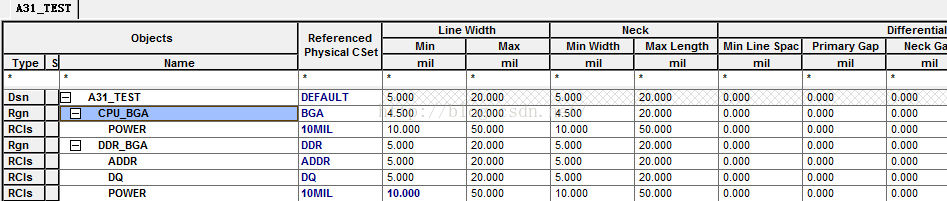

在BGA封装中电源线宽度要比一般信号线要宽一下,如信号线宽度为5mil,电源线宽度为15mil。如何在BGA一次性扇出时实现不同类型生成不同宽度?

如下操作可实现如上功能,即:

1.在网络列表中将所有电源设置到一个class对象中,注意不能设置为net group,否则不能加入到Region classs中;

2.在region对象中建立region class对象,region对象使用BGA约束对象,而region class使用电源规格的宽度约束。

如下图所示:

如上图所示,在CPU和DDR等Region对象中均将电源class单独进行约束,即使用10mil进行宽度约束。

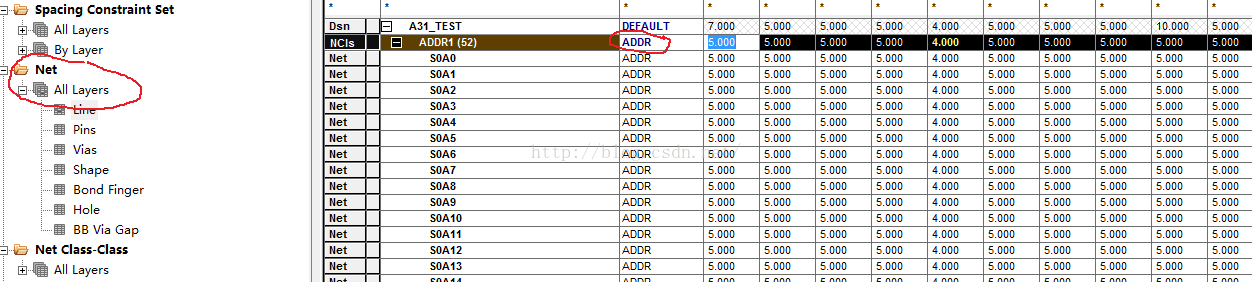

类似于physical中的一样,在对地址线进行布线时为了满足信号线有完整回流地平面,特别是在地址线过孔阵列中,如下图所示:

此时就需要将所有地址线和控制线设置到统一class中,单独进行shape to via的间距约束。此时最好不要将此约束设置到DDR的region中进行,因为地址线不仅仅在DDR区域大小中进行,采用的方法是在网络中直接对该net class进行约束即可,如下图所示:

在net功能区域,直接对ADDR1进行ADDR约束进行间距控制。

- 参考电压和时钟差分对布线特点

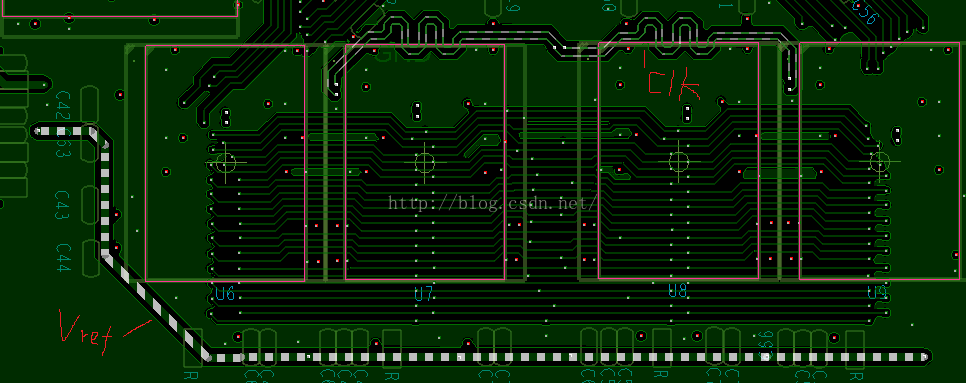

在4片DDR3的布线重难点就是地址线和控制线的设计,由于DDR区域空间是很宝贵的布线区域,所以关于时钟线和参考电源布线就显得非常重要。

在设计几款平板DDR3部分后,特总结如下:

1.时钟差分对最好放在地址线最上方,并且每个分叉点应该至少在每个DDR3引脚行数2行以上,即过孔至少比引脚行数高两行。这样的好处是在最后对时钟线进行多重匹配时,方便灵活调试。若夹在地址线中间则调整起来非常不方便。

2.参考电压Vref布线,应该放在地址线最底下,这样不会占用宝贵的DDR3空间区域。

由上图所示,在最后调整时钟线时存在很大的空间进行操作。

- 差分对绕蛇形线小技巧

在设计过程中要满足时钟差分对4根分叉线等长,由于要与地址线和DQS线匹配长度需要调整时钟差分对长度。

由于在设计之初已将时钟差分对的所有分叉线已调整为等长,在后续进行最后调整需要绕蛇形线满足一定长度要求,调整时一不小心就使得先前等长无效。为了避免这种问题出现,在绕蛇形线时选择绕中心线,这样在绕线时差分对是完全对称的,两线之间不会造成新的差值。

- 较小平面区域绕蛇形线小技巧

有时需要在小区域内满足较长的绕线,如上图可采用Trombone来进行绕行。在绕线时不采用中心线对称,GAP设为1Xspace,还有平行线的长度不要太长,这样容易产生串扰。

348

348

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?