2. ARM的程序即可以在FLASH里运行也可以在RAM里运行,不过能运行程序的FLASH只能使NorFlash,因为NANDFLASH的接口决定了其无法挂载在地址空间内。

3. 也就是说只要能挂载到ARM的程序地址空间的设备都可以直接放运行程序。否则其他存储设备只能存储程序或数据。如一般带LINUX或Wince的ARM板,一般会把主系统程序放在NorFlash或NANDFLASH中,上电后用Loader程序吧主系统程序加载到RAM或SDRAM的可执行地址去,然后跳到主程序去执行。

4. 计算机一般情况下系统存在硬盘里,系统启动时BIOS程序(在ROM里)先运行,然后从硬盘的系统分区里找到加载程序,加载到内存中(SDRAM),然后再由这段加载程序从磁盘中把系统加载进来。系统其实还可以存在光盘(所以可以从光盘启动)或网络计算机中(网吧里一般是这样)。大致就这个过程吧。具体的去网上查一下。

如果你有研究过单片机编程的分散加载机制,在编程中写过分散加载脚本。你问的第一个问题就解决了。

如果你有写过nand flash的驱动程序,你问的第二个问题就解决了。

STM32中的code可以不用拷贝到RAM中运行,也可拷贝到RAM中运行,这些不是技术问题,而是要看这段code

有没有加载到RAM中运行的必要。后面再解释。

nand flash不支持片上执行,不能在nand flash中执行程序,但nor flash支持。

但不能因此就断定STM32用的外置flash都是nor的。只要STM32带nand flash的控制器,就可以把nand中的code加载到RAM中运行。至于能不能用IO模拟nand 的接口协议,我没搞过不清楚。

首先,应该所有的单片机都是片内集成RAM和ROM(在加载域和运行域的角度看,Flash就是ROM)。

一般容量小的单片机,RAM和ROM都小,不会把flash中的代码加载到RAM中。

但有时确实需要加载,怎么办呢。就把code中比较关键的,调用很频繁的,对响应速度有要求的,就会加载到RAM中。

例如高频率中断的定时器中断ISR,就可以在分散加载脚本中修改这段code的运行域到RAM中。程序在刚上电后会在main函数之前加载这段code到RAM中。这样做的好处就是,这段code的执行速度快,我们知道ROM和RAM执行代码的速度比差距是很大的。RAM比ROM中执行速度快得多!

当然,如果你的RAM很大,你甚至可以把全部的Code加载到RAM中运行。

nand flash不是直接接到CPU的三总线上的,所以CPU不能直接从nand中取得可执行的指令,而是通过nand的控制器!

而nor是在总线上的,所以nor中的code可以直接执行。(nor的这个观点仅是我个人看法,仅供参考)。

再说外置RAM的问题,单片机在带SDRAM的控制器之后,就可以支持SDRAM了。

SDRAM在初始化好之后,SDRAM的使用方法和内置的SRAM没有差别。

如果你的单片机支持SDRAM和Nand flash,你可以把nand flash中的code加载到SDRAM中运行。

如果你知道怎么写分散加载脚本,这个功能分分钟就能实现。

对于x86的pc机和单片机等嵌入式开发系统程序的存储是截然相反的,

即:

x86的pc机cpu在运行的时候程序是存储在RAM中的,而单片机等嵌入式系统则是存于flash中

x86cpu和单片机读取程序的具体途径

pc机在运行程序的时候将程序从外存(硬盘)中,调入到RAM中运行,cpu从RAM中读取程序和数据

而单片机的程序则是固化在flash中,cpu运行时直接从flash中读取程序,从RAM中读取数据

造成这种差别的具体原因分析

x86构架的cpu是基于冯.诺依曼体系的,即数据和程序存储在一起,而且pc机的RAM资源相当丰富,从几十M到几百M甚至是几个G,客观上能够承受大量的程序数据。

单片机的构架大多是哈弗体系的,即程序和数据分开存储,而且单片的片内RAM资源是相当有限的,内部的RAM过大会带来成本的大幅度提高。

单片机的程序能存储在RAM中吗 ?

通过上面的分析可得知:单片机的程序能存储于flash中是基于两点考虑,即体系结构和RAM资源的多少。因此,在技术不但进步片内RAM容量不断增多的今天,RAM资源已经不再是制约这种差别的主要因素,而对于体系机构我们只要更改cpu读取程序的方式就可以。

将嵌入式系统的程序存于RAM中的具体做法

“对于很多的嵌入式系统,其代码很多都存储在nor flash中,运行也是直接在flash中运行.我最近了解到我新公司的软件中的一段代码当时为了提高运行速度被加载到ram中运行.当时他们是花了很多时间来解决这个问题的.

我仔细研究了一下链接脚本,用的是gnu的Linux的交叉工具链.地址分配是写在一个ld脚本中的.

他们是这样实现的:

1,将你需要在ram中运行的代码写在单独的一个c文件中,然后在脚本中设置其运行地址与存放地址分开.设置好必要的代码起始和结束的标志变量.

2,在代码中将存放地址处的代码拷贝到运行地址中.

这段代码倒是没什么问题,只是我有个更简单的办法:

还记得全局变量是怎么初始化的吗? .data段是一个自动初始化的段(内核代码处理),我只需要将这个c文件产生的代码放置在.data段中,这段代码就可以被加载到ram运行了.我测试了一下运行良好.

冯.诺依曼体系与哈佛体系的区别

二者的区别就是程序空间和数据空间是否是一体的。 早期的微处理器大多采用冯诺依曼结构,典型代表是Intel公司的X86微处理器。取指令和取操作数都在同一总线上,通过分时复用的方式进行的。缺点是在高速运行时,不能达到同时取指令和取操作数,从而形成了传输过程的瓶颈。

哈佛总线技术应用是以DSP和ARM为代表的。采用哈佛总线体系结构的芯片内部程序空间和数据空间是分开的,这就允许同时取指令和取操作数,从而大大提高了运算能力。

例如STM320LF240x系列DSP是增强型的哈佛结构通过三组并行的总线访问多个存储空间。它们分别是:程序地址总线(PAB),数据地址读总线(DRAB)和数据地址写总线(DWRB)。

stm32内部是nor flash,直接执行代码。

1. 冯诺依曼结构和哈佛结构

PC(x86)采用的是冯诺依曼结构,运行的时候即数据和程序都放在同一个存储器(ram)里,共用一条存储总线。具体 :当PC没电的时候,程序和数据存储在硬盘里,当pc上电的时候,在硬盘里运行的一段小程序把全部程序从硬盘搬运到ram中,然后程序开始在ram中运行;

而嵌入式系统(arm,dsp)采用的哈佛结构,运行的时候程序存储在flash中,数据存储在ram中,所以cpu从flash中取指令,到ram中取数据,指令总线和数据总线也是分开的;

2者之所以采用不同的结构,主要因为PC的ram空间足够,而嵌入式的ram太小;

以下以stm32来说明:

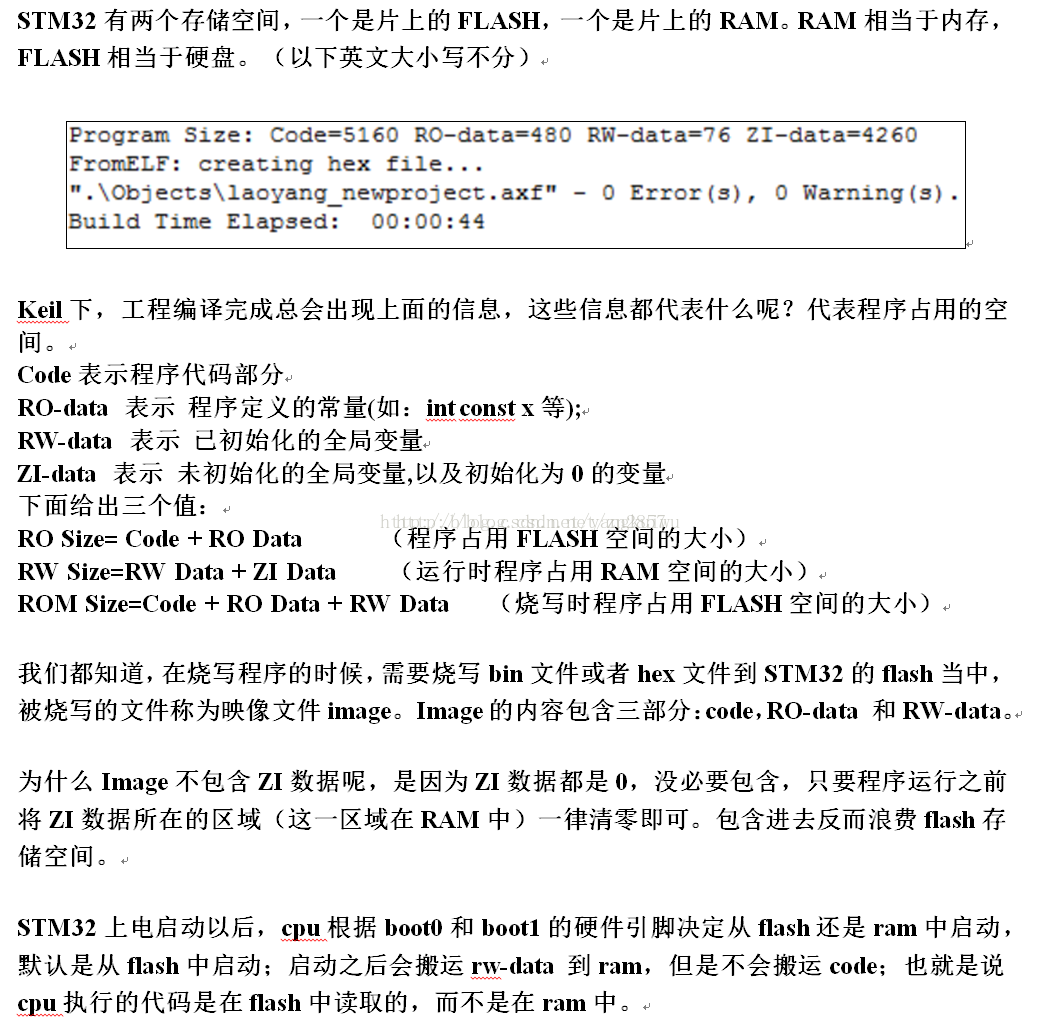

(1)cpu根据boot0和boot1的硬件引脚决定从flash还是ram中启动,默认是从flash中启动;启动之后会搬运rw-data 到ram,但是不会搬运code;

(2)如果采用ram中运行,一般只能用作调试模式,因为掉电程序就丢失了;

(3)从系统启动其实就是isp,是固化在rom中的一段代码;

参考: http://www.chinadmd.com/file/tr6xa3uo3osurvuett6iv6cx_1.html 3中启动方式的区别;

在ram中调试的设置方法;(主要是把ram的一段设置为rom来用,注意程序的大小要小于ram)

至于linux中从flash搬运到ram中之后,ram的link地址怎么从flash改变,每个函数的地址有时怎样在ram中寻址的,这是另外一个问题,需要学习和研究,

可以度娘 “stm32内存管理” 或者 “c语言内存分区”

http://blog.csdn.net/jj163zhuangzi/article/details/47088843

1886

1886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?