时钟芯片是一种集成电路,用于产生和控制电子产品的时钟信号。它是电子产品中的关键部件,用来确保各个组件和子系统之间的同步和顺序操作。

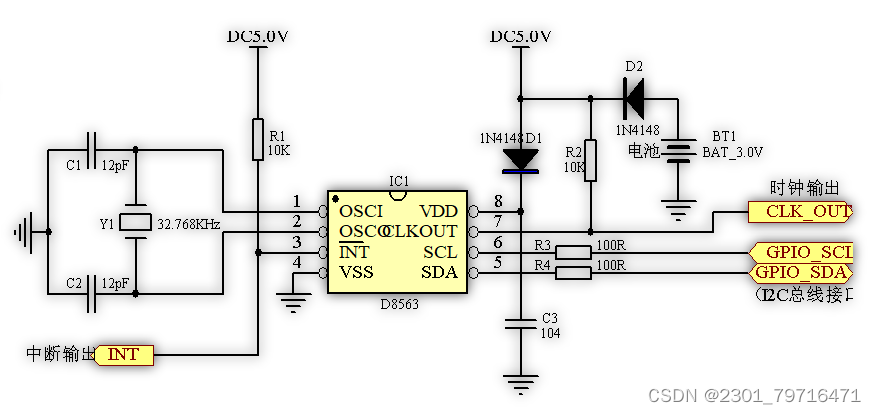

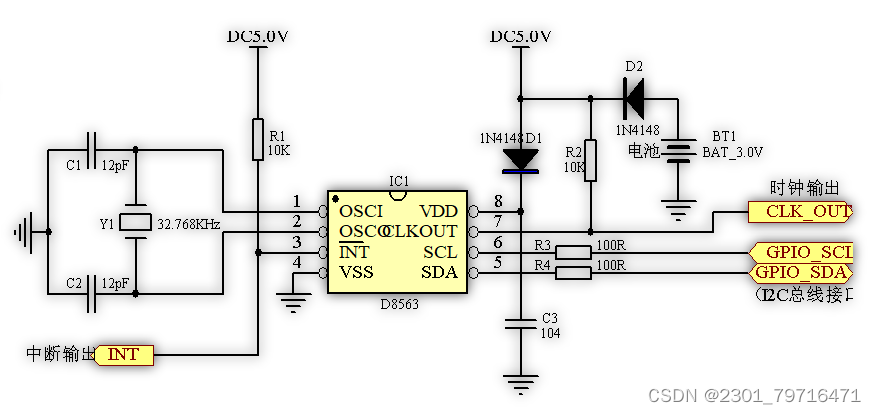

时钟芯片的原理是利用晶体振荡器产生稳定的频率信号,并通过分频和倍频电路来生成所需的时钟频率。晶体振荡器是一种利用晶体的机械振动产生电信号的装置,其频率非常稳定,通常在几十万到几千万赫兹之间。时钟芯片会通过对晶体振荡器的信号进行频率调整,使其满足特定的时钟频率要求。

时钟芯片是一种集成电路,用于产生和控制电子产品的时钟信号。它是电子产品中的关键部件,用来确保各个组件和子系统之间的同步和顺序操作。

时钟芯片的原理是利用晶体振荡器产生稳定的频率信号,并通过分频和倍频电路来生成所需的时钟频率。晶体振荡器是一种利用晶体的机械振动产生电信号的装置,其频率非常稳定,通常在几十万到几千万赫兹之间。时钟芯片会通过对晶体振荡器的信号进行频率调整,使其满足特定的时钟频率要求。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?