深知大多数程序员,想要提升技能,往往是自己摸索成长,但自己不成体系的自学效果低效又漫长,而且极易碰到天花板技术停滞不前!

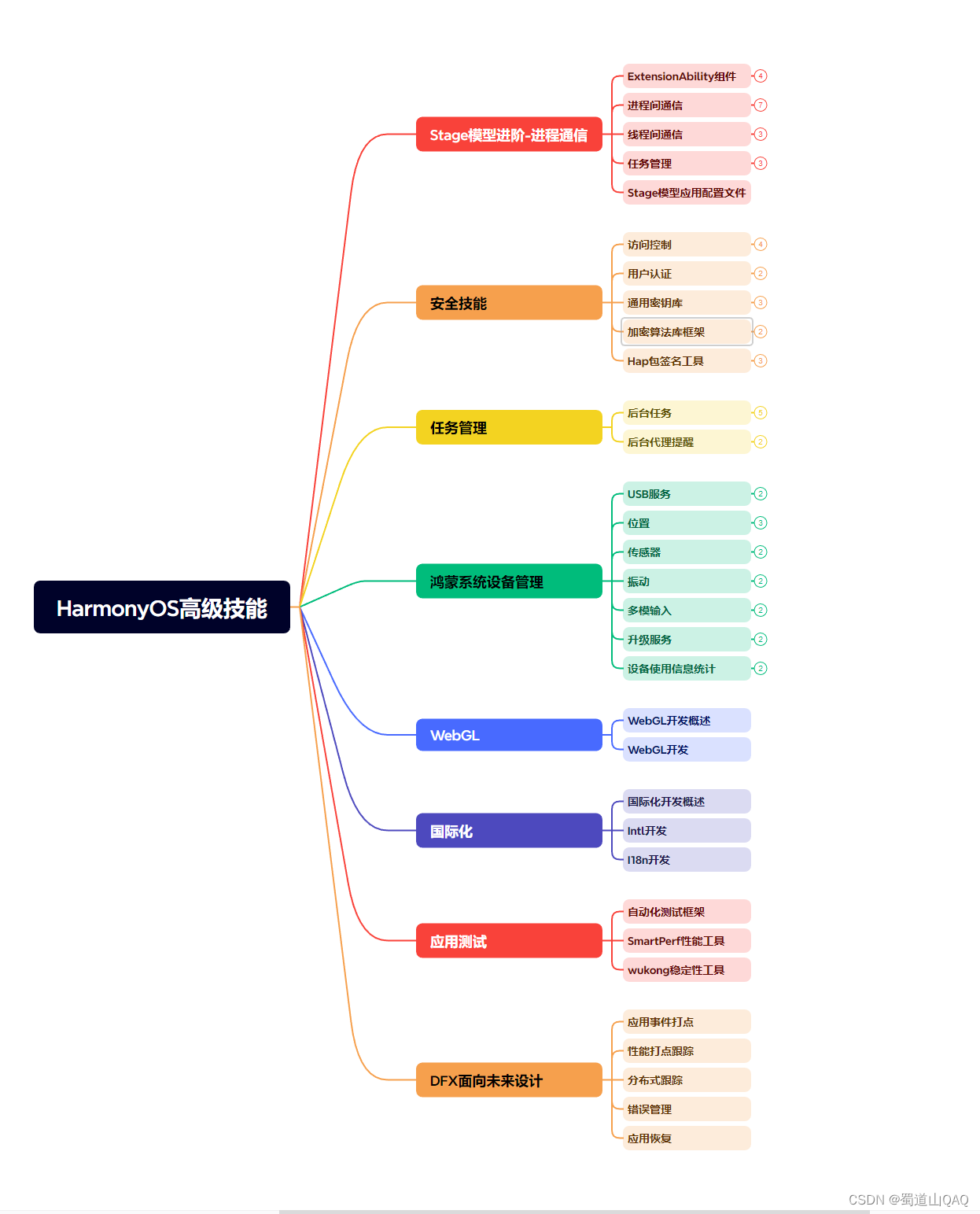

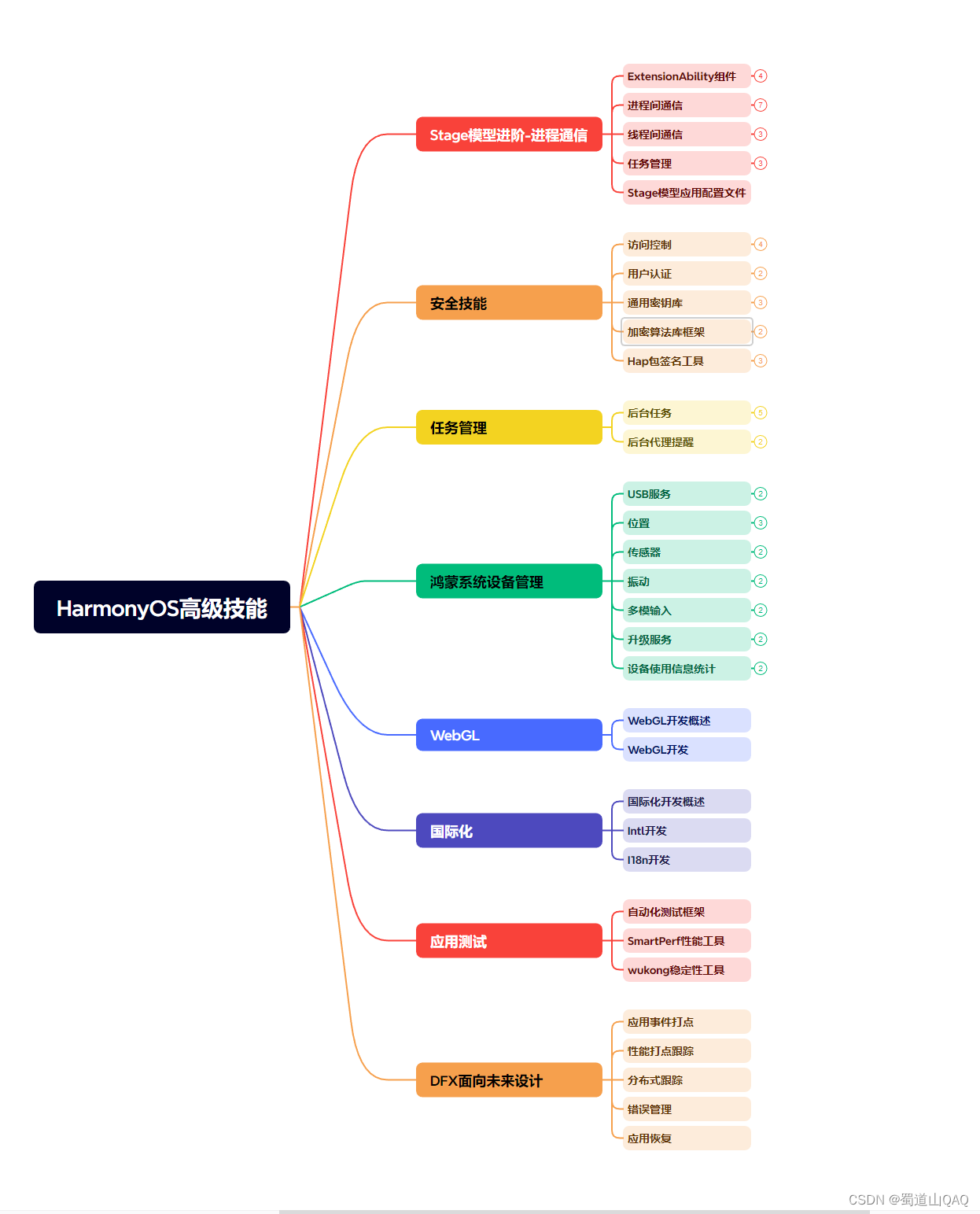

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上鸿蒙开发知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

二、解析

- 硬件层的并发优化基础知识

存储器的层次结构图如下:

各级缓存耗时对比:

采用分层缓存的层次结构会带来数据不一致问题,如下图:

那么如何保证数据的一致性,现代CPU处理办法有两种:

(1) 锁系统总线;

(2) 利用缓存一致性协议MESI(Intel处理器用的比较多,还有很多其他的缓存一致性协议),大致结构如下图:

- CPU的乱序执行

CPU中有个乱序执行的概念,概念图如下:

CPU在执行指令的时候,往往不是顺序执行,但是会遵守as-if-serial原则,也就是最终一致性原则。CPU为了提高指令执行效率,会在一条指令执行过程中(比如去内存读数据),去同时执行另一条指令,前提是这两条指令没有依赖关系。虽然指令执行顺序发生改变,但是不会影响单线程执行结果。多线程情况下为了不让CUP进行指令重排序,则需要用到Volatile关键字,因为Volatile的重要作用之一就是防止指令重排序。

CPU还会存在合并写的现象。当第一条指令往上级缓存写入数据时,由于上级缓存访问速度比较慢,可能第二条指令又对上一条指令的结果进行了修改,那么CPU将这两条指令合并的最终结果一次性的写入到缓存中,这就成为合并写。

深知大多数程序员,想要提升技能,往往是自己摸索成长,但自己不成体系的自学效果低效又漫长,而且极易碰到天花板技术停滞不前!

既有适合小白学习的零基础资料,也有适合3年以上经验的小伙伴深入学习提升的进阶课程,涵盖了95%以上鸿蒙开发知识点,真正体系化!

由于文件比较多,这里只是将部分目录截图出来,全套包含大厂面经、学习笔记、源码讲义、实战项目、大纲路线、讲解视频,并且后续会持续更新

,并且后续会持续更新**

4878

4878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?