修改S3C2440的时钟工作频率

之前写程序都没有设置过S3C2440的时钟,一上来就是设置寄存器和点灯,这和stm32的使用很不一样。在本文中将设置S3C2440的时钟频率,并用流水灯来看效果。设置的频率如下表。

| 时钟 | 频率 |

|---|---|

| FCLK | 400MHz |

| HCLK | 100MHz |

| PCLK | 50MHz |

时钟概览

打开S3C2440用户手册,查看第七章CLOCK & POWER MANAGEMENT。首先来看概览OVERVIEW的第二段:

The Clock control logic in S3C2440A can generate the required clock signals including FCLK for CPU, HCLK for the AHB bus peripherals, and PCLK for the APB bus peripherals. The S3C2440A has two Phase Locked Loops (PLLs): one for FCLK, CLK, and PCLK, and the other dedicated for USB block (48Mhz). The clock control logic can make slow clocks without PLL and connect/disconnect the clock to each peripheral lock by software, which will reduce the power consumption.

于是可以得到时钟用途表:

| 时钟 | 用途 |

|---|---|

| FCLK | CPU |

| HCLK | AHB |

| PCLK | APB |

S3C2440A拥有两个锁相环(PLL),MPLL用于产生上述三个时钟,UPLL用于产生USB时钟。PLL的原理不清楚,会用就行了。

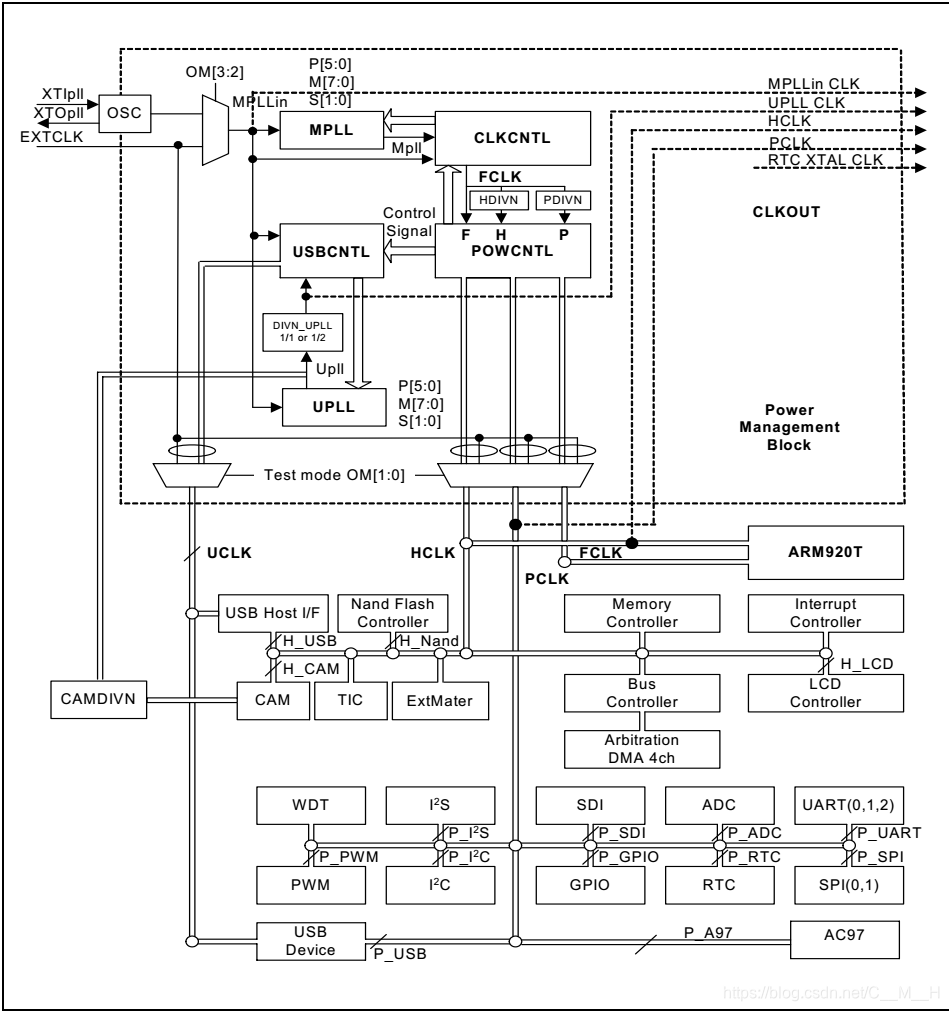

S3C2440A的时钟框图

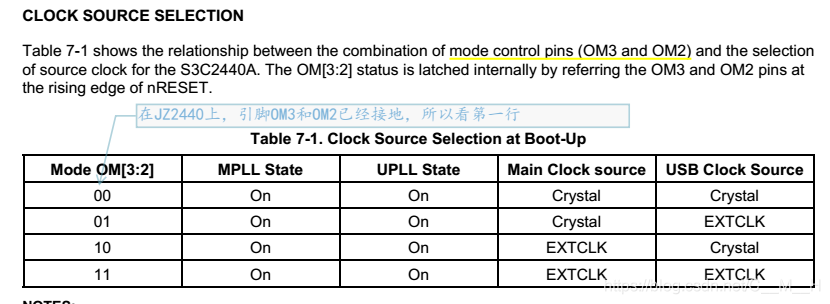

从左上角看起。时钟源有两个选择:OSC(晶振)和EXTCLK(外部时钟源)。通过OM[3:2]来选择。开始以为OM[3:2]是寄存器OM的两个位,但是在S3C2440手册中,寄存器一般以CON结尾。再翻看一下手册,发现上面有一段话,以及一个表格。

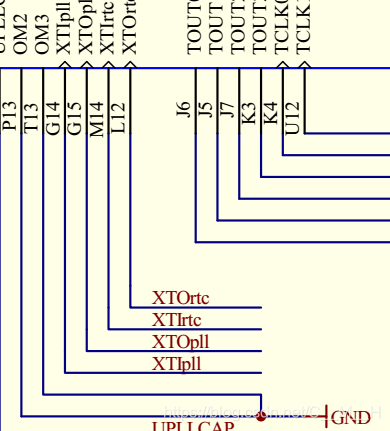

也就是说OM[3:2]其实是S3C2440A上的两个引脚。然后看到JZ2440原理图上对引脚的设置是这样的:

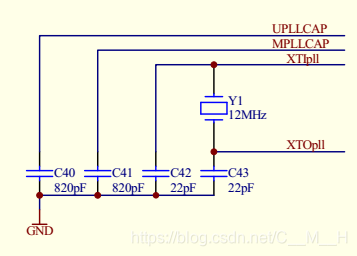

可以看到OM3与OM2引脚都接地,因此OM[3:2]=00B。因此看表格的第一行,选择的是晶振模式,即使用OSC作为时钟源,而OSC又来自XTlpll。然后来看看这个时钟源的频率是多少,在原理图上搜索XTIpll。

可以看到,晶振频率为12MHz。

继续看框图。经过OM[3:2]选择后,MPLL得到一个时钟频率,并且经过处理后输出一个时钟(FCLK),最后经过某个寄存器的配置,得到HCLK和PCLK。然后就可以为CPU、AHB和APB的工作提供时钟了。

现在可以清楚时钟的分配路线是

本文详细介绍了如何修改S3C2440微处理器的时钟工作频率,包括理解时钟框图、设置MPLL输出频率、配置分频器以及在代码中实现这些设置。通过调整时钟频率,实现了FCLK为400MHz,HCLK为100MHz,PCLK为50MHz,并讨论了在不同模式下CPU的工作状态和时钟源选择。

本文详细介绍了如何修改S3C2440微处理器的时钟工作频率,包括理解时钟框图、设置MPLL输出频率、配置分频器以及在代码中实现这些设置。通过调整时钟频率,实现了FCLK为400MHz,HCLK为100MHz,PCLK为50MHz,并讨论了在不同模式下CPU的工作状态和时钟源选择。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

919

919