I2S 是指“Inter-IC Sound”(集成电路间音频传输)。它是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种用于连接数字音频设备的串行总线接口标准。

1、I2S 时序

通常,I2S接口包括三条主要线路:数据线,帧时钟/字选择线(WS),和时钟线:

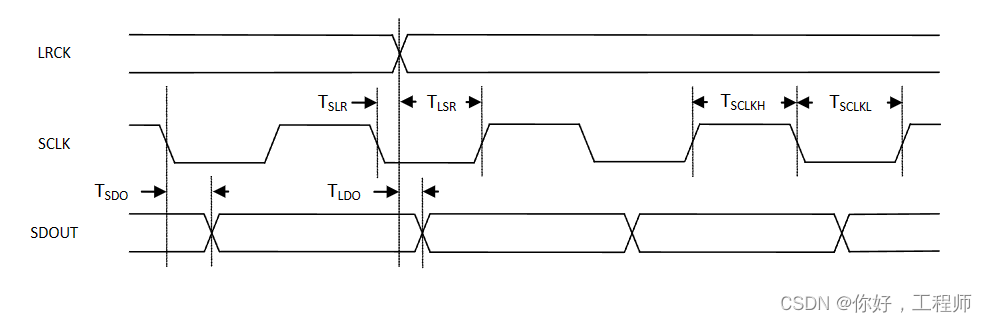

- 串行时钟 SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数。时钟信号的频率通常由系统时钟决定,并且必须与数据的采样率相匹配。

- 帧时钟 LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

- 串行数据 SDATA,就是用二进制补码表示的音频数据。数据的采样发生在时钟信号的上升沿或下降沿,具体取决于接口的配置和实现。

有时为了使系统间能够更好地同步,还需要另外传输一个信号MCLK,称为主时钟,也叫系统时钟(Sys Clock),是采样频率的256倍或384倍。

2、数据格式,根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐、I2S格式和右对齐:

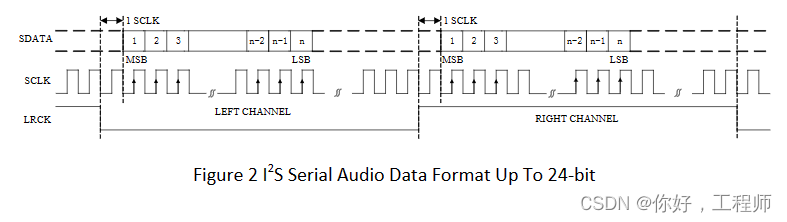

I2S格式:I2S格式的信号无论有多少位有效数据,数据的最高位总是出现在LRCK变化(也就是一帧开始)后的第2个SCLK脉冲处。

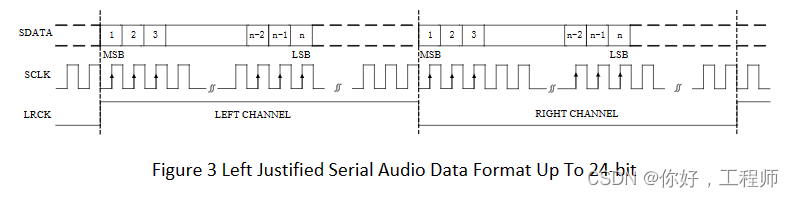

左对齐:音频数据的最高有效位(Most Significant Bit,MSB)始终位于数据帧的最左侧。在左对齐格式中,字选择线(Word Select Line)通常用于指示何时开始传输新的采样数据。当字选择线发生变化时,数据线上的数据也会相应地改变。左对齐格式的一个优势是它比其他格式更容易处理和解码,因为音频数据的开始位置始终固定在数据帧的开头。

博客介绍了I2S接口标准,它是飞利浦为数字音频设备制定的串行总线接口标准。阐述了I2S时序,包括串行时钟SCLK、帧时钟LRCK、串行数据SDATA等线路,还提到主时钟MCLK。同时介绍了数据格式,如I2S格式、左对齐格式等。

博客介绍了I2S接口标准,它是飞利浦为数字音频设备制定的串行总线接口标准。阐述了I2S时序,包括串行时钟SCLK、帧时钟LRCK、串行数据SDATA等线路,还提到主时钟MCLK。同时介绍了数据格式,如I2S格式、左对齐格式等。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?