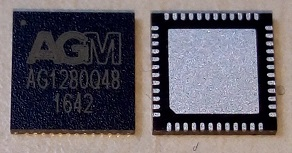

AG1280采用QFN-48 6x6和QFN-32 4x4 0.8mm(实际为0.77mm)封装,具有超低的成本和功耗。

该器件具有1280个LUT和最多40个用户IO,提供68Kbits的嵌入式Block RAM和10Kbits的分布式RAM,每个器件一个PLL提供时钟乘法和相移,以及通过JTAG接口的嵌入式FLASH配置,片内时钟发生器和宽输出频率范围。

该器件是即时接通,非易失性,多重可编程架构。器件 提供仿真的LVDS输出(LVDS_E_3R)。

AG1280的价格极具竞争力。

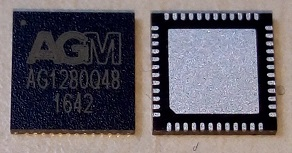

AG1280采用QFN-48 6x6和QFN-32 4x4 0.8mm(实际为0.77mm)封装,具有超低的成本和功耗。

该器件具有1280个LUT和最多40个用户IO,提供68Kbits的嵌入式Block RAM和10Kbits的分布式RAM,每个器件一个PLL提供时钟乘法和相移,以及通过JTAG接口的嵌入式FLASH配置,片内时钟发生器和宽输出频率范围。

该器件是即时接通,非易失性,多重可编程架构。器件 提供仿真的LVDS输出(LVDS_E_3R)。

AG1280的价格极具竞争力。

5494

5494

2103

2103

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?