Nand Flash与Nor Flash

起始

1988年,Intel于首先开发出NOR flash技术,一经推出很快蚕食掉EPROM和EEPROM的市场。因此可实现程序在片内执行。

1989年,东芝公司发表了NAND flash结构,强调降低每比特的成本,且容量可以很高。

所以:NAND闪存采用非常小的单元尺寸设计,可实现低位成本的存储数据,主要用作高密度数据存储介质,用于消费类设备,如数码相机和USB固态磁盘驱动器。

NOR Flash通常用于便携式电子设备(如手机和PDA)中的代码存储和直接执行。

而且:NOR和NAND闪存系统都是电可擦除解决方案,可以多次写入和擦除数据,但在关闭电源时不会丢失存储的数据。

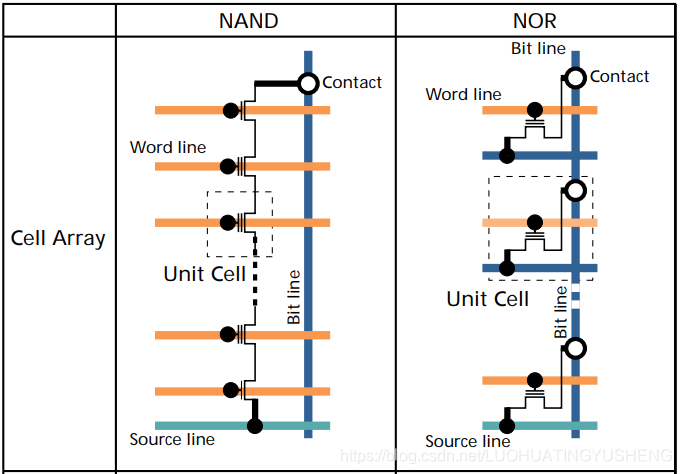

内部结构

在NOR Flash的内部电路配置中,各个存储器单元并联连接,这使得器件能够实现随机访问。

此配置可实现随机访问微处理器指令所需的短读取时间。

NOR Flash是低密度,高速读取应用的理想选择,这些应用大多是只读的,通常称为代码存储应用。

NAND闪存是作为高密度数据存储优化的替代方案而开发的,在权衡中放弃随机访问能力以实现更小的单元尺寸,从而转换为更小的芯片尺寸和更低的每比特成本。

这是通过创建一系列连接成串的八个存储晶体管来实现的。

NAND闪存系统利用NAND闪存架构的高存储密度和更小的单元尺寸,通过编程数据块实现更快的写入和擦除。

NAND闪存是低成本,高密度,高速编程/擦除应用的理想选择,通常被称为数据存储应用。

由于其本身两者结构差异以及半导体行业现有发展来看,对于任何给定的光刻工艺,NAND闪存阵列的密度将始终高于NOR闪存。理论上,对于相同的工艺技术和芯片尺寸,最高密度的NAND将至少是NOR密度的两倍。

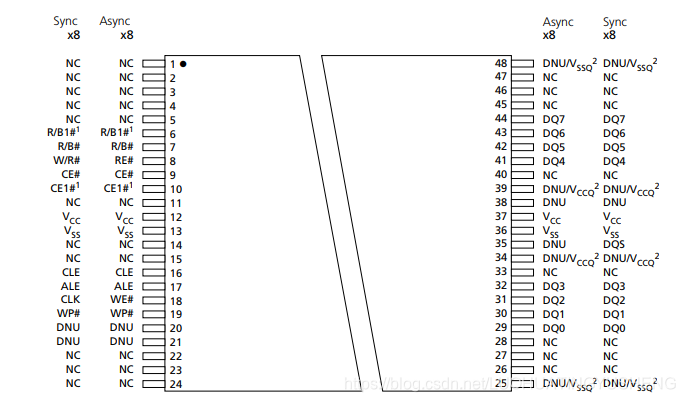

NAND 与 NOR Flash的封装引脚

NAND、NOR封装都包含TSOP封装与BGA封装,下面以TSOP48举例:

Nand Flash

特点:有同步与分同步之分;也有ONFI与TOGGLE之分,这些将在以后文章介绍。

注意NAND的数据和地址信号是公用的数据总线(一般是8条或者16条);其余为命令线以及控制线,具体如下:

ALE:地址锁存信号线;

CE#:片选线,低电平有效;

CLE:命令所存信号线;

DQX:数据输入输出;

RE#:读信号使能;

WE#:写信号使能;

WP#:写保护,保护数据;

R/B#:Read、Busy输出指示,OD门;

其余为电源和地引脚。

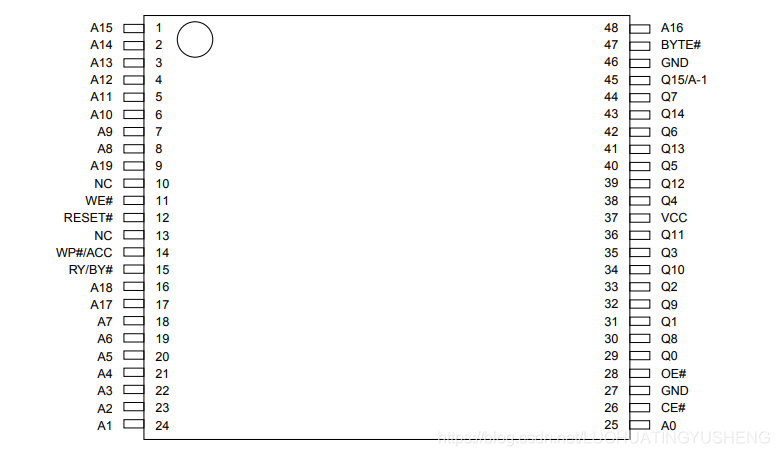

NOR Flash

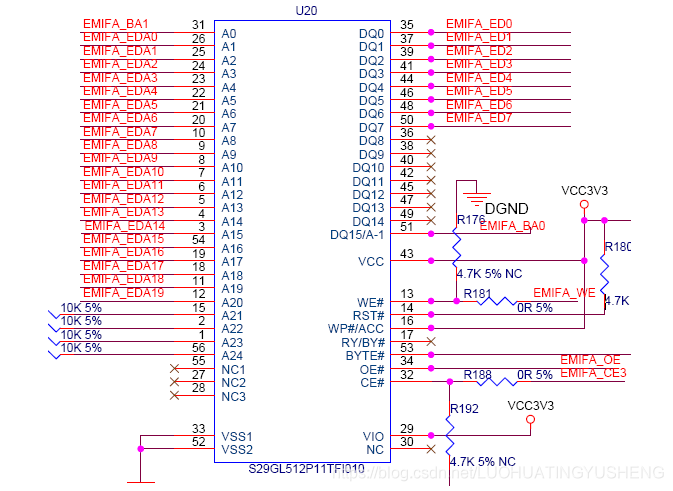

特点:无同步与异步之分,该器件的数据和地址分开,使用不同的总线传输,各司其职,所以数据传输速度比较快。具体引脚如下:

A[MAX:0]:地址传输线;

CE#:芯片片选;

OE#:输出使能;

WE#:写使能;

VPP/WP#:编程电压/写保护‘

BYTE#:位选择/字选择,8位或者16位总线选择;

RST#:复位信号;

DQx:数据信号总线;

RY/BY#:准备/繁忙指示信号,OD门;

其余为Vcc和GND。

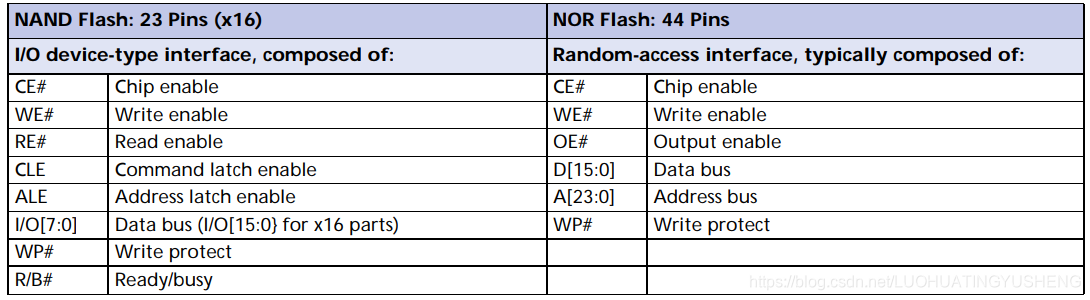

并列比较

区别/差异

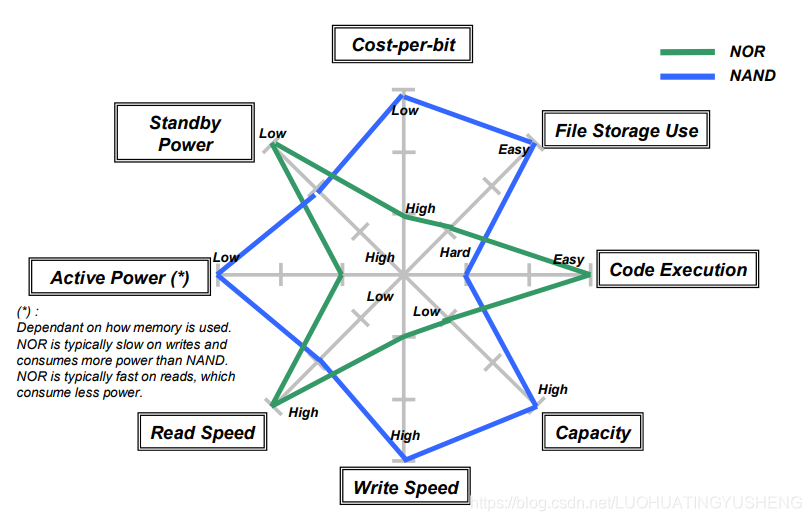

如上图,两者区别主要在于以下几点:

| 项目 | 待机功耗 | 每bit花费 | 文件存储 | 程序运行 | 容量 | 写速度 | 读取速度 | 工作功耗 |

|---|---|---|---|---|---|---|---|---|

| NAND | 大 | 低 | 适合 | 不行 | 大 | 快 | 慢 | 小 |

| NOR | 小 | 高 | 不适合 | 可以 | 小 | 慢 | 快 | 大 |

如何选取

NAND闪存的特点是:高密度,中读取速度,高写入速度,高擦除速度,以及间接或I / O类访问。

NOR闪存的特点是密度低,读取速度快,写入速度慢,擦除速度慢,以及随机访问接口。

对于需要从Flash引导的系统,从Flash执行代码,或者如果读取延迟是一个问题,NOR Flash可能就是答案。但是,对于存储应用,NAND Flash的更高密度以及高编程和擦除速度使其成为最佳选择。虽然高密度闪存器件的高编程速度的好处是显而易见的,但擦除性能同样重要,尽管不太明显。与磁存储系统驱动器(硬盘驱动器和磁带)不同,闪存需要一个单独的擦除步骤,以便在器件编程之前将所有位恢复为“1”状态。

功率是许多应用的另一个重要问题。对于任何写密集型应用,NAND闪存将消耗更少的功率。虽然NOR闪存和NAND闪存之间的瞬时功率(电压电流)数字似乎相当,但总能量将是NOR闪存显着更高,因为能量=功率*时间。

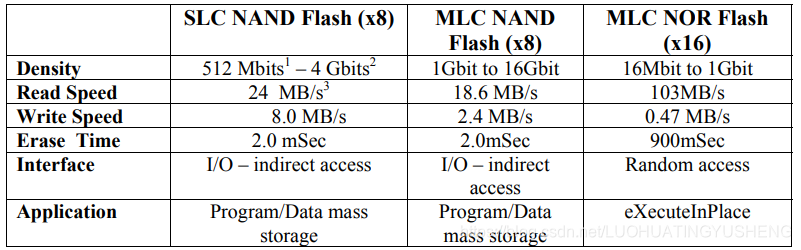

以下为关键参数对比:

所以,当系统 (如相机电话) 同时需要代码执行和大容量数据存储时, 设计人员可能需要考虑替代方案和权衡, 例如使用这两种类型的闪存, 可能与伪静态 RAM (PSRAM) 结合使用, 或将 NAND 与低功耗 DRAM 结合使用, 以便在其中运行操作代码。最好选择的闪存将是以最低的成本提供所需的性能和密度的闪存。

硬件电路设计

NAND Flash

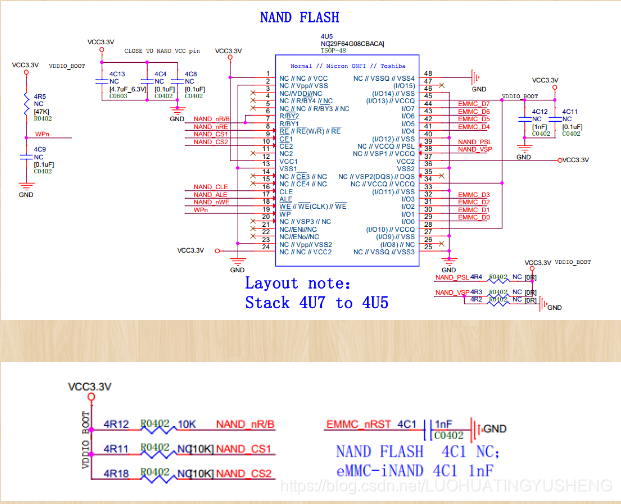

在NAND Flash器件处:

1、电源设计,器件包含两种电压,接口电压Vccq和内部存储器电压Vcc,请记住接口电压Vccq小于等于内部存储器电压Vcc。一般接口电压有3.3、1.8和1.2 V,但是常见的是3.3 V。电源引脚放置10 uF和100 nF电容用于滤波。

2、R/B引脚需要上接上拉电阻,因为该引脚为OD(漏极开路)门结构,用于指示空闲和繁忙状态。

3、CE片选引脚,该引脚为片选信号,上电时可以IO口控制,但是IO口可能是高、低、高阻,很难控制,所以我们要给一个确定的点平,高电平,不选中。(CE低电平有效)。

4、WP引脚,写保护引脚,该引脚也需要一个稳定的上电电平。所以该引脚我们上拉就是不写保护;下拉就是写保护状态。(WP低电平有效)。

5、Layout时,电源滤波电容靠近NAND Flash电源引脚放置。

6、将NAND Flash尽量靠近CPU放置,这样可以减小走线总线电容,提高信号完整性。

7、对于数据口,有些人建议走线要等常处理,但是实际上很多情况下都是非等长的处理,在我做的项目里影响不是很大,这个看产品类型以及厂商规范。

8、因为ONFO与TOGGLE规范有些差异,所以需要在设计时预留兼容两家设计的器件,我使用的主要是镁光的,所以还好,主要是东芝的不太一样。

在CPU NAND Flash接口处

1、在CPU侧的NAND Flash接口,一般都是eMMC与NAND接口共存通用的,因为eMMC等于控制器+Nand Flash;所以需要看清楚,确定那些信号指示什么,这个主要看控制器原厂的设计。

2、CPU支持的NAND Flash容量大小,块的数量,页的数量是有一定限制的,不可能无限大,就像手机可以安装的SD卡,有容量限制一样。所以在实际开发时需要注意。

3、某些CPU需要额外的配置,在上电时获取存储器的相关信息;比如:容量大小、块的数量、页的数量,这其实就是很常见的一种硬件识别软件做法,具体实现是外部IO口的电平状态来确定。

NOR Flash

NOR Flash的电路设计基本上与NAND Flash一致,仅仅是NOR的数据和地址分开了,不用每次需要传地址再传数据了。

SLC、MLC、TLC

SLC:

SLC = Single-Level Cell ,即1bit/cell,速度快寿命长,价格超贵(约MLC 3倍以上的价格),约10万次擦写寿命;

MLC:

MLC = Multi-Level Cell,即2bit/cell,速度一般寿命一般,价格一般,约3000—10000次擦写寿命。

TLC:

TLC = Trinary-Level Cell,即3bit/cell,也有Flash厂家叫8LC,速度慢寿命短,价格便宜,约500次擦写寿命,目前还没有厂家能做到1000次。

QLC

QLC是东芝最先实现商用的,但是目前信息很少,故不作详细介绍。

以上区分在固态硬盘SSD里面很常见,人们在选择时总会不好确定是选择那种的;其实上面已经很明确了,速度、寿命、容量、性价比时需要考虑的;但是SSD不仅取决于存储类型,也取决于接口控制芯片的性能,就像同样大的火车,火车头不行,那么大的货箱没用。最重要的是,电子产品的保修期很短,你能确定在保修期内上面的四种存储都会坏掉吗?显然是值得考量的。

1913

1913

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?