官方手册地址:https://china.xilinx.com/support/documentation/ip_documentation/axi_cdma/v4_1/pg034-axi-cdma.pdf

笔记主要是记录手册中比较有用的,具体详细的还是得去细看手册!!!

声明:所有文章属于个人在工作中所记下和搜集的笔记,不得转载

-

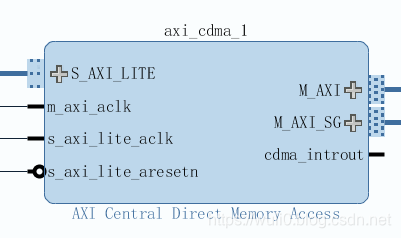

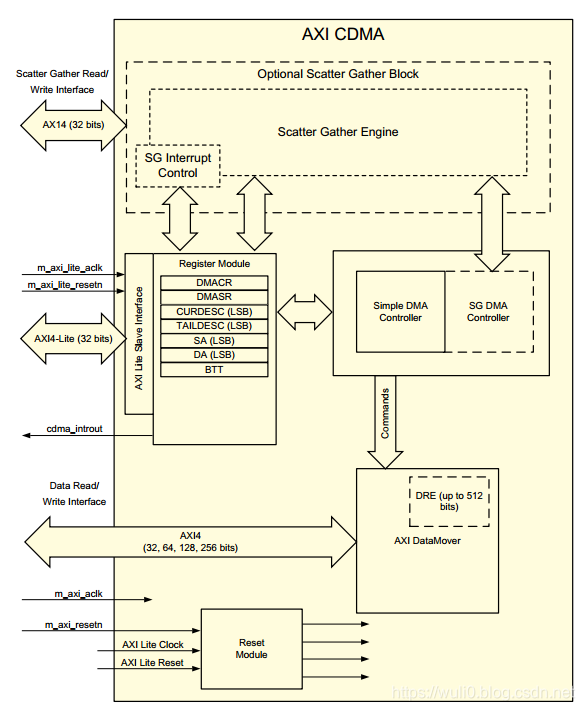

CDMA:Central Direct Memory Access,IP核内部框架如下:

从框架图可以看出:

S_AXI-Lite接口用来配置CDMA内部的寄存器,M_AXI接口用来搬运数据,M_AXI_SG接口一般与Bram连接,用来存储描述符。cdma_introut表示中断输出,一般用于DMA传输完成标志。

s_axi_lite_aclk时钟应该小于等于m_axi_aclk。

s_axi_lite_aresetn低电平复位,复位应该至少保持16个时钟周期内核才会对复位生效,且必须与s_axi_lite_aclk时钟同步。

-

寄存器地址采用小端模式,地址的[1:0]必须为0。地址空间偏移量与C_BASEADDR分配有关,寄存器配置通过S_AXI_LITE接口控制

重点关注的几个地址:

0x00:CDMA控制寄存器,bit[2]:复位bit位,bit[3]:SGMod,bit[6]:BD循环使能开关,bit[12]:DMA完成产生中断标志

0x04:CDMA状态寄存器,bit[1]:Idle,1表示Idle,0表示Not Idle

0x08:当前描述符指针,[31:6]R/W,[5:0]Reserved,SG模式下可用,CDMACR.IDLE = 1时写入,写入此字段的

描述符地址必须对齐到64字节边界(8个64bit),示例是0x00,0x40,0x80

0x10:末尾描述符指针,[31:6]R/W,[5:0]Reserved,SG模式下可用,CDMACR.IDLE = 1时写入,写入该寄存器会启动SG模式DMA传输

0x18:取数的源地址,[31:0]R/W,Simple模式下可用&#

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3507

3507

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?